1376

7 и 8 выборки по строкам матрицы, транзисторов 9 и 10 выборки по столбцам матрицы. Накопитель содержит также разрядные шины 11, v+д(где k - число столбцов матрицы), ключевые элементы на транзисторах i, , прямой 13 и инверсный 13j входы-выходы записи чтения, адресные входы 14,-14 столбцов матрицы, адресные входы 15,-15 р строк матрицы (где р - число строк матрицы), элементы под- заряда на транзисторах 16i-16i 4i, ши8

ну 6 питания и шину 17 нулевого потенциала. Надежность накопителя повышается за счет подключения ячеек 1 памяти соседних столбцов к общей разрядной шине и, таким образом, исключения паразитных связей. Потребляемая накопителем мощность в активных режимах записи и чтения снижена вследствие подключения к шинам 11 только одной выбранной ячейки 1 памяти и одного-транзистора 16. 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Порт чтения | 2018 |

|

RU2693331C1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах статического типа на МДП-транзис- торах. Целью изобретения является снижение потребляемой накопителем мощности. Накопитель содержит матрицу ячеек 1 памяти, каждая из которых выполнена из переключающих транзисторов 2 и 3, резисторов 4 и 5, транзисторов

1

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах статического типа на ЩЩ-тран- зисторах.

Цель изобретения ,- уменьшение потребляемой накопителем мощности и повышение надежности накопителя.

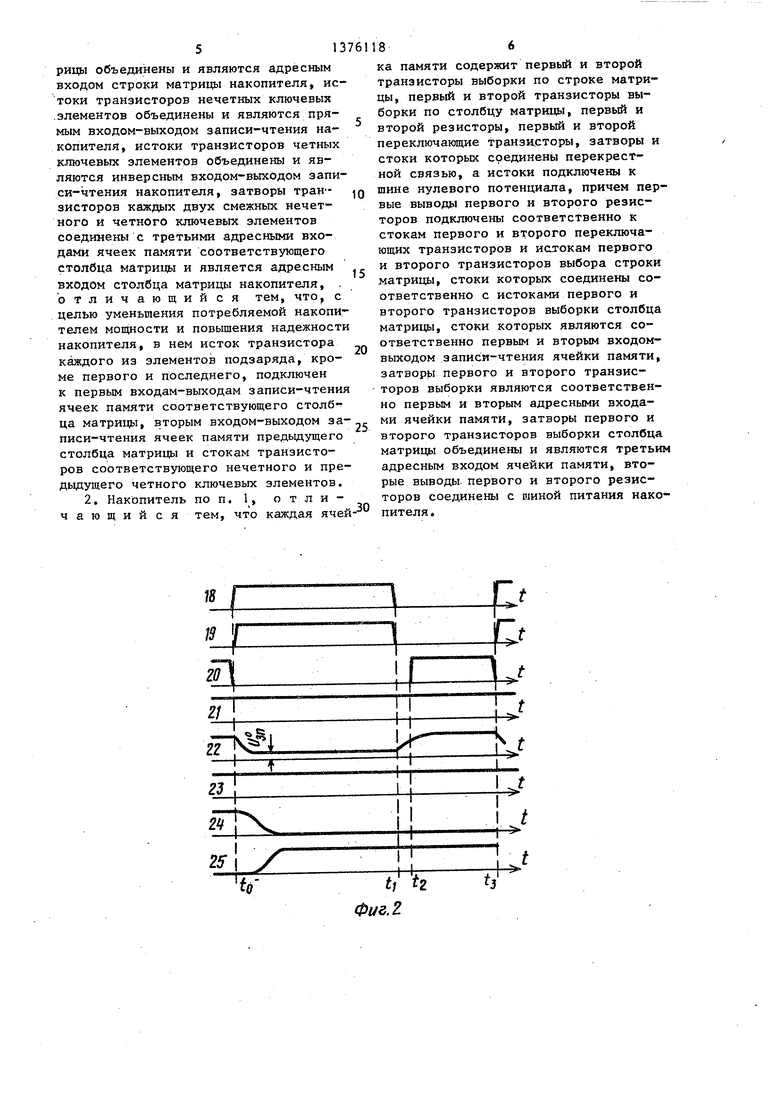

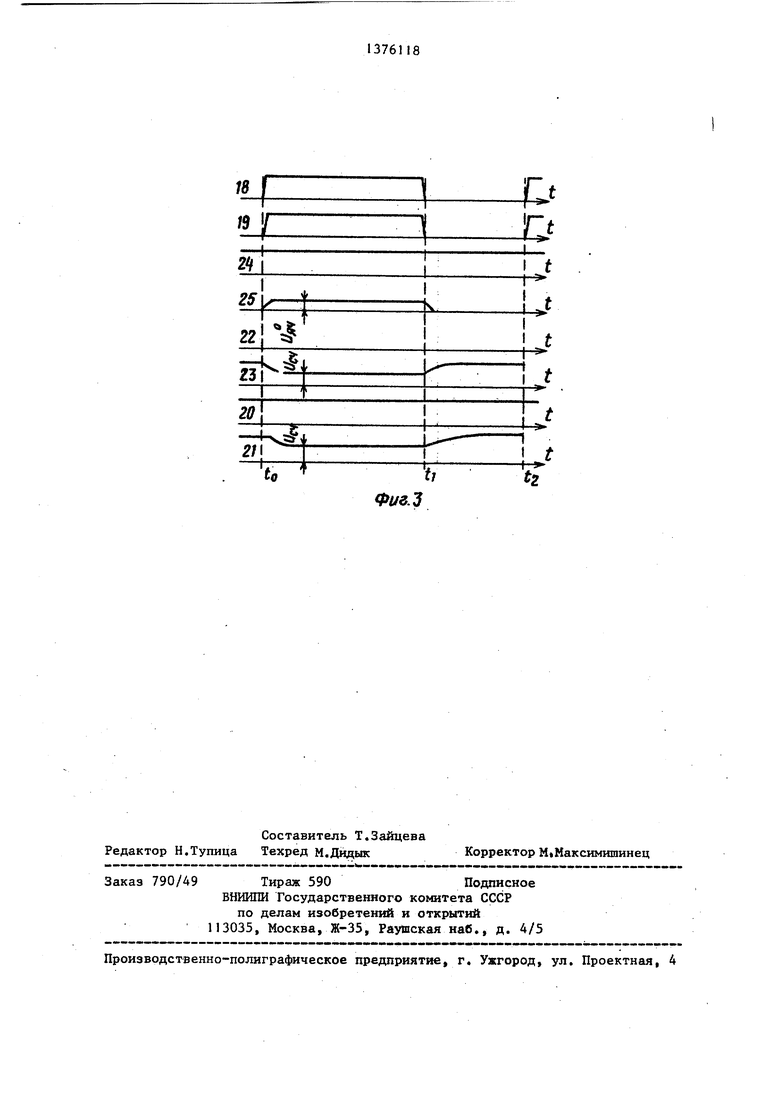

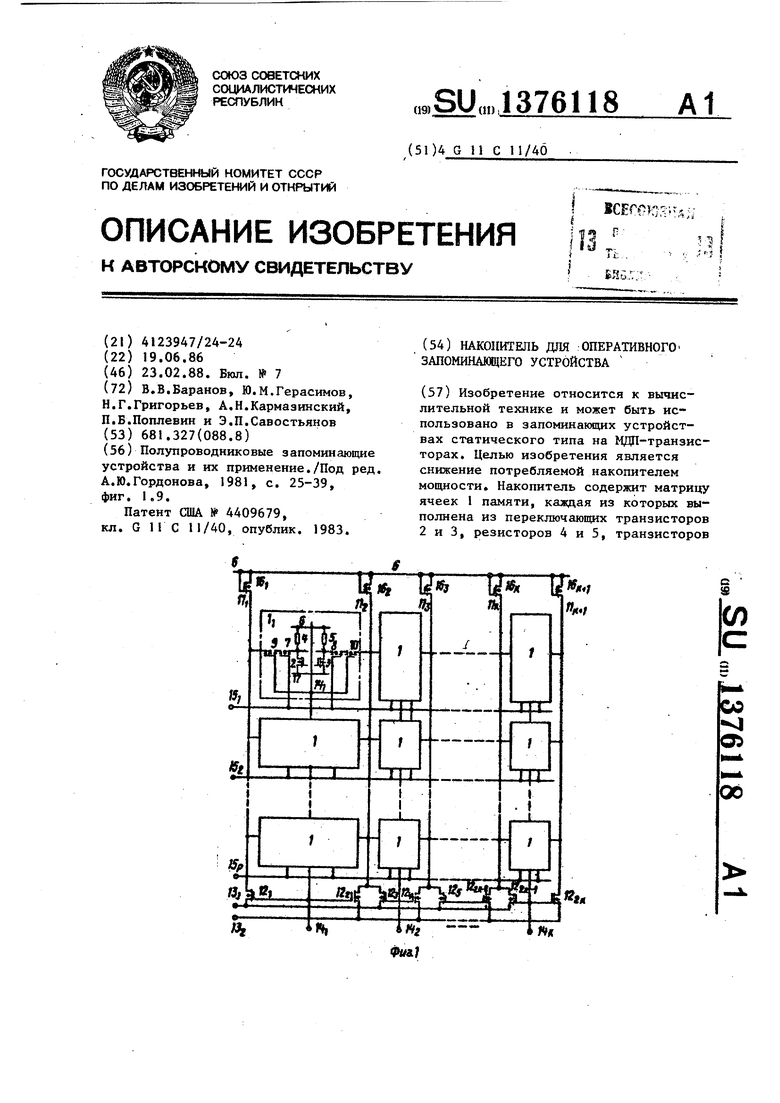

На фиг. 1 приведены структурная схема накопителя и принципиальная схема каждой ячейки памяти накопителя; на фиг. 2 и 3 - временные диаграммы, поясняющие работу накопителя.

Предлагаемый накопитель содержит (фиг. О матрицу ячеек 1 памяти, каждая из которых выполнена из первого 2 и второго 3 переключающих транзисторов, первого 4 и второго 5 резисторов, подключенных к шине 6 питания накопителя, первого 7 и второго 8 транзисторов выборки по сторонам матрицы, первого 9 и второго 10 транзисторов выборки по столбцам матрицы. Накопитель содержит также разрядные шины 111 -11 (,., (где k - число столбцов матрицы), ключевые элементы на транзисторах , прямой 13 и инверсный 13 входы - выходы записи-чтения, адресные входы столбцов матрицы, адресные входы 15i-15p строк матрицы (где р - число строк матрицы), элементы подзаряда на транзисторах 16,-16 ь,и шину 17 нулевого потенциала. На фиг. 2 и 3 обозначены напряжение 18 на выбранном входе 15, напряжение 19 на выбранном входе 14, напряжения 20

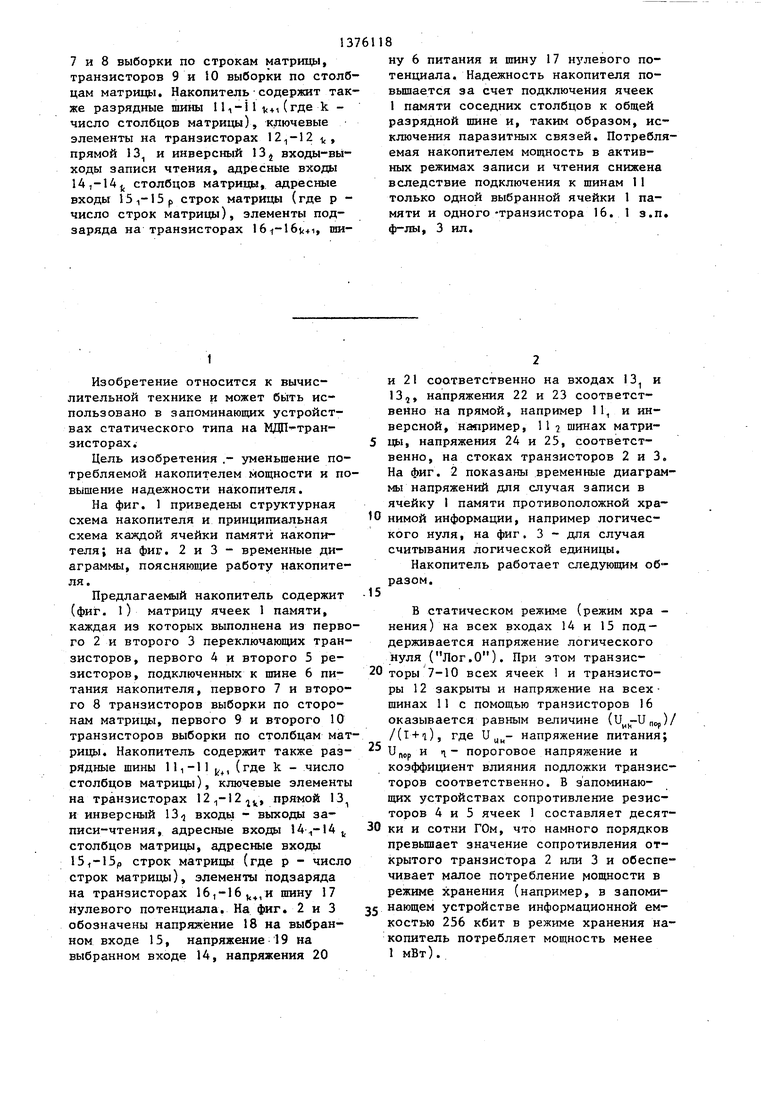

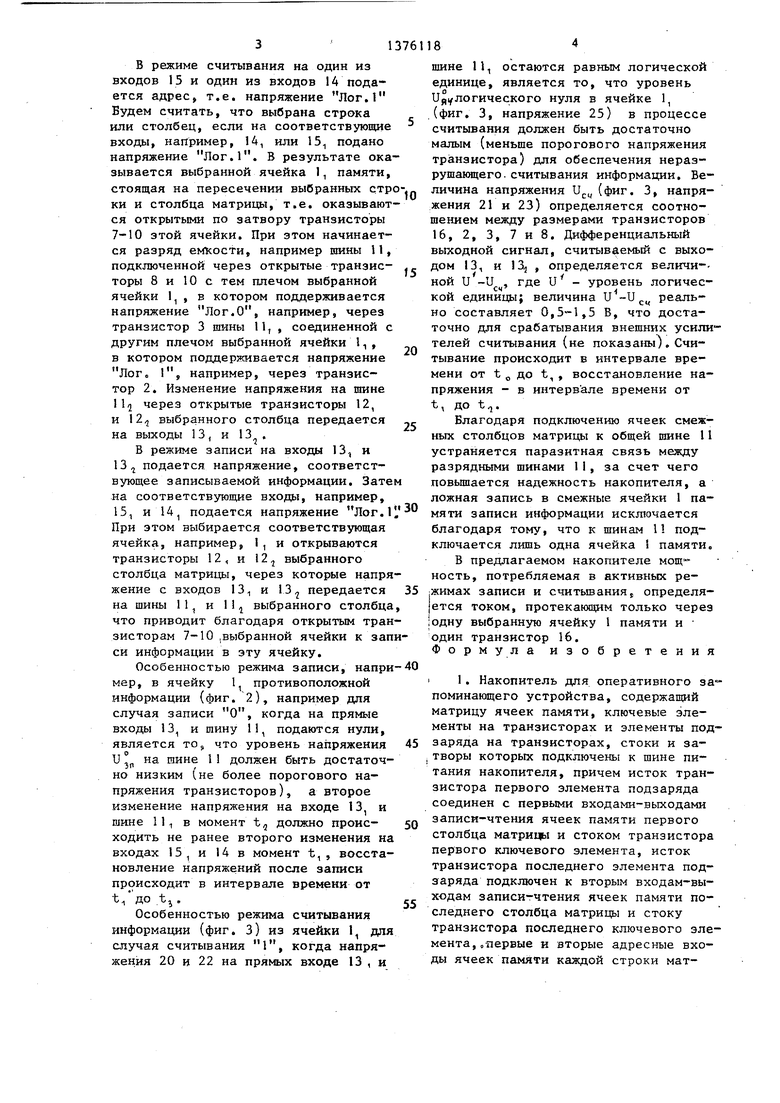

и 21 соответственно на входах 13 и 13,, напряжения 22 и 23 соответственно на прямой, например 11, и инверсной, например, П 7 шинах матри- 5 цы, напряжения 24 и 25, соответственно, на стоках транзисторов 2 и 3. На фиг. 2 показаны временные диаграммы напряжений для случая записи в ячейку I памяти противоположной хра- 0 нимой информации, например логического нуля, на фиг, 3 - для случая считывания логической единицы.

Накопитель работает cлeдyюш м образом. 5

В статическом режиме (режим хра - нения) на всех входах 14 и 15 под - держивается напряжение логического нуля (Лог.О). При этом транзис- 20 торы 7-10 всех ячеек 1 и транзисторы 12 закрыты и напряжение на всех - шинах 11 с помощью транзисторов 16 оказывается равным величине (U -Unop)/ /(l+l), где напряжение питания; пор и ч пороговое напряжение и коэффициент влияния подложки транзисторов соответственно. В запоминающих устройствах сопротивление резисторов 4 и 5 ячеек 1 составляет десят0 ки и сотни ГОм, что намного порядков превышает значение сопротивления открытого транзистора 2 или 3 и обеспечивает малое потребление мощности в режиме хранения (например, в запоми5 нающем устройстве информационной емкостью 256 кбит в режиме хранения накопитель потребляет мощность менее 1 мВт).

5 и,

В режиме считывания на один из входов 15 и один из входов I4 подается адрес, т.е. напряжение Лог.1 Будем считать, что выбрана строка или столбец, если на соответствуюние входы, например, 14, или 15, подано напряжение Лог.1. В результате оказывается выбранной ячейка 1, памяти, стоящая на пересечении выбранных стро ки и столбца матрицы, т.е. оказываются открытыми по затвору транзисторы 7-10 зтой ячейки. При этом начинается разряд емкости, например шины 11, подключенной через открытые транзис- торы 8 и 10 с тем плечом выбранной ячейки 1, , в котором поддерживается напряжение Лог.О, например, через транзистор 3 шины 11, , соединенной с другим плечом выбранной ячейки 1, , в котором поддерживается напряжение Лого 1, например, через транзистор 2. Изменение напряжения на вгане 1Ц через открытые транзисторы 12, и 12 выбранного столбца передается на выходы 13, и 13 .

В режиме записи на входы 13, и 13 подается напряжение, соответствующее, записываемой информации. Зате на соответствующие входы, например, 15, и 14, подается напряжение Лог.1 При этом выбирается соответствующая ячейка, например, I, и открываются транзисторы 12, и 12,; выбранного столбца матрицы, через которые напряжение с входов 13, и 13 передается на шины 11, и 1 выбранного столбца что приводит благодаря открытым транзисторам 7-10 .выбранной ячейки к зап си информации в эту ячейку.

Особенностью режима записи, напри мер, в ячейку 1, противоположной информации (фиг. 2), например для случая записи О, когда на прямые входы 13, и шину И, подаются нули, является то, что уровень напряжения и , на шине 11 должен быть достаточно низким (не более порогового напряжения транзисторов), а второе изменение напряжения на входе 13, и шине 11, в момент t,, должно проис- ходить не ранее второго изменения на входах 15, и 14 в момент t,, восстановление напряжений после записи происходит в интервале времени от t до t,

Особенностью режима считывания информации (фиг. 3) из ячейки Ц для случая считывания 1, когда напряжения 20 и 22 на прямых входе 13 , и

шине 1Ц остаются равным логической единице, является то, что уровень Uflifлогического нуля в ячейке 1, (фиг. 3, напряжение 25) в процессе считывания должен быть достаточно малым (меньше порогового напряжения транзистора) для обеспечения неразрушающего, считывания информации. Величина напряжения U. (фиг. 3, напряжения 21 и 23) определяется соотношением между размерами транзисторов 16, 2, 3, 7 и 8. Дифференциальный выходной сигнал, считываемый с выходом 13, и 13j , определяется величи-- ной и -U , где и - уровень логической единицы; величина реально составляет 0,5-1,5 В, что достаточно для срабатывания внешних усилителей считывания (не показаны) , Считывание происходит Б интервале времени от t о до t,, восстановление напряжения - в интервале времени от t, до t .

Благодаря подключению ячеек смежных столбцов матрицы к общей шине 11 устраняется паразитная связь между разрядными шинами 11, за счет чего повьш1ается надежность накопителя, а ложная запись в смежные ячейки 1 памяти записи информации исключается благодаря тому, что к шинам 11 подключается лишь одна ячейка 1 памяти.

В предлагаемом накопителе мощность, потребляемая в активных режимах записи и считьшания, определяется током, протекающим только через |одну выбранную ячейку 1 памяти и один транзистор 16. Форм у л а изобретения

I 1. Накопитель для оперативного за поминакяцего устройства, содержащий матрицу ячеек памяти, ключевые элементы на транзисторах и элементы под заряда на транзисторах, стоки и заi творы которых подключены к шине питания накопителя, причем исток транзистора первого элемента подзаряда соединен с первыми входами-вькодами записи-чтения ячеек памяти первого столбца матрицы и стоком транзистора первого ключевого элемента, исток транзистора последнего элемента под- заряда подключен к вторым входам-выходам записи-чтения ячеек памяти последнего столбца матрищ.1 и стоку транзистора последнего ключевого элемента, -первые и вторые адресные входы ячеек памяти каждой строки мат

513

ри1;ы объединены и являются адресным входом строки матрицы накопителя, истоки транзисторов нечетных ключевых .элементов объединены и являются прямым входом-выходом записи-чтения накопителя, истоки транзисторов четных ключевых элементов объединены и являются инверсным входом-выходом записи-чтения накопителя, затворы транзисторов каждых двух смежных нечетного и четного ключевых элементов соединены с третьими адресными входами ячеек памяти соответствующего столбца матрицы и является адресным входом столбца матрицы накопителя, отличающийся тем, что, с целью уменьшения потребляемой накопителем мощности и повышения надежности накопителя, в нем исток транзистора каждого из элементов подзаряда, кроме первого и последнего, подключен к первым входам-выходам записи-чтения ячеек памяти соответствующего столб- ца матрицы, вторым входом-выходом записи-чтения ячеек памяти предыдущего столбца матрицы и стокам транзисторов соответствующего нечетного и предыдущего четного ключевых элементов. 2, Накопитель по п. 1, отличающийся тем, что каждая ячей

0

61

5

0

186

ка памяти содержит первый и второй транзисторы выборки по строке матрицы, первый и второй транзисторы выборки по столбцу матрицы, первый и второй резисторы, первый и второй переключающие транзисторы, затворы и стоки которых соединены перекрестной связью, а истоки подключены к шине нулевого потенциала, причем первые выводы первого и второго резисторов подключены соответственно к стокам первого и второго переключающих транзисторов и истокам первого и второго транзисторов выбора строки матрицы, стоки которых соединены соответственно с истоками первого и второго транзисторов выборки столбца матрицы, стоки которых являются соответственно первым и вторым входом- выходом запис и-чтения ячейки памяти, затворы первого и второго транзисторов выборки являются соответственно первым и вторым адресными входами ячейки памяти, затворы первого и второго транзисторов выборки столбца матрицы объединены и являются третьим адресным входом ячейки памяти, вторые выводы первого и второго резисторов соединены с пшной питания накопителя .

Фие.З

| Полупроводниковые запоминающие устройства и их применение./Под ред | |||

| А.Ю.Гордонова, 1981, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4409679, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1988-02-23—Публикация

1986-06-19—Подача