(54) АССОЦИАТИВНАЯ ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная ячейка памяти | 1973 |

|

SU513393A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU924754A1 |

| Элемент ассоциативной памяти | 1980 |

|

SU875460A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

| Ассоциативный запоминающий элемент | 1980 |

|

SU928415A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| СПОСОБ ЗАПИСИ, СЧИТЫВАНИЯ И ПРЕОБРАЗОВАНИЯИНФОРМАЦИИ | 1970 |

|

SU283311A1 |

| Ассоциативная запоминающая матрица | 1985 |

|

SU1275546A1 |

Изобретение относится к области вычислительной техники, в частности к области ЗУ, и может быть использовано при построении ассоциативной памяти.

Известна ассоциативная ячейка памяти содержащая триггер и элементы управления записью-считыванием.

Недостатком известной ячейки .является малое быстродействие, обусловленное многотактным првдышп9м работы при сложном ассоциативном поиске,1йГ значительная сложность функциональной схемы..

Целью изобретения является упрощение ассоциативной ячейки памяти и повышение ее быстродействия.

Поставленная цель достигается тем, что ассоциативная ячейка памяти содержит логический элемент ИЛИ, логический элемент И и два передающих вентиля. Входы логического элемента ИЛИ подкл1очены к прямому выходу триггера и к |аз- рядной шине нуля, а выход;-к одному иа входов логического элемента И, второй вход которого подд лючен к логическому входу .ячейки, а выход к логическому

; выходу ячейки.: Передающие вентили сое-

; динёны последовательно и включень между разрядной йиной нуля и адресной ,щи«

, ной. Управляющие входь передающих вен-

5 I тилей подключены к прямому выходу триг

i гера и к. логическому входу ячейки.

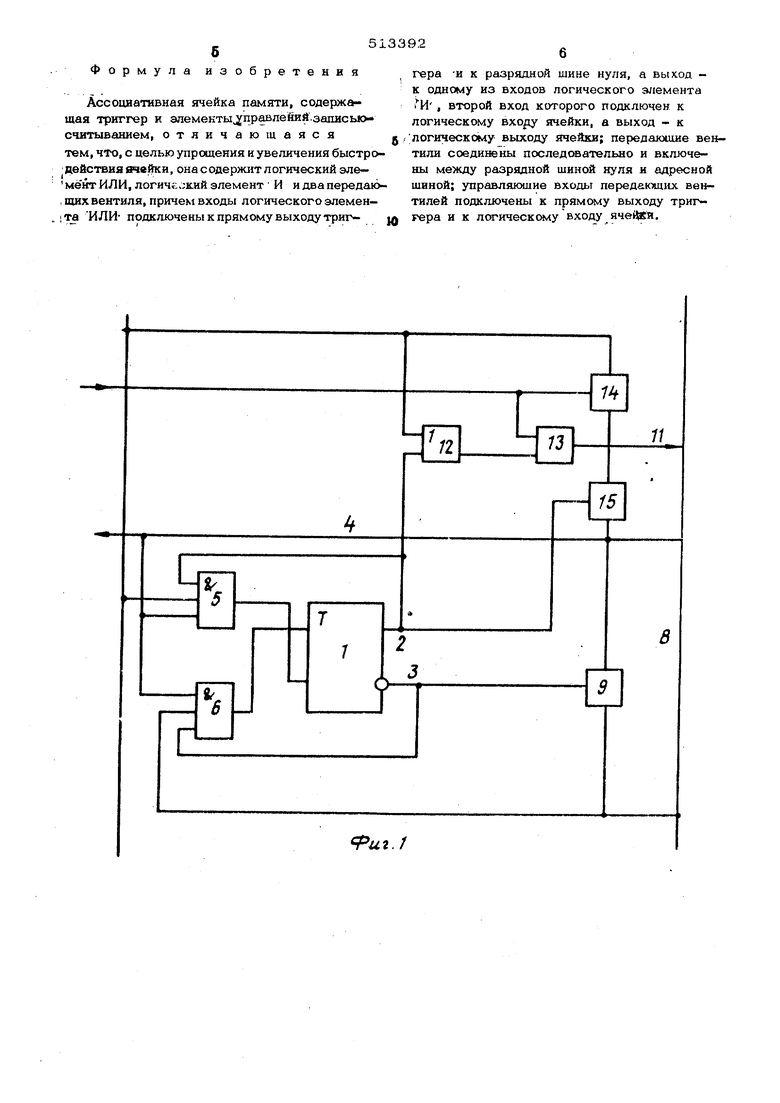

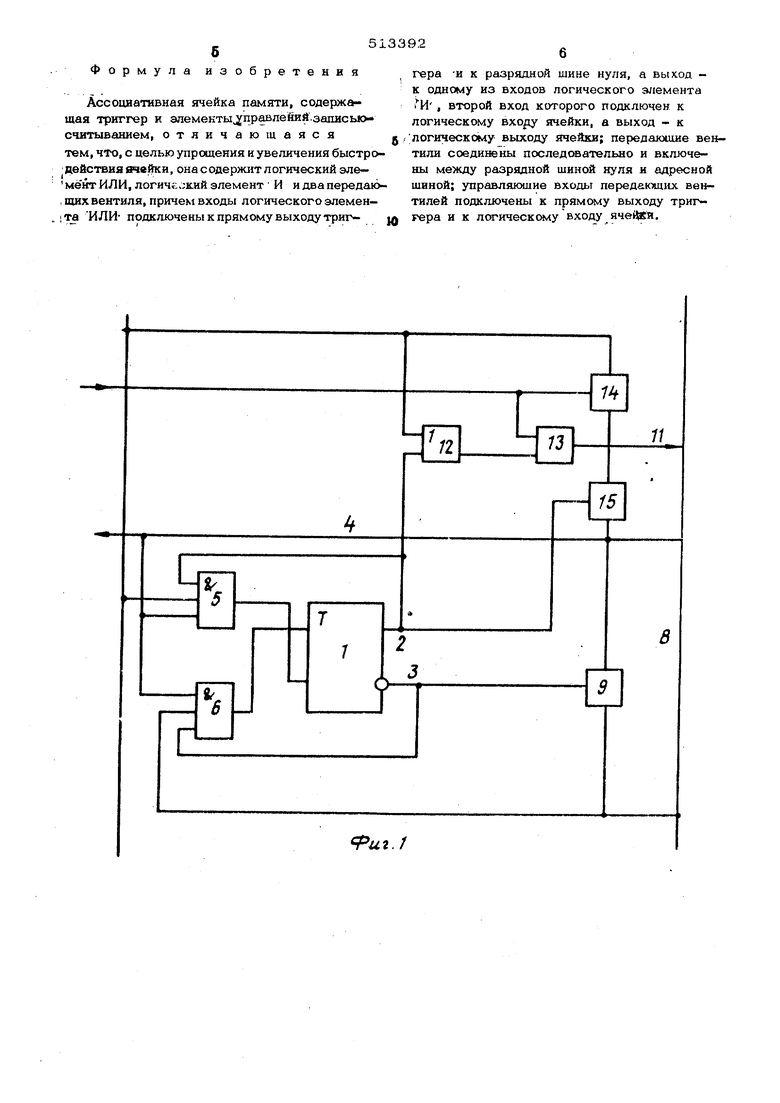

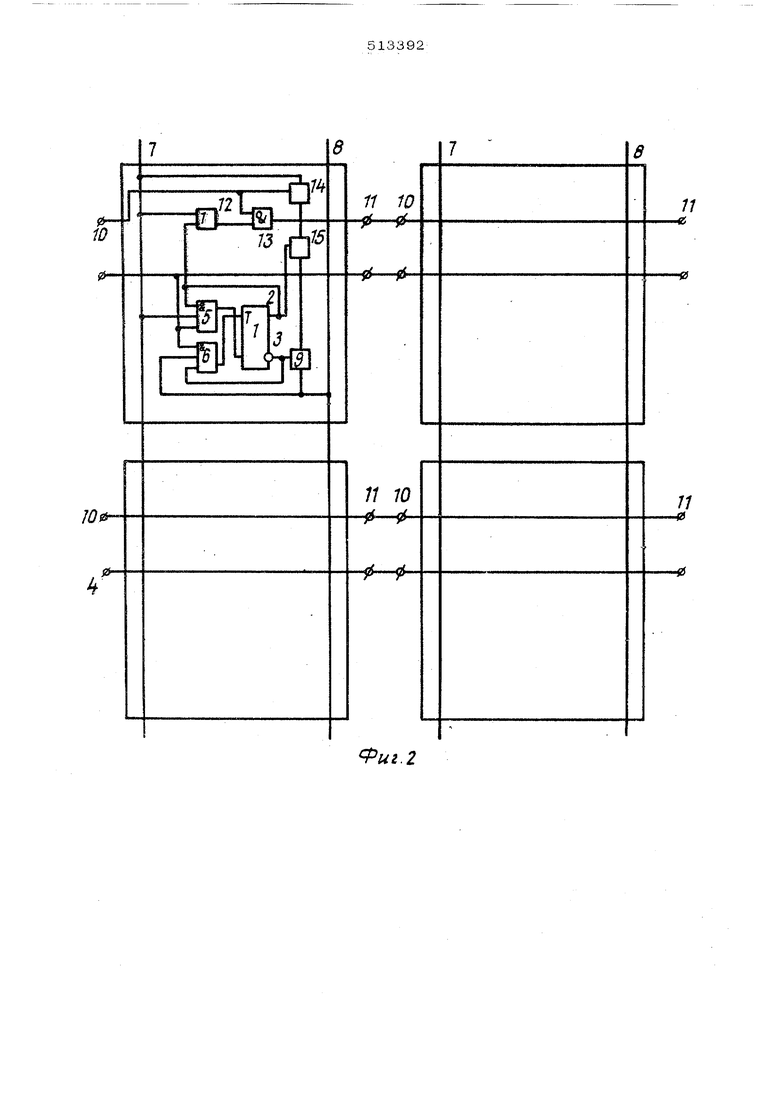

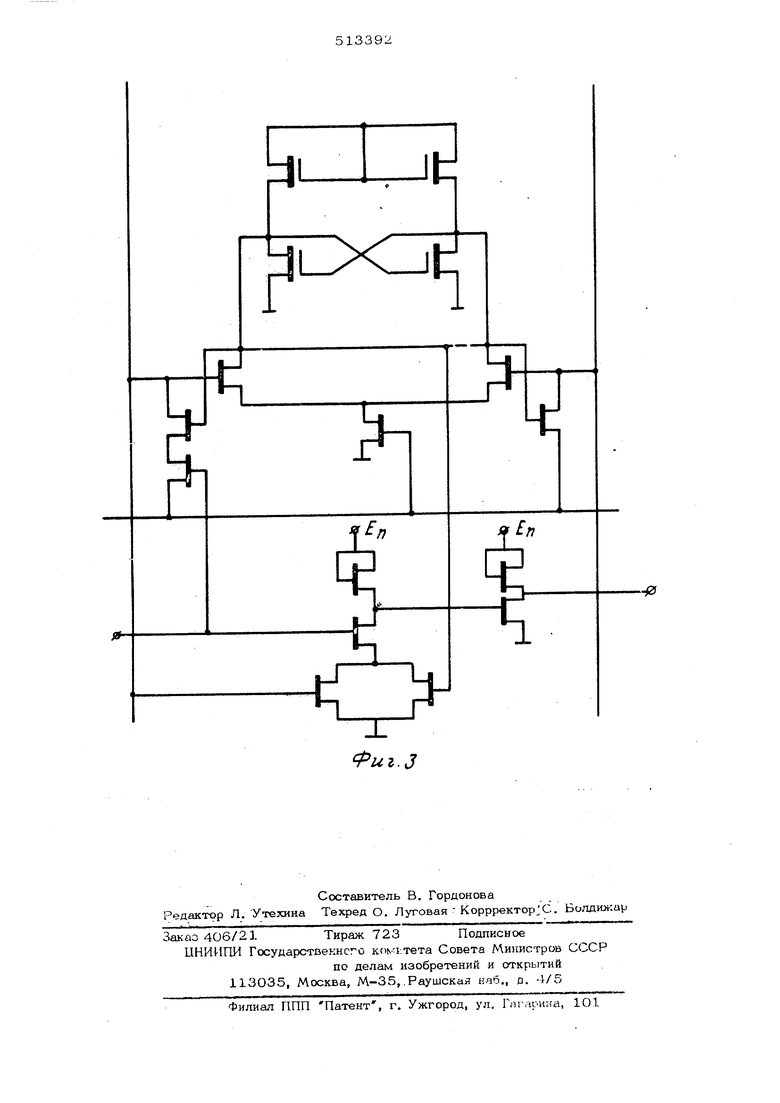

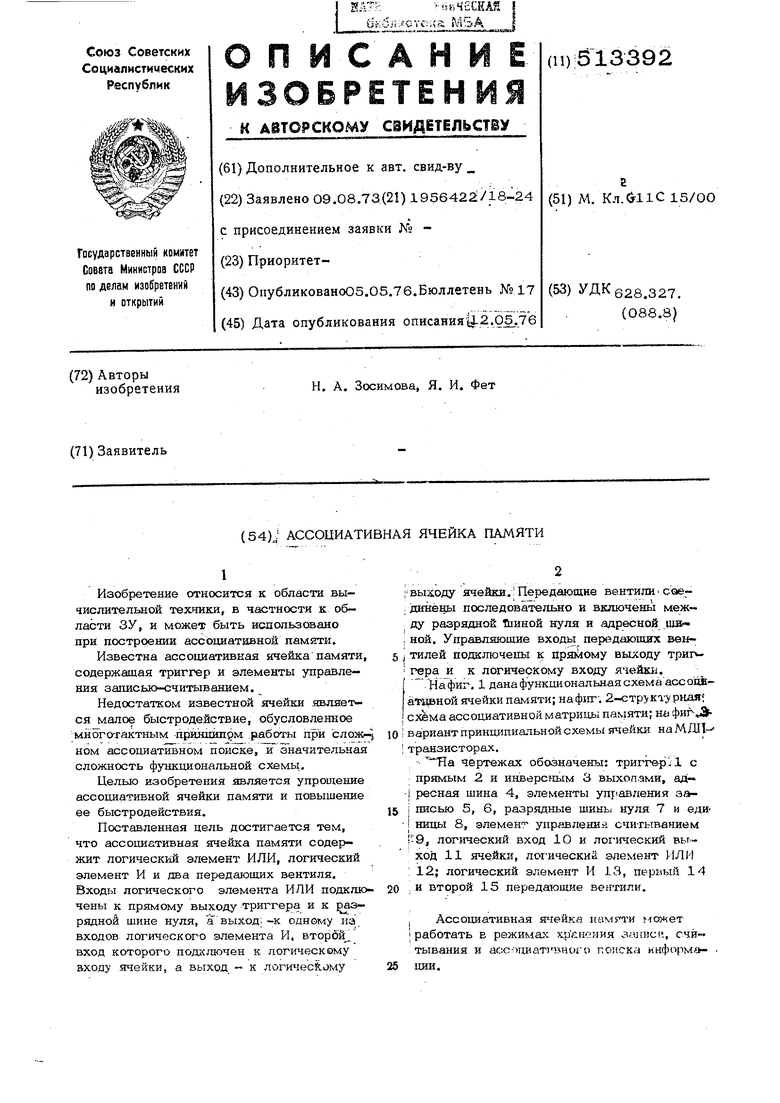

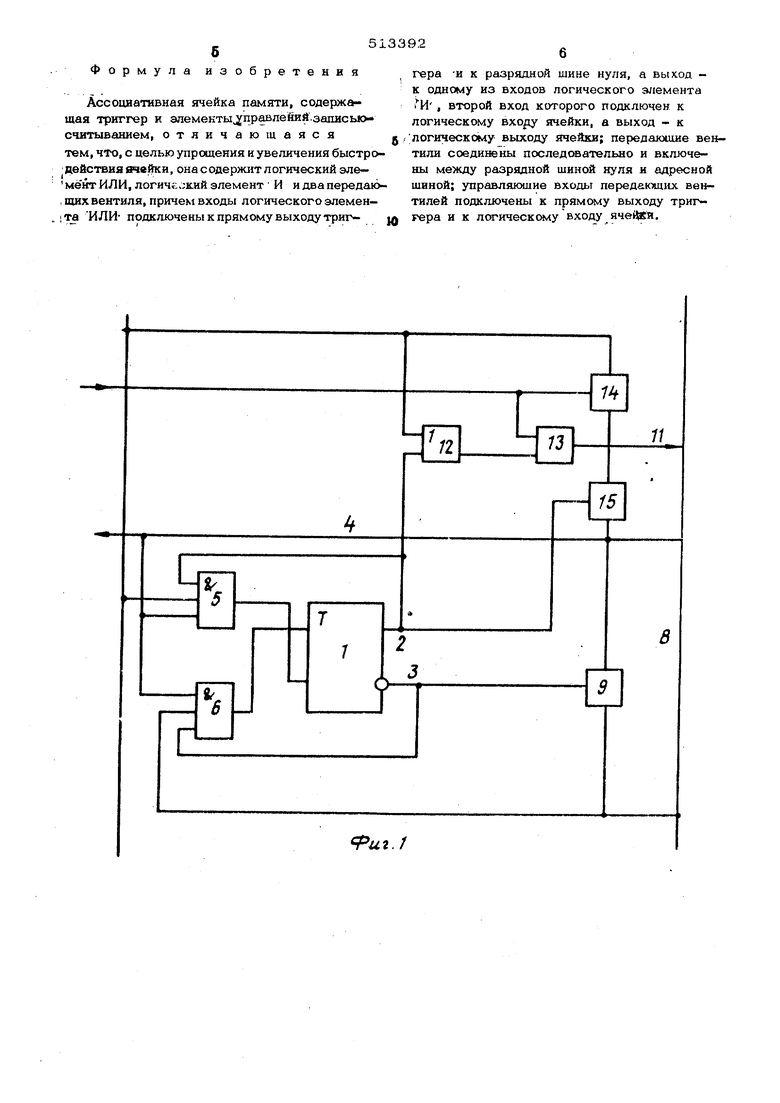

Нафиг. 1 дана функциональная схемаассоЙЕатшаной ячейки памяти; . 2-е тр к туркая схема ассоциативной матрицы памяти; на вариант принципиальной схемы ячейки HaMfllW I транзисторах.

Па чертежах обозначены: триггер с прямым 2 и инверсным 3 выходами, ад- | ресная шина 4, элементы управления писью 5, 6, разрядные шины нуля 7 и еди ницы 8, элемен-: управления считыванием Г9, логический вход 10 и логический выход 11 ячейки, логический элемент ИЛИ : 12; логический элемент И 13, первый 14 20 .и второй 15 передающие вентили.

I Ассоциативная ячейка памяти может I работать в режимах хргнсния зшЕнс ,, считывания и асс-)циат) но1о поиска информа- 25 ции. В режиме хравенна адресная шина 4 в разрядные ишвы нуля 7 в едвницы 8 в ходятся на уровне логического Ю. Обрашенве к ячейке для записи щш с4я тьшанвя осуществляется пооачей логической 1 на адресную шину 4. Элементы управпенвя записью 5, 6 обеспечивают взменевве состояния трвгге ра в выбранной ячейке, если храняшаяся нем информация противоположна информа ции подаваемой парофазно на ра ядные цшны 7 и 8. Элемент управления считьшанием 9 представляет собой передаюишй вентиль, обеспечиваюишй передачу тока считьш ния черэз находящуюся на уровне логической , адресную шину 4 на находяшух ся на уровне логического О разрядную иину 8 при наличии логической на инверсном выходе триггера 1.. В режиме считывания информации разрядные шины 7,8 находятся на уровне логического О, что обеспечивает запирание управляющих записью элемент(ж 5,6 в ячейке. В режимах записи и считывания на лошческой вход 10 ячейки подается логический О. Этот сигнал поступает на вход э; вмвнта И 13 выход которого является логическим выходом 11 ячейки, на котором также оказывается логический О. Р При объединении ассоциативных ячеек в однородную двухмерную ассоциативную матрицу возможно в течение одного такта обращения осуществлюсь слож1уз1Й ассоциагивный поиск чисел, равных заданному, больших или меньщ х заданного. В режиме cpaBHeHjiff на адресной шине 4 и разрядной шине 8 каждой ячейки матрицы оказывается О, что приводит к запиранию элементов 5,6 и 9. : Обратный, код 1каждого разряда признака подается на разрядную щину 7 соответ ствующего столбца матрицы. На логические входы 10 ячеек левого столбца маггрицы подается логическая отпирающая элемент И 13 и первый пер дающей вентиль 14. в триггере ячей ки хранится , то на выходе элемента И13 появляется . В результате на логическом вых:оде 11 ячейки появляется независимо от логв чес(аго1 уровня на рязрядной щине нуля 7. Тшкой же уровень на логическом выходе 1 ячейки появляется в случае, когда в триггере 1 хранится О, а на разрядную щину нуля 7 подается (логический О вра ря/ie признака сравнения). Логический О на логическом выходе 11 ячейки появляется лишь в случае, триггере 1 хранится О, а на разрядую щину нуля 7 подается О (логическая; в разрядепризнака сравиения). Таким образом, появляется на лоическом выходе 11 ячейки только в том лучае, когда Р Щввся в ячейке значеие разряда чвсла равно зиачению соответС7%ую(цего разряда признака или больше его. игнал на логическем выходе 11ячейки крайнего справа столбца появляется только в том случае, если число в сответствующей этой ячейке строке матрицы равцо заданно му признаку влв больше его Если на ло1 ческий вход 10 ячейки подана (все предыдущие разряды чвсла авдысответствуюшим разрядам признака или болыие их), то первый передающий вентиль 14 открыт, при , на лрдмом выходе 2 триггера 1 ячейки ( в разряде числа) открывается второй передающий вентиль 15. При логической на соответствующей 8ТОЙ ячейке разрядной шине 7 (О в разряде признака) через два последовательно соединенных передающих вентиля 14, 15, включенных между разрядной шиной 7 и адресной щиной 4, течет ток в находящуюся на уровне логического О адресную шину 4. Т(жоеые сигналы от всех ячеек в строке мат риды, означающие, что некоторый разряд числа строго болыие соответствующего разряда признака при условии, что все предыдущие . старщие разряды равны соответствующим разрядам признака или больше их, через элемент, ИЛИ проходят на выход адресной I шины 4. В случае когда хранящееся в ячейке число равно соответствующему разряду призна4а.лли меньше его, токовые сигналы в адресную шину 4 от такой ячейки не поступают, так как один.из двух передающих вентилей 14, 15 закрыт. Таким образом, отсутствие сигнала на адресной шине 4 строки матрицы означает, что хранящееся в ней число меньше заданного признака либо равно ему. В первом случае на логическом выходе 11 краЁней справа ячейки (младший разряд числа) должен появиться О, во втором случае - . Наличие сигнала на адресной шине 4 строки при сравнении независимо от состояния логического выхода 11 крайней справа ячейки означает, что хранящееся в данной строке число больше заданного признака. Наиболее просто предлагаемая ассоциативная ячейка памяти может быть реализована на МДП - транзисторах, где в качестве передающих вентилей может быть использован один транзистор. Формула изобретения Ассоциативная ячейка памяти, содержащая триггер и эпементы правлейий.записьюсчитыванием, отличающаяся тем, что, с целью упрощения и увеличения быстро действия ячв1йк и, она с одержит л огический эле мент ИЛИ, логиче лсий элемент И и два передаю , щих вентиля, причем входы логического элемен Та ИЛИ- подключены к прямому выходу триггера И к разрядной шине нуля, а выход к одному из входов логического элемента И , второй вход которого подключен к логическому ячейки, а выход - к логическому выходу ячейки; передающие вентили соединены последовательно и включены между разрядной шиной нуля и адресной шиной; управляюш ие входы передающих вентилей подключены к прямсму выходу триггера и к логическому входу .

5

иг.1

иг.2

Ul.J

Авторы

Даты

1976-05-05—Публикация

1973-08-09—Подача