Изобретение относится к вь чиcли- тельной технике и может найти применение при разработке устройств автономного и встроенного контроля цифровых устройств.

Цель изобретения - повышение достоверности контроля.

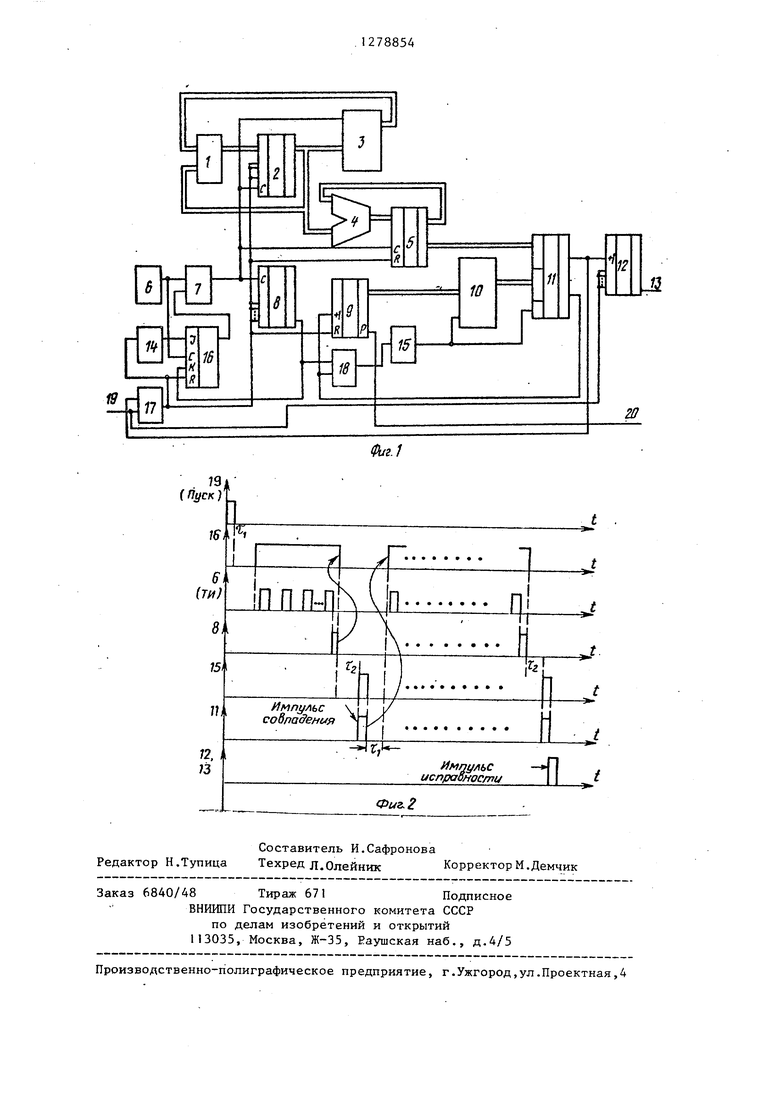

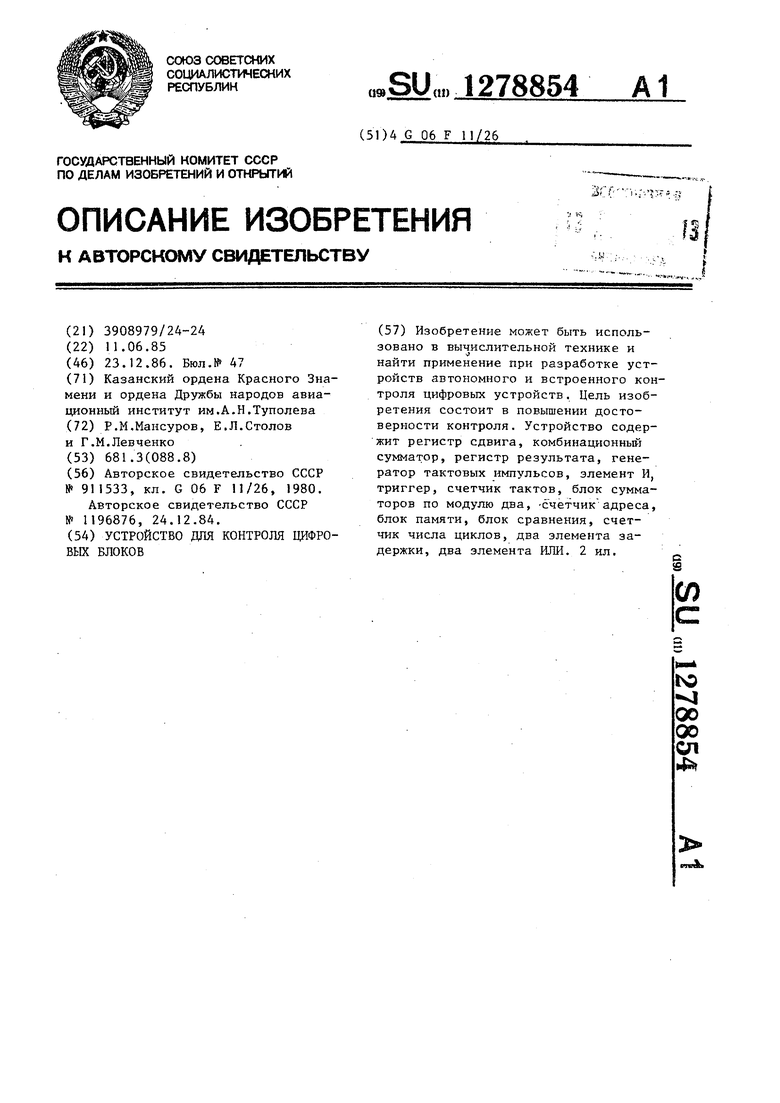

На фиг.Г приведена функциональная схема устройства; на фиг.2 -. временная диаграмма работы устройства.

Устройство содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, контролируемый блок 3, комбинационный сумматор 4, регистр 5 результата, генератор 6 тактовых импульсов элемент И 7, счетчик 8 тактов, счетчик 9 адреса, блок 10 памяти, блок 11 сравнения, счетчик 12 числа циклов, выход 13 сигнала исправности, первый 14 и второй 15 элементы за- держки, триггер 16, первый 17 и второй 18 элементы ИЛИ, вход 19 пуска, выход 20 сигнала неисправности.

Блок 1 сумматоров по модулю два содержит п сумматоров по модулю два, Первые входы, вторые входы и выходы всех п сумматоров по модулю два образуют первую группу входов, вторую группу входов и группу выходов блока

1сумматоров по модулю два соответственно. Выходы п сумматоров по модулю два подключены к входам соответствующих разрядов п-разрядного регистра

2сдвига. Первые входы п сумматоров по модулю два подключены к выходам п разрядов регистра 2 сдвига, причем первый вход i-ro сумматора соединен с выходом (i-l)-ro разряда регистра 2 сдвига, где , а первый вход первого сумматора соединен с выходом п-го разряда регистра 2 сдвига. Вторые входы п сумматоров по модулю два соединены с одноименными выходами контролируемого блока. Ре- гистр 2 сдвига, блок 1 су1 1маторов по модулю два и контролируемый блок 3 вместе с указанными связями представляют собой автономньй генератор, работающий под действием тактовых импульсов .

Двоичные числа, порождаемые этим автономным генератором, с г руппы выходов регистра 2 сдвига поступают на группу входов контролируемого блока 3. Вид последовательности двоичных чисел автономного генератора определяется начальным состоянием .регистра 2 сдвига, начальным состоянием конт

5

5

5

0

5

0

0

ролируемого блока 3 и его исправностью или неисправностью. В процес- се работы автономный генератор ввиду детерминизма структуры входит в цикл. т.е. на выходах регистра 2 сдвига генерируется последовательность двоичных чисел у(1), у (2) , . . . , у(р), у(р+1),...,у(р+Т), y(p-i-l),..., содержащая непериодическую часть у(1), у(2),...,у(р) и периодическую часть у(р+1),..., у(р+Т). При исправном контролируемом блоке 3, начальное состояние которого может быть любым, автономный генератор входит в цикл, принадлежащий некоторому множеству циклов. Попадание в циклы-, не принадлежащие указанному множеству, говорит о неисправности объекта контроля. Задача устройства заключается в определении циклов, в которые попадает автономный генератор. В общем случае конкретный цикл характеризуется суммой своих двоичных чисел.

Комбинационный сумматор 4 совместно с регистром 5 результата служит дпя накопления суммы чисел x(t) последовательности, где t - количество суммирующих чисел.

Счетчик 8 тактов служит для задания количества t суммирующих чисел последовательности. Емкость счетчика 8 тактов выбирается такой, чтобы самый длинный цикл автономного генератора проходил достаточно большое количество раз. В этом случае величина x(t) , равная значению К старших разрядов x(t) ., будет одной и той же для конкретного цикла независимо от начального состояния контролируемого блока. Сумма чисел непериодической части, зависяЕ1ая от начального состояния контролируемого блока, и сумма чисел неполк;ого цикла в конце последовательности сказываются лищь на значениях младших разрядов x(t), которые на учитываются. Назовем величину x(,t) параметром цикла.

Блок 10 памяти служит для хранения параметров циклов, соответствующих исправному контролируемому блоку. Параметры циклов должны быть известны заранее и занесены в блок 10 памяти, начиная с нулевой ячейки.

Счетчик 9 адреса служит дпя хранения адреса считываемой ячейки блока 10 памяти.

Блок 11 сравнения служит дл сравнения полученных в процессе контроля

,величин x(t) с параметрами циклов записанных в ячейках блока 10 памяти Счетчик 12 числа циклов задает общее число циклов контроля.

Устройство работает следующим об- раз.ом.

Сигнал на входе 19 пуска устанавливает начальное значение в счетчике 12 числа циклов и, проходя через элемент ИЛИ 17, устанавливает начальные состояния регистра 2 сдвига и счетчика 8 тактов, сбрасывает в нулевые состояния регистр 5, счетчик 9 адреса и триппер 16. Этот же сигнал, задержанный элементом 14 задержки на время приведения устройства в исходное состояние, устанавливает триггер 16 в единичное состояние. Сигнал с прямого выхода триггера 16 открывает элемент И 7, и импульсы с выхо- да тактового генератора 6 поступают . через элемент И 7 на входы синхронизации регистра 2 сдвига, контролируемого блока 3, регистра 5 и счетчика 8 тактов. Тактовые импульсы иницииру ют работу автономного генератора, состоящего из регистра 2 сдвига, контролируемого блока 3 и блока 1 сумматоров по модулю два.

С выхода регистра 2 сдвига кодо- вые комбинации поступают на входы контролируемого блока, на вход блока 1 сумматоров по модулю два и на вход комбинационного сумматора 4. Реакция контролируемого блока 3 на входное воздействие поступает с выхода контролируемого блока на вторую группу входов блока 1 сумматоров по модулю два. Выходные сигналы блока 1 сумматоров по модулю два участвуют в фор- мировании нового значения разрядов регистра 2 сдвига.

Комбинационный сумматор 4 совместно с регистром 5 осуществляет накопление суммы двоичных чисел с выхода регистра 2 сдвига. Число тактов работы автономного генератора определяется емкостью счетчика 8 тактов, импульс с выхода переполнения которого устанавливает в нулевое состояние триггер 16, что прерывает поступление тактовых кнпулъсов та блоки устройства . Импульс переполнения счетчика В тактов одновременно проходит

через элемент KJli 18 и элемент 15 за- 55 Если в течение каждого цикла провердержки на вход считывания блоков 10 памяти и на вход сравнения блока 11 сравнения. Это позволяет произвести, сравнение чисел, поступающих по пер25

5

fO15 20 35 40

4550

вой и второй группам входов блока 1 1 сравнения. К этому моменту на первой группе входов блока 11 сравнения присутствует число x(t) , являющееся значением К старших разрядов суммы, накопленной в регистре 5, а на второй группе входов блока 11 сравнения присутствует параметр циклаi содержащийся в нулевой ячейке блока памяти, поскольку счетчик 9 адреса в этот момент имеет нулевое значение. При несовпадении чисел, поступающих по двум группам входов блока 11 сравнения, сигнал с выхода несравнения блока 11 сравнения поступает на суммирующий вход счетчика 9 адреса и увеличивает его содержимое на единицу. Этот же сигнал, прошедший через, элемент ИЛИ 18 и задержанный элементом 15 задержки на время установления нового адреса, разрешает сравнение числа с содержимым следующей ячейки блока 10 памяти.

Таким образом, блок 11 сравнения осуществляет сравнение числа x(t)| с параметрами циклов, записанных в последовательных ячейках блока 10 памяти. Если x(t) не совпадает ни с -одним из параметров, записанных в ячейках блока 10 памяти, то импульс переполнения счетчика 9 адреса, поступающий на выход 20, свидетельствует о неисправности контролируемого блока. При совпадении полученной величины x(t) содержимым одной из ячеек блока 10 памяти сигнал с выхода совпадения поступает на суммирующий входсчетчика 12 числа циклов проверки и одновременно на второй вход элемента ИЛИ 17, чем обеспечивается повторный запуск устройства на новый цикл проверки. Сигнал совпадения на выходе блока I1 сравнения говорит о том, что устройство обнаружило один из циклов, соответствующих исправному объекту контроля.

Повторный запуск устройства в общем случае происходит при другом неизвестном начальном состоянии контролируемого блока и приводит к обнаружению цикла с другим параметром. Общее число циклов проверки задается - емкостью счетчика 12 числа циклов.

ки фиксируется сигнал совпадения соответствующей величины x(t)| с содержимым ячеек блока 10 памяти, то сигнал переполнения счетчика 12 числа циклов, поступающий на выход 3, с большой достоверностью говорит об исправности объекта контроля.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее регистр сдвига, комбинационный сумматор, регистр результата, генератор тактовых.импульсов, элемент И, триггер, счетчик тактов , причем группа разрядных выходов регистра сдвига соединена с первой группой информационных входов комбинационного сумматора и является группой информационных выходов устройст ва дпя подключения к группе информационных входов контролируемого блока вторая группа информационных входов комбинационного сумматора соединена с группой выходов младших разрядов регистра результата, выход генератора тактовых импульсов -соединен с первым входом элемента И и синхровхо- дом триггера, первый установочный вход и выход которого соединены со ответственно с выходом переполнения счетчика тактов и вторым входом эле- мента И, отличающееся тем, что, с целью повышения досто верности контроля, в устройство вве дены блок сумматоров по модулю два, счетчик адреса, блок памяти, блок сравнения, счетчик числа циклов, два элемента задержки, два элемента ИЛИ, причем первая и вторая группы информационных входов блока сумматоров по модулю два соединены соответственно с группой разрядных выходов регистра сдвига и группой информационных входов устройства для подключения к группе выходов контролируемого блока, установочные входы регистра

-

-

-

,

10

15

20

25

30

сдвига и счетчика тактов, входы сброса счетчика адреса, триггера и регистра результата объединены и подключены к выходу первого элемента ИЛИ, первый вход которого соединен с выходом равенстве блока сравнения, выход неравенства которого подключен к счетному входу счетчика адреса и первому входу второго элемента ИЛИ, первый вход которого соединен с выходом переполнения счетчика тактов, синхровходы счетчика тактов регистра результата, регистра сдвига и выход устройства для подключения к входу синхронизации контролируемого бло- ка объединены и подключены к выходу элемента И, второй вход первого элемента ИЛИ подключен к входу запуска устройства и установочному входу счетчика числа циклов, выход переполнения которого является выходом исправности устройства, первая и вторая группы информационных входов блока сравнения соединены соответственно с группой выходов старших разрядов регистра результата и группой выходов блока памяти, группа информационных входов которого подключена к группе разрядных выходов счетчика адреса, выход второго элемента ИЛИ через первый элемент задержки .соединен с входом считывания блока памяти и входом разрешения сравнения блока сравнения, выход Е;ервого элемента 35 ИЛИ через второй элемент задержки

подключен к второму установочному - входу триггера, выход переноса счетчика адреса является выходом неисправности устройства, группа выходов сумматоров по модулю два подключена к группе информационных входов регистра сдвига.

40

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1986 |

|

SU1354196A2 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1196876A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1527636A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1302285A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1411750A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU935951A1 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

Изобретение может быть использовано в вычислительной технике и ч найти применение при разработке устройств автономного и встроенного контроля цифровых устройств. Цель изобретения состоит в повьгаении достоверности контроля. Устройство содержит регистр сдвига, комбинационный сумматор, регистр результата, генератор тактовых импульсов, элемент И, триггер, счетчик тактов, блок сумматоров по модулю два, -счетчик адреса, блок памяти, блок сравнения, счетчик числа циклов, два элемента задержки, два элемента ИЛИ. 2 ил. (Я С N9 00 оо СП

| Устройство для формирования тестовых воздействий | 1980 |

|

SU911533A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1196876A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-11—Подача