Изобретение относится к вычислительной технике, может найти применение при разработке устройств автономного и встроенного контроля цифровых устройств и является дополнительным к авт.св. № 127885А.

Цель изобретения - повьтеМне надежности устройства за счет исключения ложного срабатывания блока сравнения и повышения достоверности контроля цифровых блоков за счет вы- гшсления количества одинаковых параметров циклов.

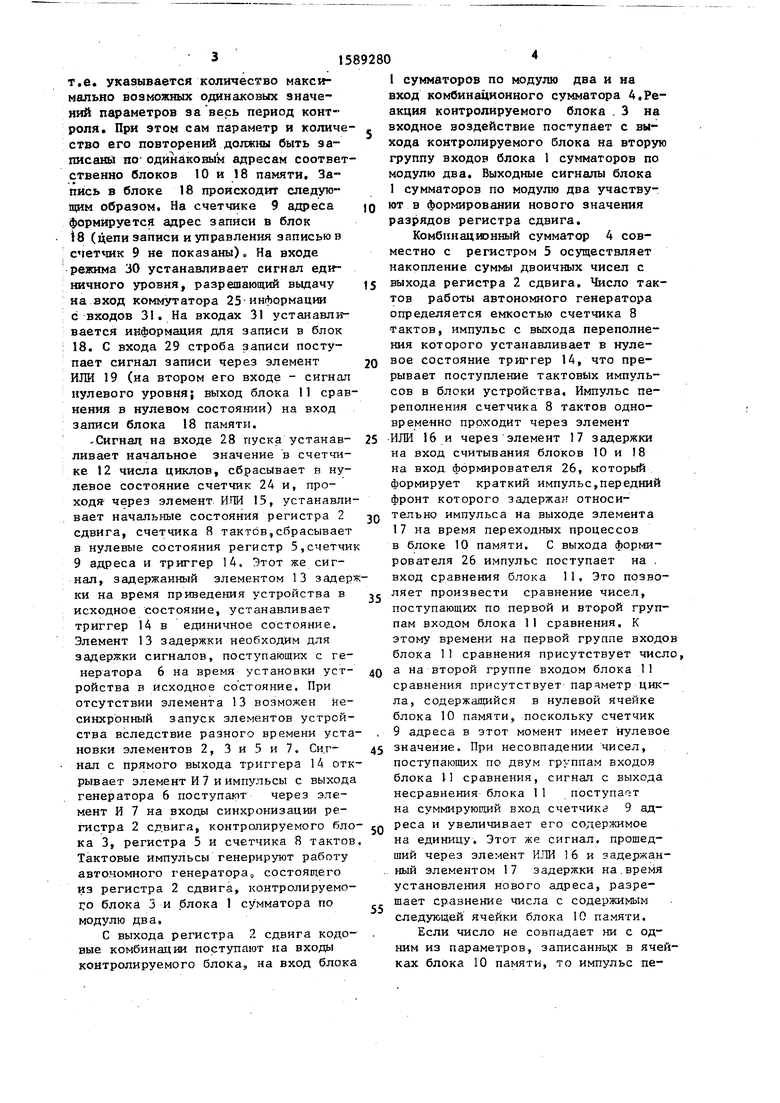

На чертеже приведена функциональная схема устройства. .

Устройство для контроля цифровых , блоков содержит блок 1 сумматоров по модулю два, регистр 2 сдвига, контролируемый блок 3, комбинационный, сумматор 4, регистр 5 результата, генератор 6 тактовых импульсов, первый элемент И 7, счетчик 8 тактов,

счетчик 9 адреса, первый блок 10 памяти, блок 11 сравнения, счетчик 12 числа циклов, первый 13 элемент задержки, триггер 14, первый 15,второй 16 элементы ИЖ, второй элемент 17 задержки, второй блок 18 памяти,третий элемент ИЛИ 9, третий элемент 20 задержки, второй элемент И 21, четвертый 22, пятый 23 элементы задержки, счетчик 24, коммутатор 25, формирователь 26 одиночного импульса, четвертый элемент ИЛИ 27, вход 28 пуска, первый 29,второй 30 управляющие входы,информационные входы 31,выход 32 сигнала исправности,выход 33 сигнала неисправности.

Устройство работает следующим образом.

Предварительно в блок 18 памяти записывается в дополнительном виде - наименьшее количество параметров циклов, недопустимое при контроле,

С

У 70

D 30

К)

.е. указывается количество максиально возможных одинаковых значений параметров за весь период контоля. При этом сам параметр и количе- , ство его повторений должны быть за- пясанй ПО одинаковым адресам соответственно блоков 10 и 18 памяти. Запись в блоке 18 происходит следующим образом. На счетчике 9 адреса ю формируется адрес записи в блок 18 (цепи записи и управления записью в счетчик 9 не показаны) На входе режима 30 устанавливает сигнал единичного уровня, разрешающий выдачу 15 на вход коммутатора 25 информации с входов 31. На входах 31 устанавливается информация дпя записи в блок 18. С входа 29 строба записи поступает сигнал записи через элемент 20 ИЛИ 19 (на втором его входе - сигнал нулевого уровня; выход блока 11 сравнения в нулевом состоянии) на вход записи блока 18 памяти.

-Сигнал на входе 28 пуска устанав- 25 ливает начальное значение в счетчике 12 числа циклов, сбрасывает в нулевое состояние счетчик 2А и, проходя- через элемент ИЛИ 15, устанавливает начальные состояния регистра 2 сдвига, счетчика 8 тактов,сбрасывает в нулевые состояния регистр 5,счеТчик 9 адреса и триггер 14. Этот же сигнал, задержанный злементом 13 задерж30

ки на время приведения устройства в исходное состояние, устанавливает триггер 14 в единичное состояние. Элемент 13 задержки необходим для задержки сигналов, поступающих с генератора 6 на время установки устройства в исходное состояние. При отсутствии элемента 13 возможен несинхронный запуск элементов устройства вследствие разного времени установки элементов 2, 3 и 5 и 7. Сигнал с прямого выхода триггера 14 открывает элемент И 7 и импульсы с выхода генератора 6 поступают через элемент И 7 на входы синхронизации регистра 2 сдвига, контролируемого блока 3, регистра 5 и счетчика 8 тактов. Тактовые импульсы генерируют работу автономного генератора, состоящего из регистра 2 сдвига, контролируемого блока 3 и блока 1 сумматора по модулю два.

С выхода регистра 2 сдвига кодовые комбинации поступают па входы контролируемого блока, на вход блока

5

0

5

0

5

0

5

I сумматоров по модулю два и на вход комбинационного сумматора А,Реакция контролируемого блока . 3 на входное воздействие поступает с выхода контролируемого блока на вторую группу входов блока 1 сумматоров по модулю два. Выходные сигналы блока 1 сумматоров по модулю два участвуют в формировании нового значения разрядов регистра сдвига.

Комбинационный сумматор А совместно с регистром 5 осуществляет накопление суммы двоичных чисел с выхода регистра 2 сдвига. Число тактов работы автономного генератора определяется емкостью счетчика 8 тактов, импульс с выхода переполнения которого устанавливает в нулевое состояние триггер 14, что прерывает поступление тактовых импульсов в блоки устройства. Импульс переполнения счетчика 8 тактов одновременно проходит через элемент ИЛИ 16 и через элемент 17 задержки на вход считывания блоков 10 и 18 на вход формирователя 26, который формирует краткий импульс,передний фронт которого задержан относительно импульса на выходе элемента 17 на время переходных процессов в блоке 10 памяти, С выхода формирователя 26 импульс поступает на . вход сравнения блока 11. Это позволяет произвести сравнение чисел, поступающих по первой и второй группам входом блока 11 сравнения. К этому времени на первой группе входов блока 11 сравнения присутствует число, а на второй группе входом блока II сравнения присутствует паряметр цикла, содержащийся в нулевой ячейке блока 10 памяти, поскольку счетчик 9 адреса в этот момент имеет нулевое значение. При несовпадении чисел, поступающих по двум группам входов блока И сравнения, сигнал с выхода несравнения блока 1 1 поступа зт на суммируюпшй вход счетчика 9 адреса и увеличивает его содержимое на единицу. Этот же сигнал, прошедший через элемент ИЛИ 16 и задержанный элементом 17 задержки на.время установления нового адреса, разрешает сравнение числа с содержимым следующей ячейки блока 10 памяти.

Если число не совпадает ни с одним из параметров, записаннь1х в ячейках блока 10 памяти, то импульс переполнения счетчика 9 адреса,посту- - narowtii через четвертый элемент ИЛИ 27 на выход 33, свидетельствует о неисправности контролируемого блока.

При совпадении полученного числа с содержимым одной из ячеек блока 10 памяти сигнал с выхода совпадения блока 11 сравнения поступает на суммирующий вход счетчика 12 числа циклов и на второй вход элемента ИЛИ 15, чем обеспечивается повторный запуск устройства на новый цикл проверки. Одновременно этот сигнал поступает на первый вход второго элемента И 21, на второй вход которого поступает задержанный на элементе 20 задержки сигнал считывания блоков памяти с выхода элемента 17, по которому происходит считывание информации из блока 18. Информация на информационных входах счетчика 24 по сигналу с вьтхода элемента И 21 параллельно записывается в счетчик 24, после чего содержимое счетчика 24 увеличивается на -i-l (по сигналу с выхода элемента И 21,задержанному на элементе 22 задержки) и через открытый по вторым входам коммутатора. 25 (на входе 30 режима в это время сигнал нулевого уровня) поступает на информационный вход блока 18 памяти. Одновременно сигнал с выхода элемента 22 задержки через элемент 23 задержки и третий элемент ИЛИ 19 (на его первом входе сигнал нулевого уровня) поступает на вход записи блока 18, по которому осуше- ствляется запись информации по адресу, установленному на выходе счетчика 9.

Повторный запуск устройства в общем случае происходит при другом

памяти, увеличенное на +1 в счетчике 24, сформирует на выходе переполнения сигнал,, который поступает на выход 33 и сввдетельствует о неисправности. Адрес, т.е. параметр, по которому происходит зацикливание,можно определить на выходе счетчика 9. Если в течение каждого цикла верки фиксируется сигнал совпадения соответствующего числа с содержимым ячеек блока 10 памяти, то сигнал переполнения счетчика 12 числа циклов, поступающий на выход 32, с большой

J5 достоверностью говорит об исправности объекта контроля. Одновременное формирование сигнала на выходах 32 и 33 свидетельствует об неисправности контролируемого блока или об регу20 лярном считывании одного и того же параметра цикла, что при данном методе контроля маловероятно.

saapfl-zf jaa.. га9.зл.1 ЗйЗ-эп-И - задержка на соответствующих элемен25 тах, контроль цифрового блока заканчивается появлением сигнала на выходе 32 или (и) 33.

Формула изобретения

30

Устройство для контроля цифровых

блоков по авт.св. № 1278854, отличающееся тем, что, с целью повышения надежности устройства за счет исключения ложного срабатывания блока сравнения и повышения достоверности контроля цифровых блоков за счет вычисления количества одинаковых параметров циклов, в уст- дл ройство введены второй блок памятиj

35

счетчик, второй, элемент И, коммутатор, третий и четвертый элементы ИШ, третий, четвертый, пятый элементы задержки и формироватаг.с гдакочнеизвестном начальном состоянии конт- j ного импульса, выход которого соеди- ролируемого блока и приводит к обнаружению цикла с другим параметром. В этом случае в блок 18 информация увеличения на +1 записывается по дру50

гому адресу. Однако при неисправности контролируемого блока или аппаратуры данного устройства может быть, что параметр цикла не выходит из зо- нь, регулярно сравнивается с одной из ячеек блока 10, например только из одной или двумя, что свидетельст- ву.ет об неисправностях в аппаратуре. Тогда за несколько повторных запусков содержимое определенной ячейки

55

нен с входом разрешения блока сравнения, а вход - с выходом второго элемента задержки, входом считывания второго блока памяти и входом третьего элемента задержки, выход третьего элемента задержки соедикан с первым входом второго элемента И, второй, вход которого соединен с первым входом первого элемента ИЛИ,выход второго элемента Н соединен с установочным входом счетчика и через четвертый элемент задер ки - со счетным входом счетчика, н через пятый элемент задержки соединен с первым

памяти, увеличенное на +1 в счетчике 24, сформирует на выходе переполнения сигнал,, который поступает на выход 33 и сввдетельствует о неисправности. Адрес, т.е. параметр, по которому происходит зацикливание,можно определить на выходе счетчика 9. Если в течение каждого цикла проверки фиксируется сигнал совпадения соответствующего числа с содержимым ячеек блока 10 памяти, то сигнал переполнения счетчика 12 числа циклов, поступающий на выход 32, с большой

достоверностью говорит об исправности объекта контроля. Одновременное формирование сигнала на выходах 32 и 33 свидетельствует об неисправности контролируемого блока или об регулярном считывании одного и того же параметра цикла, что при данном методе контроля маловероятно.

saapfl-zf jaa.. га9.зл.1 ЗйЗ-эп-И - задержка на соответствующих элементах, контроль цифрового блока заканчивается появлением сигнала на выходе 32 или (и) 33.

Формула изобретения

Устройство для контроля цифровых

блоков по авт.св. № 1278854, отличающееся тем, что, с целью повышения надежности устройства за счет исключения ложного срабатывания блока сравнения и повышения достоверности контроля цифровых блоков за счет вычисления количества одинаковых параметров циклов, в уст- ройство введены второй блок памятиj

счетчик, второй, элемент И, коммутатор, третий и четвертый элементы ИШ, третий, четвертый, пятый элементы задержки и формироватаг.с гдакоч j ного импульса, выход которого соеди-

50

55

нен с входом разрешения блока сравнения, а вход - с выходом второго элемента задержки, входом считывания второго блока памяти и входом третьего элемента задержки, выход третьего элемента задержки соедикан с первым входом второго элемента И, второй, вход которого соединен с первым входом первого элемента ИЛИ,выход второго элемента Н соединен с установочным входом счетчика и через четвертый элемент задер ки - со счетным входом счетчика, н через пятый элемент задержки соединен с первым

входом третьего элемента ИЛИ,второй вход которого подключен к первому входу строба записи устройства, а выход соединен с входом записи второ- го блока памяти, группа адресных входов которого соединена с группой разрядных выходов счетчика адреса, группа информационных входов второго блока памяти соединена с группой вы- ходов коммутатора, группа выходов вто- рого блока памяти соединена с группой информационных вхЬдов счетчика, вход сброса которого соединен с входом запуска устройства, группа выходов

счетчика соединена с первой группой информационных входов коммутатора, вторая группа информационных входов и управляющий вход которого соединены соответственно с группой информационных входов и входом режима устройства, выход переполнения счетчика соединен с первым входом, четвертого элемента ИЛИ, второй вход которого соединен с выходом переполнения счетчика адреса, выход четвертого элемента является выходом неисправности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1986 |

|

SU1354196A2 |

| Устройство для тестового контроля электромеханических блоков | 1982 |

|

SU1151973A1 |

| Устройство для контроля оперативной памяти | 1986 |

|

SU1401520A2 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для автоматического контроля больших интегральных схем | 1981 |

|

SU1027735A1 |

Изобретение относится к вычислительной технике и может найти применение при разработке устройств автономного и встроенного контроля цифровых устройств. Целью изобретения является повышение надежности устройства за счет исключения ложного срабатывания блока сравнения и повышения достоверности контроля цифровых блоков благодаря вычислению количества одинаковых параметров циклов. В устройство введены второй блок памяти, счетчик, коммутатор, третий и четвертый элементы ИЛИ второй элемент И, третий, четвертый, пятый элементы задержки и формирователь одиночного импульса. 1 ил.

J2

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-22—Подача