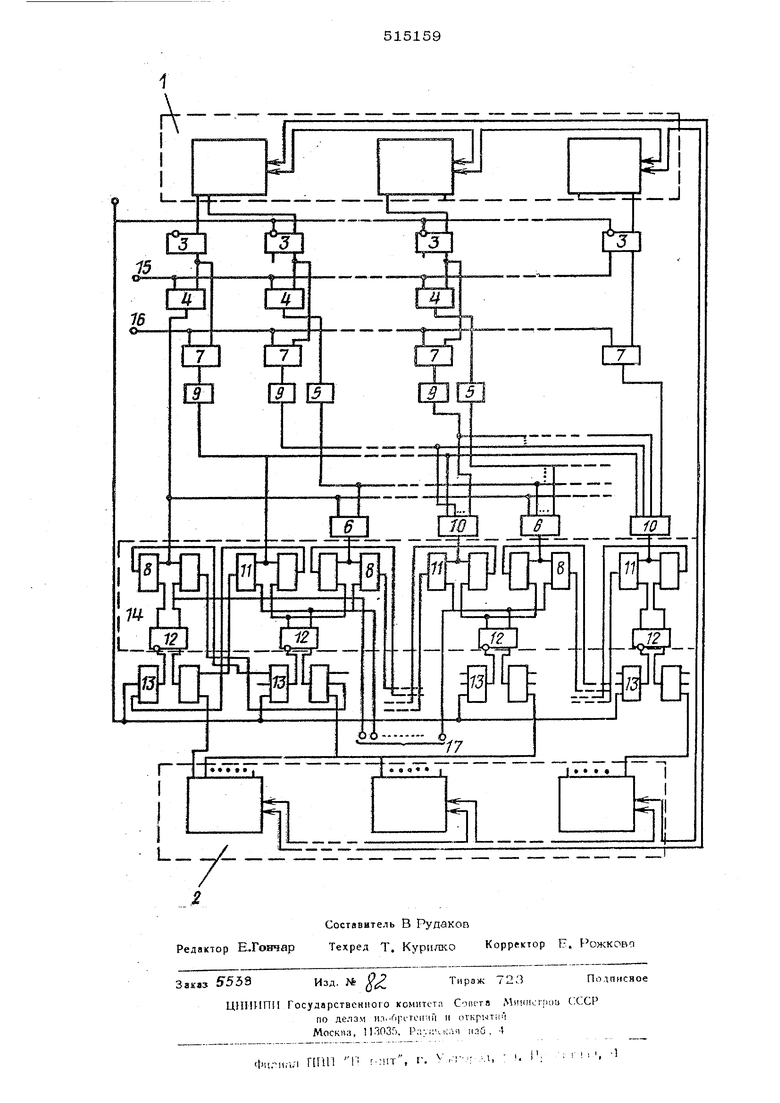

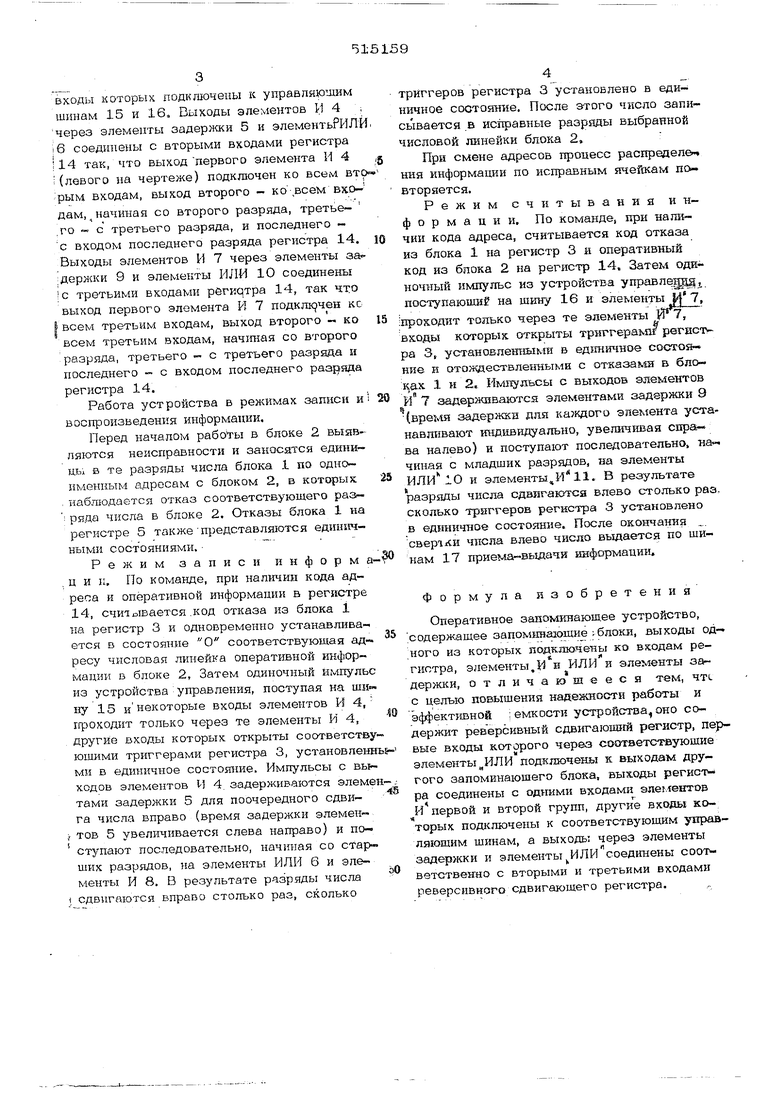

Изобретение относится к запоминающим устройствам. Известно оперативное запоминающее устройство, содержащее запоминающие блоки выходы одного из которых подключены к входам регистра, элементы И,и, элементы задержки. В этом устройстве могут быть использованы интегральные запоминающие ячейки с небольщим кблйчеством дефектов, а также отсутствует возможность восстановления работоспособности устройства при возникновении новых неисправностей. Цель изобретения - повыщение надежнос ти работы и эффективной емкости устройстса. Для ее осуществления предлагаемое устройство содержит реверсивный сдвигающий регистр, первые входы которого через соответствующие элементы,, ИЛИ подключены к выходам другого запоминающего блока, выходы регистра соединены с одними входами элементов И первой и второй групп, другие входы которых подключены к соответствующим управл$аошим шинам, а выходы через элементы задержки и элементы ИЛИ соединены соответственно с вторыми и третьими входами реверсивного сдвигающего регистра. На чертеже изображена блок-схема предложенного устройства. Устройство содержит запоминающий блок 1, служащий для хранения информации об отказах электронных элементов, запоминающий блок 2 предназначенный для хранения оперативной информации, регистр 3, элементы И 4 первой группы, элементы задержки 5, элементы ИЛИ 6 элементы И 7 второй группы, элементы И 8 третьей группы, служащие для сдвига числа вправо, элементы задержки 9 элементы ИЛИ 10, элементы И 11 четвертой группы, служащие для сдвига влево, триггеры 12, элементы ИЛИ 13. Элементы И 8 и 11 и триггеры 12 образуют реверсивный сдвигающий регистр 14. Первые входы регистра 14 через элементы,ИЛИ 13 подключены к выходам блока 2. Выходы регистра 3 соединены с одними входами элементов и 7, другие входы которых подключены к управляющим шинам 15 и 16, Выходы элементов И 4 через элементы задержки 5 и элементьРИЛ 16 соединены с вторыми входами регистра il4 так, что выходпервого элемента И 4 ; (левого на чертеже) подключен ко вт рым входам, выход второго - ко-,всем вхо- дам,начиная со второго разряда, третье,го - с третьего разряда, и последнего с входом последнего разряда регистра 14. Выходы элементов И 7 через элементы за ;держки 9 и элементы ИЛИ 10 соединены С третьими входами рбгкатра 14, так что выход первого элемента И 7 подклк чен ко I всем третьим входам, выход второго - ко всем третьим входам, начзгаая со второго разряда, третьего - с третьего разряда и последнего -- с входом последнего разряда регистра 14. Работа устройства в режимах записи и воспроизведения информации. Перед началом рабогы в блоке 2 выявляются неисправности и заносится едшти- ubi в те разряды числа блока 1 по одноименным адресам с блоком 2, в которых наблюдается отказ соответствующего ряда числа в блоке 2. Отказы блока 1 на регистре 5 такжепредставляются един55чными состояниями. Режим записи информ а , н и п. По команде, при наличии кода адреса и оперативной информации в регистре 14, считывается .код отказа из блока i на регистр 3 и одновременно устанавливается в состояние О соответствующая ад ресу числовая линейка оперативной информации в блоке 2, Затем одиночный импульс из устройства управления, поступая на шн ну 15 инекоторые входы элементов И 4, ггроходит только через те элементы И 4, другие входы которых открыты соответству юшими триггерами регистра 3, установленн ми в единичное состояние. Импульсы с выходов элементов И 4. задерживаются элеме тами задержки 5 для поочередного сдвига числа вправо (время задержки элемен;, тов 5 увеличивается слева направо) и поступают последовательно, начиная со старших разрядов, на элементы ИЛИ 6 и элементы И 8, В результате разряды числа j сдвигаются вправо столько раз, скюлько триггеров регистра 3 установлено в единичное состояние. После этого число записывается .в исправные разряды выбранной числовой линейки блока Пра смене адресов процесс распределен ния информации по исправным ячейкам по Бторяется. Режим считывания информации. По команде, при наличии кода адреса, считывается код отказа из блока 1 на регистр 3 и оперативный код из блока 2 на регистр 14. Затем одиночный импульс из устройства управле щ, доступающиг на шину 16 и элементы , :прокодит только через те элементы W7, входы которых открыты триггерам регистра 3, устаноБпенными в ед1Шйчное состоя- ние н отождествленными с отказаьш в блоKfiX. 1 и 2,. Импульсы с выходов элементов И 7 задерживаются элементами задержки 9 (вреьет задержки для каждого эпемента устанавливают тщивидуально, увеличивая справа налево) и поступают последовательно, на-« чиная с младших разрядов, на элементы ИЛИ 1О и элементы й 11. В результате разряды числа сдвигаются влево столько раз, сколько триггеров регистра 3 установлено в едтгачное состояние. После окончания cBepiKH числа влево число вьщается по шинам 17 прие - а--вь5дачк информации. Формула изобретения Оперативное запозушнаюш.ее устройство, содержащее запоминающие ; блоки, выходы од- ного из которых подключены ко входам регистра, элементы,И н ИЛИ и элементы задерж1си, отличаюшееся тем, чтс с целью повышения надежности работы и эффективной : емкости устройства оно содержит реверсив хый сдвигаютшгй регистр, первые входы которого через соотвегствующие элементы ИЛИ подключены к выходам другого запоминающего блока, выходы регист ра соединены с одними входами элеглентоэ И первой и второй групп, другие входы которых подключены к соответствующим управляющим шинам, а выходы через элементы задержки и элементы ИЛИ соединены соот ветственао с вторыми и третьими входами реверсивного сдвигающего регистра. 75 1 Щ. I 3 I 1 a ШШ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с замещениемдЕфЕКТНыХ ячЕЕК | 1978 |

|

SU803009A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Запоминающее устройство с кор-РЕКциЕй ОшибОК | 1979 |

|

SU809397A1 |

| Устройство для управления трехфазным асинхронным электродвигателем | 1990 |

|

SU1818674A1 |

| Устройство для вывода информации | 1982 |

|

SU1019429A1 |

| Устройство для выборки информации из блока памяти | 1987 |

|

SU1509982A2 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

Авторы

Даты

1976-05-25—Публикация

1975-01-15—Подача