Изобретение относится к электротехнике, и может быть использовано в медицинском оборудовании для регулирования скорости перемешивающих устройств.

Целью изобретения является повышение точности регулирования частоты вращения.

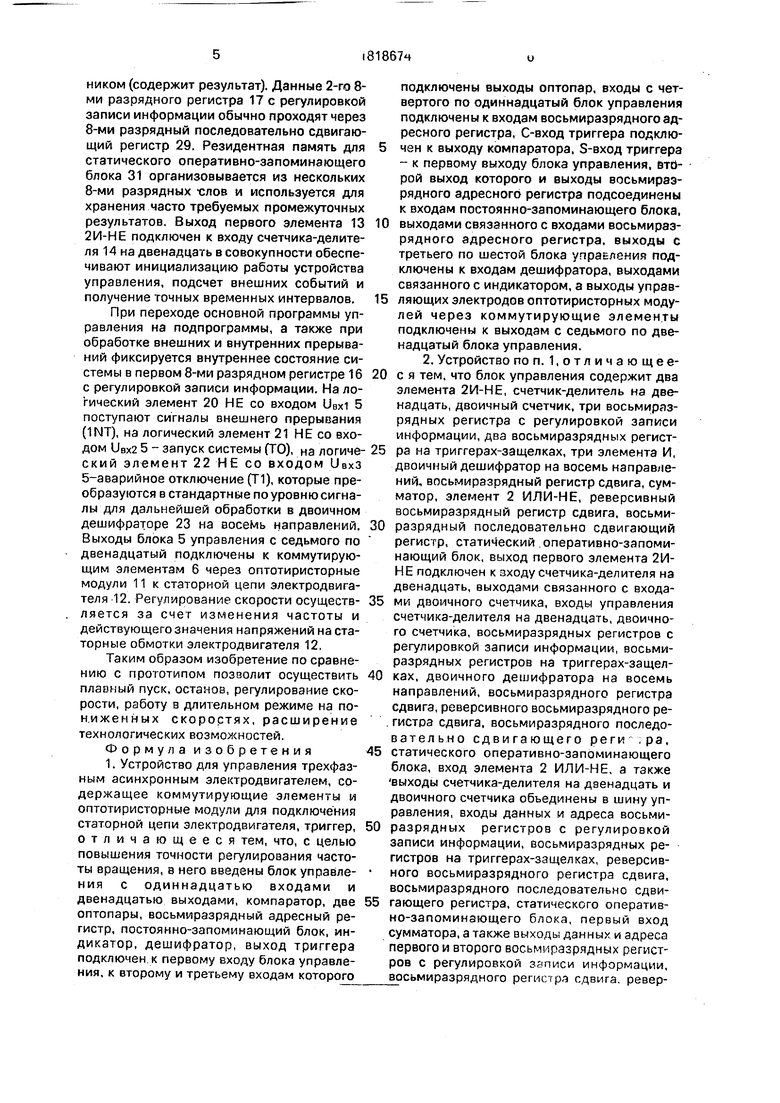

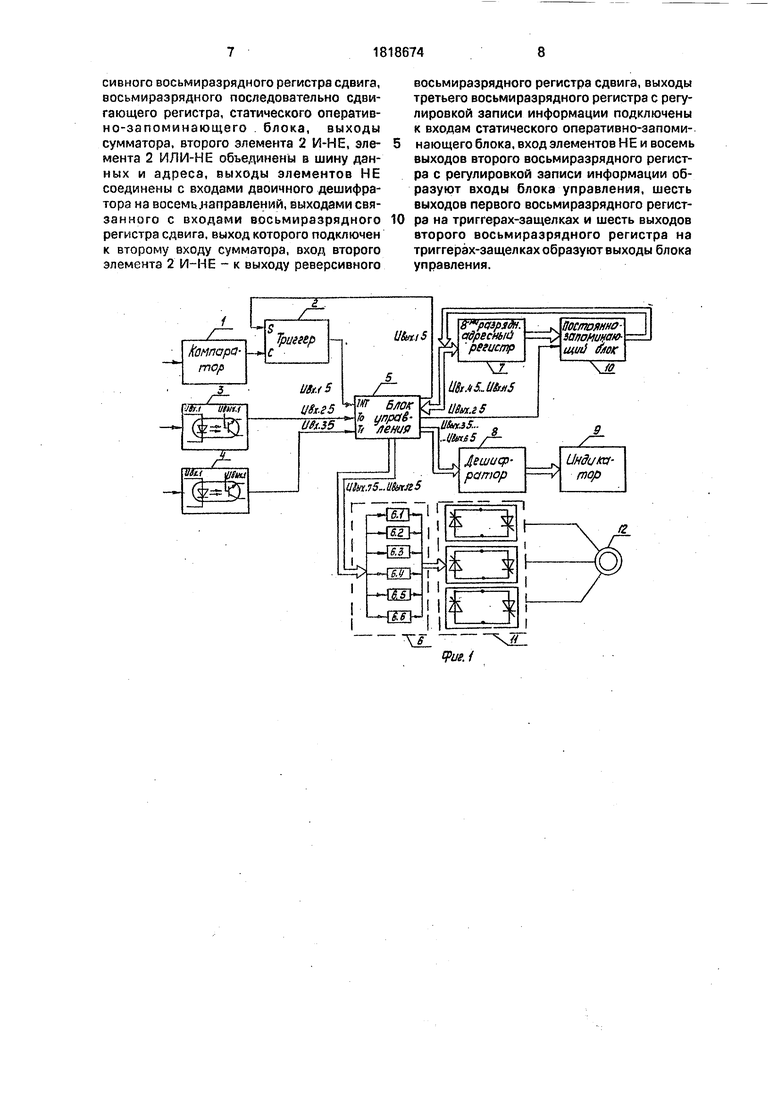

На фиг. 1 показана функциональная схема устройства для управления трехфазным асинхронным электродвигателем.

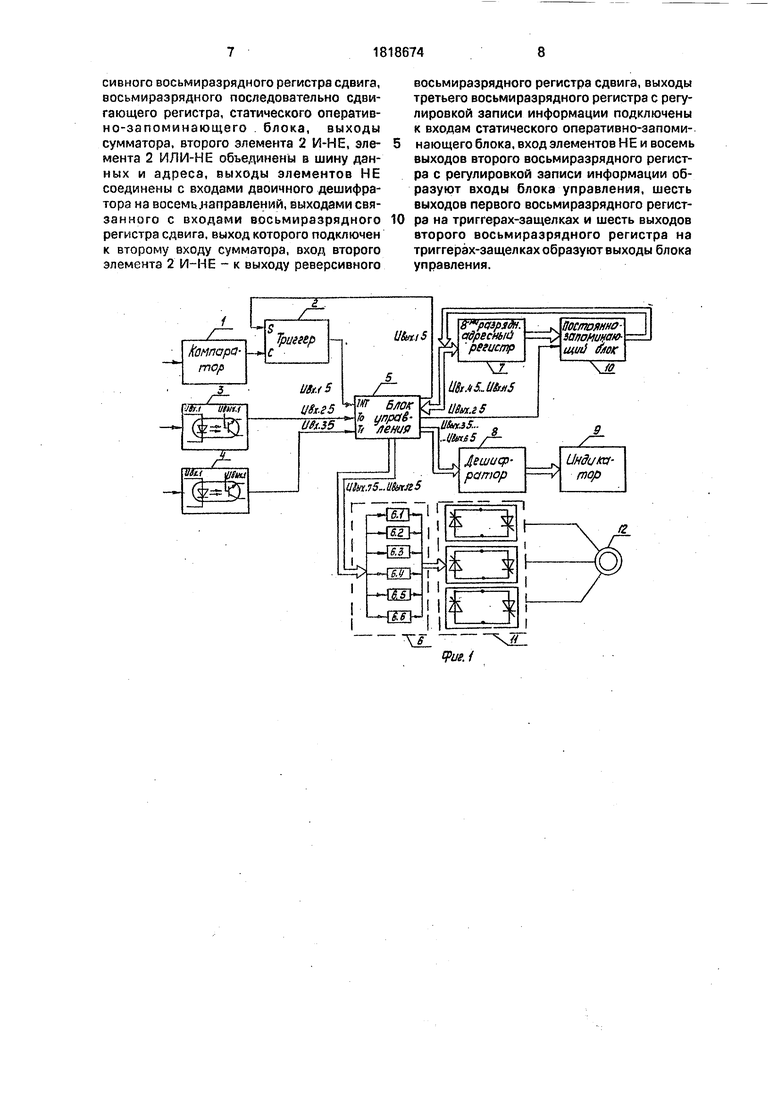

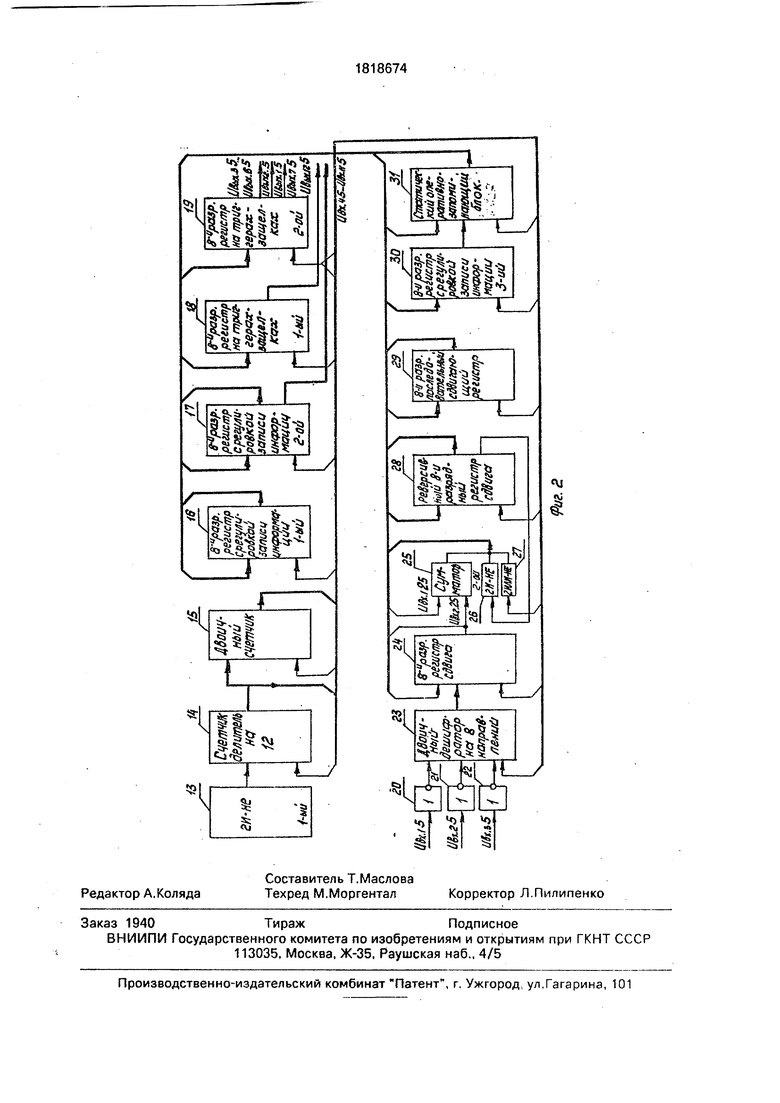

На фиг, 2 - функциональная схема блока управления асинхронным электродвигателем.

Устройство для управления трехфазным асинхронным электродвигателем содержит компаратор 1, выход которого подключен к С входу триггера 2, две оптопары 3, 4, выходами подключенными к второму и третьему входам блока 5 управления, первый вход которого соединен с выходом триггера 2. выходы с седьмого по двенадцатый блока 5 управления подключены к коммутирующим элементам 6, S-вход триггера 2 - к первому выходу блока 5 управления, входы

с четвертого по одиннадцатый блока 5 управления подключены ко входам восьмиразрядного адресного регистра 7, выходы с третьего по шестой блока 5 управления подключены ко входам дешифратора 8, выходами связанного индикатором 9, второй выход блока 5 управления и выходы восьмиразрядного адресного регистра 7 подсоединены ко входам постоянно-запоминающего блока 10, выходами связанного со входами восьмиразрядного адресного регистра 7. к .выходам коммутирующих элементов 6 подсоединены оптотиристорные модули 11 для подключения статорной цепи электродвигателя 12.

Блок 5 управления содержит первый элемент 13 2И-НЕ, счетчик-делитель 14 на двенадцать, двоичный счетчик 15, первый восьмиразрядный регистр 16 с регулировкой записи информации, второй восьмиразрядный регистр 17 с регулировкой записи информации, первый восьмиразрядный регистр 18 на триггерах-защелках, второй восьмиразрядный регистр 19 на триггерахел

с

со

ь

00

с VJ

N

защелках, три элемента 20, 21, 22, НЕ, двоичный дешифратор 23 на восемь направлений, восьмиразрядный регистр 24 сдвига, сумматор 25, второй элемент 26 2И-НЕ, элемент 27 2ИЛИ-НЕ, реверсивный восьмираз- рядный регистр 28 сдвига, восьмиразрядный последовательно сдвигающий регистр 29, третий восьмиразрядный регистр 30 с регулировкой записи информации, статический оперативно-запоминаю- щий блок 31, выход первого элемента 13 2И-НЕ подключен ко входу счетчика-делителя 14 на двенадцать, выходами связанного со входами двоичного счетчика 15, входы управления счетчика-делителя 14 на две- надцать, двоичного счетчика 15, восьмиразрядных регистров 16, 17, 30 с регулировкой записи информации, восьмиразрядных регистров 18, 19 на триггерах-защелках, двоичного дешифратора 23 на восемь направлений, восьмиразрядного регистра -24 сдвига, реверсивного восьмиразрядного регистра 28 сдвига, восьмиразрядного последовательно сдвигающего регистра 29,

статического оперативно-запоминающего

блока 31, вход элемента 27 2ИЛ1/ЖЕ, а также выходы счетчика-делителя 14 ка двенадцать и двоичного счетчика 15 объединены в шину управления, входы данных и адреса, восьмиразрядных регистров 16, 17, 30 с ре- гулировкой записи информации, восьмиразрядных регистров 18, 19 на триггерах-защелках, реверсивного восьмиразрядного регистра сдвига 28, восьмиразрядного последовательно сдвигающего регистра 29, статического оперативно-запоминающего блока 31, первый вход сумматора 25, а также выходы данных и адреса первого и второго восьмиразрядных регистров 16, 17 с регулировкой записи информа- ции, восьмиразрядного регистра 24 сдвига, реверсивного восьмиразрядного регистра 28 сдвига, восьмиразрядного последовательно сдвигающего регистра 29, статического оперативно-запоминающего блока 31, выходы сумматора 25, второго элемента 26 2И-НЕ, элемента 27 2ИЛИ-НЕ объединены в шину данных и адреса, выходы элементов 20,21,22 НЕ соединены со входами двоичного дешифратора 23 на восемь направлений, выходами связанного со входами восьмиразрядного регистра 24 сдвига, выход которого подключен к второму входу сумматора 25, вход второго элемента 26 2И-НЕ - к выходу реверсивного восьмиразрядного регистра 24 сдвига, выходы третьего восьмиразрядного регистра 30 с регулировкой записи информации подключены ко входам статического оперативно-запоминающего блока 31, вход элементов 20, 21, 22 НЕ.и восемь выходов

5 0

5

0 5 0 5 0 5

второго восьмиразрядного регистра 17с регулировкой записи информации образуют входы блока 5 управления, шесть выходов первого восьмиразрядного регистра 18 на триггерах - защелках и шесть выходов второго восьмиразрядного регистра 18 на триггерах-защелках образуют выходы блока 5 управления.

Устройство управления работает следующим образом. Каждая операция, которую выполняет блок управления идентифицируется единственным байтом информации называемым кодом команды или кодом операции. Выборка команды осуществляется следующим образом: первоначально адрес, хранящийся в двоичном счетчике 15, передается по выходу в постоянно-запоминающий блок 10, из которого адресованный байт команды возвращается в устройство управления, которое запоминает его в 8-ми разрядном регистре 24 сдвига. Код команды, записанный в 8-ми разрядном регистре сдвига поступает по 2-му выходу в сумматор 25, во второй элемент 26 2И-НЕ и элемент 272ИЛИ-НЕ.

Сумматор 25,второй элемент 26 2И-НЕ и элемент 27 2ИЛИ-НЕ выполняют арифметические и логические операции с двоичными числами: принимают 8-ми разрядные слова данных от одного или двух источников и генерирует 8-ми разрядный результат.

Сумматор 25, второй элемент 26 2И-НЕ и элемент 27 2ИЛИ-НЕ выполняют функции сложения с переносом или без него, опера ции И, ИЛИ, исключающего ИЛИ, инкремен- тирование(декрементирование содержимого регистров), циклический сдвиг влево, вправо. Если команда двухбайтовая, то первый байт, выбранный из памяти, помещается в 8-ми разрядном регистре 24 сдвига, а следующий байт - в реверсивном 8-ми разрядном регистре 28 сдвига.

Кроме того, что сумматор 25, второй элемент 26 2И-НЕ и элемент 27 2ИЛИ-НЕ вы- полняютарифметические и логические операции с двоичными числами, в нем же вырабатываются биты признаков, которые отражают условия, возникающие в процессе арифметических и логических операций. В зависимости от состояния бита признака реализуются переходы при выполнении программы. Обычно один из операндов, с которыми работает сумматор 25, второй элемент 26 2И-НЕ и 27 2ИЛИ-НЕ содержится в 8-ми разрядном последовательно сдвигающем регистре 29.

При выполнении операций 8-ми разряд-- ный последовательно сдвигающий регистр 29 является регистром-источником данных (содержит операнд) или регистром-приемником (содержит результат). Данные 2-го 8- ми разрядного регистра 17с регулировкой записи информации обычно проходят через 8-ми разрядный последовательно сдвигающий регистр 29. Резидентная память для статического оперативно-запоминающего блока 31 организовывается из нескольких 8-ми разрядных -слов и используется для хранения часто требуемых промежуточных результатов. Выход первого элемента 13 2И-НЕ подключен к входу счетчика-делителя 14 на двенадцать в совокупности обеспечивают инициализацию работы устройства управления, подсчет внешних событий и получение точных временных интервалов.

При переходе основной программы управления на подпрограммы, а также при обработке внешних и внутренних прерываний фиксируется внутреннее состояние системы в первом 8-ми разрядном регистре 16 с регулировкой записи информации. На логический элемент 20 НЕ со входом UBxl 5 поступают сигналы внешнего прерывания (1NT), на логический элемент 21 НЕ со входом Uex2 5 - запуск системы (ТО), на логиче- ский элемент 22 НЕ со входом Ивхз 5-аварийное отключение (Т1), которые преобразуются в стандартные по уровню сигналы для дальнейшей обработки в двоичном дешифраторе 23 на восемь направлений. Выходы блока 5 управления с седьмого по двенадцатый подключены к коммутирующим элементам 6 через оптотиристорные модули 11 к статорной цепи электродвигателя 12. Регулирование скорости осуществляется за счет изменения частоты и действующего значения напряжений на ста- торные обмотки электродвигателя 12,

Таким образом изобретение по сравнению с прототипом позволит осуществить плавный пуск, останов, регулирование скорости, работу в длительном режиме на по- н.иженных скоростях, расширение технологических возможностей.

Формула изобретения

1. Устройство для управления трехфазным асинхронным электродвигателем, содержащее коммутирующие элементы и оптотиристорные модули для подключения статорной цепи электродвигателя, триггер, отличающееся тем, что, с целью повышения точности регулирования частоты вращения, в него введены блок управления с одиннадцатью входами и двенадцатью выходами, компаратор, две оптопары, восьмиразрядный адресный регистр, постоянно-запоминающий блок, индикатор, дешифратор, выход триггера подключен, к перворлу входу блока управления, к второму и третьему входам которого

подключены выходы оптопар, входы с четвертого по одиннадцатый блок управления подключены к входам восьмиразрядного адресного регистра, С-вход триггера подклю- 5 чен к выходу компаратора, S-вход триггера - к первому выходу блока управления, второй выход которого и выходы восьмиразрядного адресного регистра подсоединены к входам постоянно-запоминающего блока,

0 выходами связанного с входами восьмиразрядного адресного регистра, выходы с третьего по шестой блока управления подключены к входам дешифратора, выходами связанного с индикатором, а выходы управ5 ляющих электродов оптотиристорных модулей через коммутирующие элементы подключены к выходам с седьмого по двенадцатый блока управления.

2. Устройство по п. 1, о т л и ч а ю щ е е0 с я тем, что блок управления содержит два элемента 2И-НЕ, счетчик-делитель на двенадцать, двоичный счетчик, три восьмиразрядных регистра с регулировкой записи информации, два восьмиразрядных регист5 ра на триггерах-защелках, три элемента И, двоичный дешифратор на восемь направлений, восьмиразрядный регистр сдвига, сумматор, элемент 2 ИЛЙ-НЕ, реверсивный восьмиразрядный регистр сдвига, восьми0 разрядный последовательно сдвигающий регистр, статический оперативно-запоминающий блок, выход первого элемента 2И- НЕ подключен к входу счетчика-делителя на двенадцать, выходами связанного с входа5 ми двоичного счетчика, входы управления счетчика-делителя на двенадцать, двоичного счетчика, восьмиразрядных регистров с регулировкой записи информации, восьмиразрядных регистров на триггерах-защел0 ках, двоичного дешифратора на восемь

направлений, восьмиразрядного регистра

сдвига, реверсивного восьмиразрядного ре. гистра сдвига, восьмиразрядного последовательно сдвигающего р е г и ; р а,

5 статического оперативно-запоминающего блока, вход элемента 2 ИЛИ-НЕ, а также выходы счетчика-делителя на двенадцать и двоичного счетчика объединены в шину управления, входы данных и адреса восьми0 разрядных регистров с регулировкой записи информации, восьмиразрядных регистров на триггерах-защелках, реверсивного восьмиразрядного регистра сдвига, восьмиразрядного последовательно сдви5 тающего регистра, статического оперативно-запоминающего блока, первый вход сумматора, а также выходы данных и адреса первого и второго восьмиразрядных регистров с регулировкой записи информации, восьмиразрядного регистра сдвига, реверсивного восьмиразрядного регистра сдвига, восьмиразрядного последовательно сдвигающего регистра, статического оперативно-запоминающего . блока, выходы сумматора, второго элемента 2 И-НЕ, элемента 2 ИЛ И-НЕ объединены в шину данных и адреса, выходы элементов НЕ соединены с входами двоичного дешифратора на восемь лаправлений, выходами связанного с входами восьмиразрядного регистра сдвига, выход которого подключен к второму входу сумматора, вход второго элемента 2 И-НЕ - к выходу реверсивного

восьмиразрядного регистра сдвига, выходы третьего восьмиразрядного регистра с регулировкой записи информации подключены к входам статического оперативно-запоминающего блока, вход элементов НЕ и восемь выходов второго восьмиразрядного регистра с регулировкой записи информации образуют входы блока управления, шесть выходов первого восьмиразрядного регистра на триггерах-защелках и шесть выходов второго восьмиразрядного регистра на триггерах-защелках образуют выходы блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь квадратурных сигналов | 1987 |

|

SU1550633A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

Использование: в электроприводах медицинского оборудования и перемешивающих устройств, например, крови. Сущность изобретения заключается в том, что устройство дополнительно снабжено блоком управления, компаратором, двумя опторазвязками технологических параметров .шинным формирователемадреса и данных, постоянно-запоминающим устройством, дешифратором, индикатором. 1 з. п. ф-лы. 2 ил.

2

ТЈ

фие.1

Stefifcft

t О ТЗМъ2ГЪ1

«fH

|Щ 4.

Ш

Е1Ш

J

L

ИИ8

Cr5J3

J

г

И 1ь з - с

1

и

1

S

1

5i & § .

ente

31

Ј HhSiL

S(HЈ |адЫ

°о«

Н и § §

fill И

«VJ

Ј

|

I

feftti

h

жта

1 jg i a

| Способ управления асинхронным электроприводом | 1982 |

|

SU1035767A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ управления трехфазным асинхронным электродвигателем | 1982 |

|

SU1112514A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1993-05-30—Публикация

1990-10-16—Подача