1

Изобретение относится к технике свяЗЯ; может использоваться в системах передачи данных с решающей обратной связью.

Известно устройство для зашиты от ошибок в системах связи с решающей обратной связью, содержащее на входе блок декодирования, дешифратор служебных сигналов и «входной регистр, выход которого через блок памяти приема подключен к управляющему блоку и к узлу ввода-вывода информации, выход которого через блок памяти передачи подключен ко входу блока 1код;ированиа, к которому подключен одновременно шифратор служебных сигналов.

Цель изобретения - повышение скорости передачи.

Предлагаемое устройство отличается тем, что в него введены последовательно соединенные схемы опроса, регистр резуль тата сложения, основной счетчик, счетчик адреса .проверочной комбинации, дешифратор информации и регистр состояния памяти, а также регистр ошибочной комбинации с сумматором и регистр адреса ошибочной комбинации. При этом дополнит1льные выходы блока памяти приема подключены соответственно ко входам регистра ошибочной комбинации и счетчика адреса проверочной комбинации непосредственно, а ко входу регистра результата сложения - черь;з cyhfматор; выходы регистра состояния памяти и основного счетчика подключены к соответ «ствующим входам управляющего блока, дополнительные выходы которого подключены соответственно к управляющим входам дешифратора служебных сигналов, дешифратора информации, регистра состояния памя. и и регистра адреса ошибочной комбинапик. к другому входу которого и к дополнительному входу блока памяти приема подключен выход счетчика адреса проверяемой комбинации.

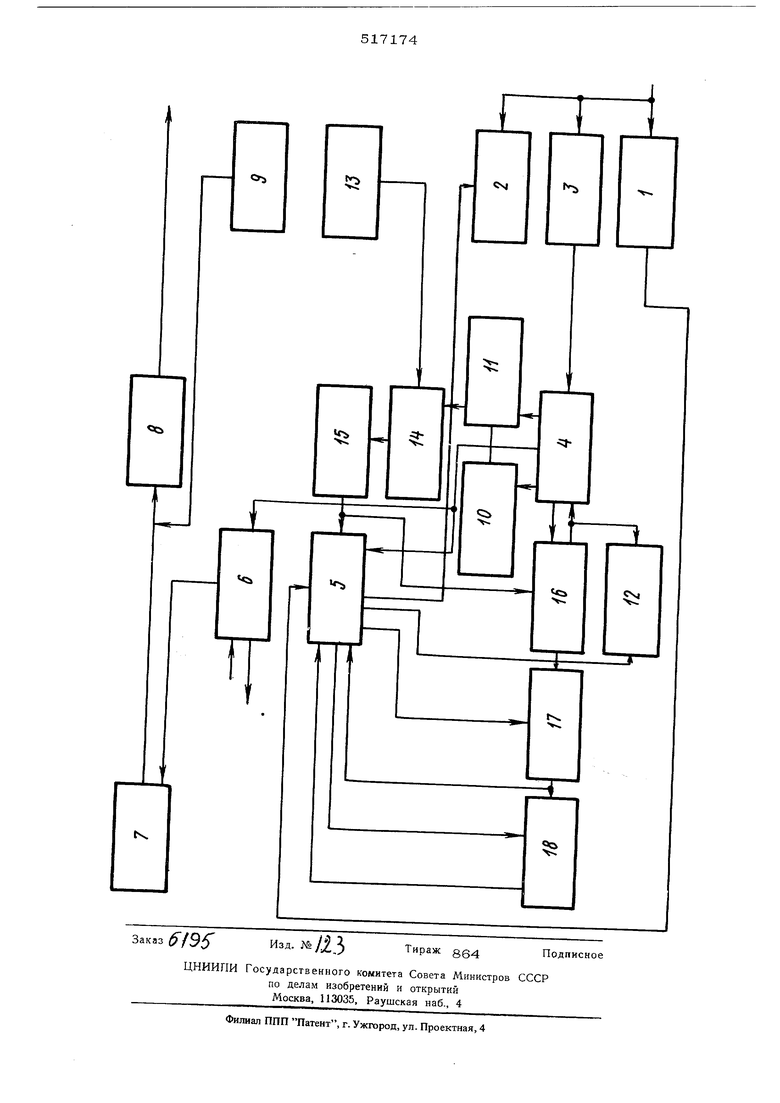

На чертеже приведена функциональная схема устройства.

Устройство содержит блок декодиробаний 1, дешифратор служебных сигналов 2 и входной регистр 3, выход которого через блок памяти приема 4 подключен к упрашгяюшему блоку 5 и к узлу ввода-вьгпода пнформаиии 6, Выход узла 6 через блок па.чштн

рает соответствующий разряд регистра состояния памяти 18. Управляющий блок 5 переводит разряд в состояние 1 и записывает ошибочную комбинацию в первую зону памяти приема, если блок памяти приема 4 не содержит ощибочных комбинаций. Если

же в блоке памяти приема есть хотя бы одна ошибочная комбинация, то вновь полученная ошибочная комбинация записывается в очередную свободную зону этого блока.

Если блок декодирования 1 вырабатывает сигнал Нет ошибки, возможны два режима работы устройства в зависимости от состояния регистра состояния памяти 18. В первом режиме при опросе регистра состояния памяти 18 управляющий блок 5 обнаруживает разряды, находящиеся в состоянии 1. В этом случае блок 5 считывает в регистр адреса ошибочной комбинации 12 содержимое регистра записи блока памяти приема 4, далее от содержимого регистра 12 вычитается единица. Дешифратор информации 17 выбирает разряд регистра состояния памяти 18 по состоянию регистра адреса ошибочной комбинации. Управляющий блок 5 проверяет этот разряд. Если он находится в состоянии 1, блок 5 считывает первое слово из зоны блока памяти приема 4 по адресу, содержащемуся в счетчике адреса проверочной комбинации 16, в регистр ощибочной комбинации 10, а затем первое слово из зоны по адресу, содержащемуся в регистре записи блока памяти приема 4. Сумматор 11 складывает эти слова по модулю два. Схема опроса 13 посылает в основной счетчик 15 число импульсов, равное числу единиц в регистре результата сложения 14. Далее считываются следующие два слова указанных зон и т. д. до тех пор, пока не считывается последнее слово зоны. Если после сложения основной счетчик 15 вырабатывает сигнал Повтор, содержимое счетчика адреса проверочной комбинации 16 переписывается в регистр адреса ошибочной комбинации Л 2.

Если основной счетчик 15 выраба ывает сигнал Повтор, разряд pefScTpa состояния памяти 18,выбранный дешифратором информации 17, переводится в состояние О. После этого управляющий-блок 5 проверяет содержимое счетчика адреса проверочной комбинации 16, Если содержимое счетчика адреса проверочной комбинации не равно нулю, из него вычитается единица и повторяется все сначала. Так происходит до тех пор, пока содержимое счетчика 16 не станет равным нулю. После этого прове ряется состояние регистра адреса ошибочной комбинации 12. Если он не находится

в исходном состоянии, управляющий блок 5 переписывает комбинацию из зоны, адрес которой находится в регистре записи блока памяти приема 4, в зону, адрес которой находится в регистре адреса ошибочной комбинации 12, который после переписи переводится в исходное состояние. При исходном состоянии регистра 12 в блоке памяти приема 4 изменений не происходит.

Во втором режиме при опросе регистра

состояния памяти 18 управляющий блок 5 не обнаруживает в нем ни одного разряда в состоянии 1. Правильно принятую комбинацию, записанную в первой зоне блока

памяти приема 4, управляющий блок 5 считывает в узел ввода-вывода информации до приема следующей комбинации.

При переполнении блока памяти приема 4, которое возможно только при наличии

в нем хотя бы одной ошибочной комбинации, управляющий блок 5 стирает все комбинации в блоке памяти приема 4, и устройство переходит в режим фазирования.

При передаче комбинации записываются

в блок памяти передачи 7 на случай их

повторной передачи. На каждую переданную комбинацию в момент времени, определяемый значением Н , ожидается сигнал обратной связи, который содержится в принимаемой комбинации. При получении сигнала обратной связи Подтверждение соответствующая ему комбинация стирается из блока памяти передачи 7. При получении сигнала Запрос соответствующая комбинация передается на повторную передачу в блок кодирования 8. Кроме того, управляющий блок 5 переписывает повторную комбинацию из своей зоны в очередную свободную зону, которая при этом помечается.

В старой зоне комбинация не стирается. Если в процессе передачи дешифратор служебных сигналов 2 обнаруживает фазовые комбинации, устройство переходит в режим фазирования. Затем управляющий

блок 5 организует выдачу комбинаций из блока памяти передачи 7, начиная с первой зоны. Комбинации из помеченных зон с меткой управляющий блок 5 стирает без передачи.

Формула изобретения

Устройство для защиты от ошибок в системах Связи с решающей обратной связью, содержащее на входе блок декодирования,

дешифратор служебных сигналов и входной регистр, выход которого через блок памяти приема подключен к управляющему блоку и к узлу ввода-вывода информации, выход которого чересз блок памяти передачи подключен ко входу блока кодировапередачи 7 подключен ко входу блока кодирования 8, к которому подключен выход шифратора служебных сигналов 9. В схему входят так регистр ошибочной комбинации 10 с сумматором 11, регистр адреса ошибочной комбинации 12 и послед о ват льно соединенные схема опроса 13, регистр результата сложения 14, основной счетчик 15,счетчик адреса проверочной комбинации 16,дешифратор информации 17 и регистр состояния памяти 18. Дополнительные выход блока памяти приема 4 подключены соответственно ко входам регистра ошибочной комбинации 10 и счетчика адреса проверочной комбинации 16 :епосредственно, а ко входу регистра результата сложения 14 - через сумматор 11. Выходы регистра состояния памяти 18, основного счетчика 15, блока декодирования 1 и дешифратора информации 17 подключены к соответствуюш;им входам управляющего блока 5, дополнительные выходы которого подключены соответственно к управляющим входам дешифратора служебных сигналов 2, дешифратора информации 17, регистра состо ния памяти 18 и регистра адреса ошибочной комбинации 12, к другому входу которого и к дополнительному входу блока памяти приема 5 подключен выход счетчика адреса проверочной комбинации 16. Устройство работает следующим образом. Комбинация с выхода дискретного канала поступает на блок декодирования 1, который проверяет принадлежность комбинации к кодовому множеству. Если принятая комбинация принадлежит к кодовому множеству, бло декодирования вырабатывает сигнал нет ошибки, в противном случае он вырабатыва ет сигнал ошибка. Входной регистр 3 накапливает слово для записи в блок памяти приема 4, хранящий все принятые комбинации, для каждой из которых выделена зона объемом в несколько слов. Дешифратор служебных сигналов 2 служит для выявления фазовой комбинации среди принятых. Сумма- тор 1 поразрядно складывает содержимое регистра ошибочной комбинации 10 и регист ра считанного числа блока памяти приема 4 и результат сложения поступает в регистр результата сложения 14. После сложения комбинаций основной сче чик 15, рассчитанный на заданное число им накапливает расстояние Хэмпульсовd между ними. Если d d , XXа счетчик 15 вырабатывает сигнал Повтор. Схема опроса 13 последовательно проверяет содержимое разрядов регистра результата сложения 14. Если проверяемый разряд находится в состоянии 1, схема опроса 13 посылает импульс в счетчик 15. Для нахождения ошибочных комбинаций с це1гью сравнения юс с правильно принятой комбинацией в счетчике адреса проБеряе--40й комбрлшции 6 формируется адрес зоны блока памяти приема 4. Регистр адреса ошибочной комбинации 12 после проверки содержит адрес зоны блока памяти приема 4, в которую необходимо записать принятую без ошибок комбинацию. В исходном состоянии регистр 12 содержит адрес последней зоны блока памяти приема 4. Если после проверки блока памяти приема 4 регистр 12 находится в исходном состоянии, принятая комбинация остается в своей зоне, иначе эта комбинация из своей зоны переписывается в зону, адрес которой содержит регистр адреса ошибочной комбинации. Дешифратор информации 17 в соответствии с состоянием регистра адреса ошибочной комбинации 12 выбирает один из разрядов регистра состояния памяти 18, каждый разряд которого соответствует зоне блока памяти приема 4. Если в зоне блока памяти приема 4 записана ошибочная комбинация, соответствующий разряд регистра состояния памяти 18 находится в состоянии 1. В противном случае он находится в состоянии О. Блок памяти передачи 7 хранит все переданные комбинации до первой неподтвержденной. Каждая комбинация хранится в зоне из нескольких слоев. Объем блока памяти передачи 7 на К комбинаций больше блока памяти приема 4, чтобы не было ее перенаполнения. Блок кодирования 8 генерирует кодовые комбинации и посылает их на вход дискретного канала. В режиме фазирования, с которого начинается работа устройства, шифратор служебных сигналов 9 посылает через блок кодирования 8 в дискретный канал фазовые комбинации. Дешифратор служебных сигналов 2, служащий для выявления фазовой комбинации среди принятых, анализирует комбинации, поступающие с выхода дискретного канала. После фазирования устройства для защиты от ошибок, находящиеся на противоположных концах дискретного канала, проводят двустороннюю одновременную передачу. Если в результате приема очередной комбинации блок декодирования 1 вырабатывает сигнал Ошибка, управляющий блок 5 записывает эту комбинацию в блок памяти приема 4. Адреса записи считываются из блока памяти приема 4 в регистр адреса ошибочной комбинации 12. Дещифратор информации 17 по состоянию регистра 12 выбиния, к которому подключен одновременно шифратор служебных сигналов, отличающееся тем, что, с целью повышения скорости передачи при высоких уровнйх ошибок в канале, в него введены последовательно соединенные схема опроса, регистр результата сложения, основной счет чик, счетчик адреса проверочной комбинации, дешифратор информации и регистр состояния памяти, а также регистр ошибочной комбинги ции с сумматором и регистр адреса ошибоч- ной комбинации, при этом дополнительные выходы блока памяти приема подключены соответственно ко входам регистра ошибочной ., комбинации и счетчика адреса проверочной i ...,комбинации непосредственно, а ко входу регистра результата сложения - через сум|матор, выходы регистра состояния памяти |и основного счетчика подключены к соответ 1ствуюшим входам управляющего блока, до1 полнительньге выходы которого подключены соответственно к управляющим входам дешифратора служебных сигналов, дешифратора информации: , регистра состояния памя- и и регистра адреса ошибочной комбинации, к другому входу которого и к дополнительном входу блока памяти приема подключен ° Bbfход счетчика адреса проверяемой комбинация.

оъ

f

NJ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Логическое запоминающее устройство | 1976 |

|

SU610174A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| СПОСОБ ПЕРЕДАЧИ СООБЩЕНИЙ В ПОЛУДУПЛЕКСНОМ КАНАЛЕ СВЯЗИ | 1996 |

|

RU2127953C1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

«о

5

«о

Авторы

Даты

1976-06-05—Публикация

1974-12-27—Подача