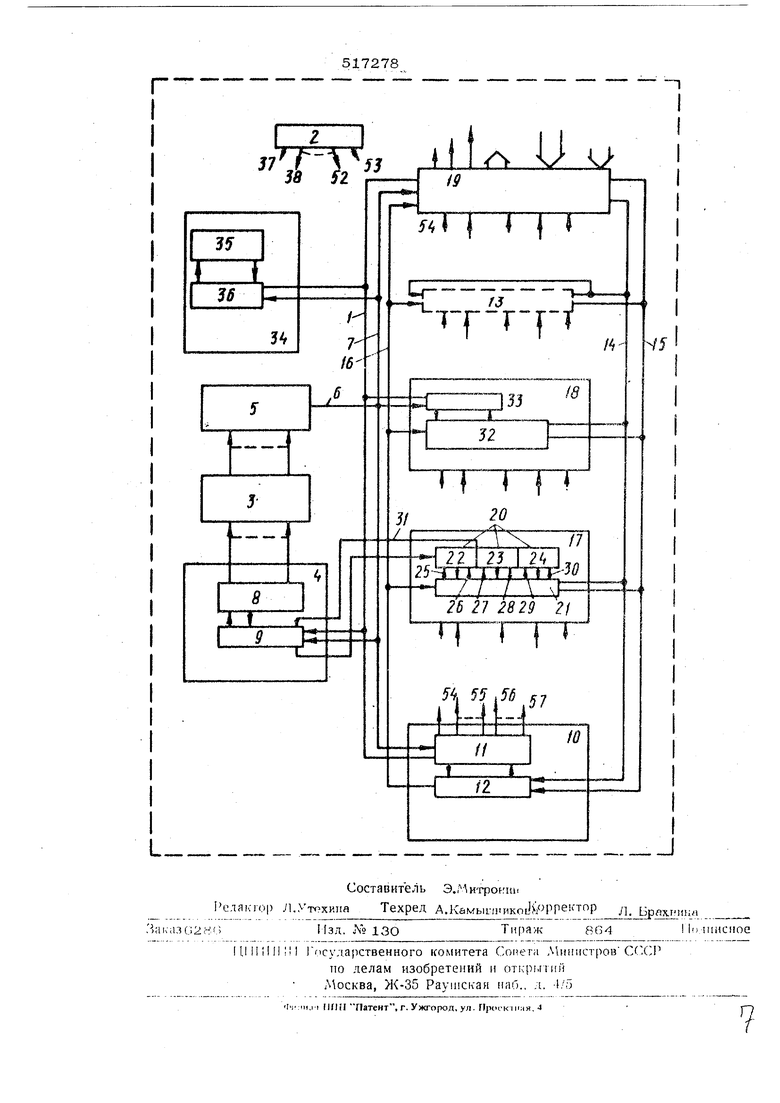

(54) ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА ДАННЫХ ДЛЯ ОБРАБОТКИ ка и с выходом логической схемы выбора регистра, а выходы подключены к соответствующему входу упомянутой логической схемы и ко второму вьзхоДу блока. Регистровое устройство содержит последователь- ногвключэнные регистры сдвига, вход и выход первого из которых соединены соответственно с первыми входом и выходом, и логическую схему, входы и выходы которой подключены к соответствующим выходам н входам регистров сдвига, ко второму входу и ко второму и третьему выходам устройства. Это ПОЗВОЛИЛИ) существенно упростить машину. Структурная схема ЦВМ приведена на чертеже, где обозначены 1.- шина ответа памяти; 2 - репе времени; 3 -считывающее запоминающее устройство (ЗУ); 4 программный блок; 5 - преобразователь параллельного кода в последовательный; 6- информационные: линии; 7 - шина ЗУ; регистр адреса 8 и логическая схема 9 блока 4; 10 - блок преобразования и выб ра регистра, состоящий из логической схе мы выбора регистра 11 и схемы сложения -вычитания 12; 13 - накопительный .регис 14 - исходная шина; 15 - шина назначения; 16 - шина; 17 - регистровое устрой ство; 18 - сумматор на накапливающем регистре; 19 - буферный накопитель; шестизначный регистр 2О и логическая схема 21 устройства 17; регистр сдвига 22 несдвигаемый регистр 23, сдвигаемый регистр 24; 25-30 - входы и выходы регио ра 20; 31 - линия; 32 - накапливающий регистр; 33 - логическая часть сумматора- 18; 34 - блок индикации, состоящий из индикаторного регистра 35 TJ лопгческ схемы 36; 37-53 - выходы реле времени 2; 54-5 7 - линии. ЦВМ предназначена для создания контрольных блоков KOMNfep4ecKorc оконечного устройства для записи финансовых деловы данных вместе с другими аналогичными оконечными устройствами TI присоединена к коллектору данных тиша центрального счетчика. Каждое устройство для записи данных информации включает коллектор данных, содер кащт1х информацию, касающуюся коммерческих деловых данных. ЦВМ работает на щестнадцатибитовом периодическом цикле, а реле времени 2 создает щестнадиать отлольных временны сигналов (выходы 37-53). За время меж ду каждой парой послояо51ателЕ1Ных ciiniaлов (на выхолы 37 и 38) создаются четыре отдельных с.игналп, имеющих v Tbipe разных фазы шбты. ЦВМ содержит интеграторы на четырехфазовых металло-оксидных полупроводниках и больших интегральных системах. В считывающем ЗУ накопленная инфор- кшация может быть считана со скоростью электронного луча 4,096 слов на 12 бит. Таким образом, ЗУ может накапливать 4, 12 бит слов, каждое из которых может быть командным сигналом или частью командного сигнала, необходимого для работы ЦВМ. ЗУ 3 смонтировано только на металло- оксидйых полупроводниках и программируется в процессе изготовления. Таким образом, ЗУ 3 содержит зафиксированную программу, которая включаетразличные командные слова, необходимые для введения в логические схемы, находящиеся в ЦВМ. ЗУ 3 по команде, полученной от сигналов, поступивших из программного блока 4, подает на преобразователь 5 серию сигналов, соответствующих логи 1еским 1 битам или. логическим О битам. Преобразователь 5 подает выходной сиГ нал ЗУ, считываемый параллельно с ЗУ 3 в качестве последовательного сигнала в линию 6, а оттуда на шину 7 ЗУ. С шины 7 ЗУ последовательный сигнал подается на ряд других блоков. Местополол ение любого из заданных командных слов, создаваемых ЗУ 3, определяется программным блоком 4, содержащим регистр адреса 8 и логические схемы 9, Регистр адреса 8 содержит счетчик, который может осуществлять любой счет от О до 4О95. Особый отсчет счетчнКа, включенного в регистр адреса 8, опред 5.пяет по.ложение в ЗУ 3, создающем командный сигнал для преобразователя 5. Так, напри гер, если отсчет в счетчике регистра адреса 8 показывает число 1,О29, то командное слово в ЗУ 3, которое располо;кено в адресе ячейки 1,О29, создает выход ЗУ 3. Сопе)- жимое счетчика в регистре адрес.:а 8 нестандартного типа yвeл rчивaGтcя на единицу I за каждый цикл. Зто значит, что после десяти сигналов времени любого заланног) цикла, которые создаются реле времени 2, счетчик регистра адреса 8 уволнчиваот свой отсчет на единицу. При поступлении соответствующих cniналов на счетчик регистра 8 из логической схемы 9 его отсчет увеличивается но послрдовательно, т. е. путем получения .гум.мьг, отличной от единицы. Это r-rioiicTiiO необходимо для ответвления iipoi p.., нл копленной в cJy 3, и .кшачсигг, что iifi л рлима (наприме)э, оснонн/ш) ...Т 6i.iT, гц.т .- дена в пoдпiJOГpaм fy для н},111Г лнеи11я цск;.ч-.)-. рых функций. Затем может быть осуществл обратный переход к основной программе. Назначение этой операции - сохранение объ ма ЗУ 3 и недопущение его значительного расширения. Счетчик регистра адреса 8 хранит отсчет более, чем один цикл, в слу чаях, когда время, необходимое для выполнения команды, более, чем один цикл. ЦВЛ содержит регистры различного типа, к которым и из которых поступает информация в виде восьмибитовых кодовых символов. Регистры должны быть выбраны , в соответствии с сигналами, поступающими из блока преобразования и выбора регистра 1О, включающего в се.бя логическую схему выбора регистра 11 и схему сложения и вычитания 12. Логическая схема- выбора регистра 11 декодирует код в битах 0 до Ь специального сигнала команды, подан ного для того, чтобы определить, откуда ис : ходит.-состветстЕгуюишя командз. После того как команда определена, рещается кодовый сигнал Д кода и О кода, и сигналы подаются в линии 54-57. Линии подсоединены к каждому регистру Ю, который должен быть выбран. Сигнал появляется на одной из 54, 55 и на одной из линий 56, 57. ЦВМ содержит три специальных типа регистров, которые включены в схему. ЦВМ имеет от О до трингадцати накопитель ных регистров, которые следует выбирать. Число накопительных регистров 13 определяется назначением ЦВМ. Каждый регист 13 может иметь один илиболее символов, которые определяются 8 двоичными битами. Каждый регистр 13 имеет два выхода, на которые последовательно на бит, подаются наиболее значимые позиционные символы (последний значимый символ - на -первый бит). Один выход регистра . 13 присоединен к исходной шине .14, другой - к шине назначения. 15. Если логическая, схема выбора регистра 11 выбирает регист 13 в качестве начального регистра путем подачи сигналов на лини.и 56 и 57, присоединенные к регистру, то любой символ, который выводится из этого регистра, подается на сходную шину 14. Если логи. ческая схема регистра 11 выбирает регистр J.3 в качестве регистра назначения путем подачи сигналов на линии 54 и 57, присОЛииенные к тегистру, то .пюбой символ, который выполится из этото регистра, подается на шину назнпчения 15. Выход каждого роглсгра 13 на исходную шину Н 1исоединен но вход pc riiciija но типу связи. Токим образом, еслц рогист|| 13 BFii6ij;ii в к;1Ч(стг.о начального регистра, то выходной сигнал, поданный на исходную щину 14, также подается на вход регистра и становится его последним значИ мым символом. Регистр 13 действует в этом случае как цир кулярный регистр сдвига. Это означает, что когда символ в ре.гистре 13 попадает в исходную шину 14, каждый из оставшихся символов в регистре увеличивается в значении положения, и символ, поданный в исходную щину 14, устанавливается в. последнем значимом символе положения регистра. Второй вход каждого регистра 13 связан с щиной 16, где происходят арифметические операции, и которая связана с ны.ходом схемы сложения и вычитания 12. Регистр 13, который выбран в качестве регистра назначения, при сигнале, п.оявляющемся в шине 16. накапливает в последнем значащем символе положения информацию, обнаруженную этим cvIГнaлoм. Исходная щина 14 и шина назначения 15 являются входами схемы сложения и вычи.тания 12. Эта схема при сигналах из л: гической схемы выбора регистра 3 1, выполняет сложение, вычитание или перевод информации, появляющейся в исходной шино 14 и шине назначения 15, в шипу 16, гдо происходят арифметические операции. ЦВМ содержит также три специа.аьных регистра. Они включают регистровое уст ройство 17, суммирующее устройство 18 и входной. буферный накопитель 19, включающий ycTpofiCTBo ввода и вывода сигналов. Каждый из этих регистров также может быть выбран начальным perncTpONf или регистром назначения по сигналам с логической схемы выбора оегистра 11. Регистровое устройство 17 включает в себя шестизначный регистр 20 и логические схемы 21. . Регистр 2О включает двухзначный регистр сдвига 22, двухзначный несдвигаемый регистр 23, который может создавать два символа одинакового значения по одной команде, и двухзнач н п1 сдвигаемьнЧ регист) 24. Для получения информации с одного из регистров 22, 23 или 24 сигнал, полученный из логической схемы 21, показывает, акой из символов и какой из регистров олжен быть использован в заданном поожении, Два положения дв}х символов етистра 22 обозначают и естой и пятый имволы регистра 2О; два символа региста 23 являются четвертым и третьим симолом, и два символа регистра 24 - втоым и первьгм СИМГЗО.ЛОМ. Входы и выходы 25-30 соответственно оединены с CHNfB-,)naMH в регистре 2О и

лог 1ческой схеме 21. Если требуется более значимый символ регистра 22, сигнан будег на выходе 25. который связан с шестой позицией символа, тогда как на оставшихся выходах сигнала нет. Это создает наиболее значимый символ регистра 22, который должен быть подан на уставов, ленную i чeйкy, Аналогично, если требуется менее значимый символ регистра 23, сигнал появляется на выходе 28, тогда

как на оставшихся пяти указательных стрел ках сигнала нет. При этом последний значимый символ регистра 23 подается в соответствующую ячейку.

Регистры; реагуфуют на сигналы с выходов и входов 25-30, указываюшие пере вод их накопленного содержания в логическую схему 21, и откуда они могут быть поданы на шину 14 или 15.

Два положения символа регистра 22

могут быть использовань для накопления двенадпатибитового сигнала, указывающего адрес для ЗУ 3. Двенадцать битов накапливаются следующим образом: биты -j до) л накапливаются в менее значимом положении

символа регистра :22, а биты fcg ДО в четырех менее значимых положениях би- тов более значимых положений;символов регистра 22, Четыре наиболее значимых положения битов более значимых симво- лов регистра 22 не используются. По команде регистр ,22 через линию Й1 сдвигает двенадцать накопленных в нем битов в программный блок 4 и вводит их. в качестве адреса в регистр адреса 9. Регистр 22 может быть использован также в качестве нормального двухзначного запоминающего регистра, и с этой целью он может подавать сигналы через логическую схему 21 к исходной щине 14 или шине назначения 15 и может реагировать на сигнапы, появляющиеся в шине 16, где происходят арифметические операции, которые подаются туда через логическую схему 21.

I

Регистр 23 может быть использован

в качестве регистра i адреса устройств обработки специальных данных информации, частью которых является ЦВМ. Этот регистр не является регистром сдвига, а скорее триггерным регистром, который; может создавать шестнадцать битов команды, закодированной вне программы. Регистр 23 может подавать свою закодированную информацию через логическую схекту 21 и не; ходную ;ииму 14 или шину назначения 15 в зависимости от того, Е ыбран регистр 2О

Б качестве начал()Ного регистра пли регигтра назначения .Он но реагирует па Jiio6bfu сшналы,по5и№ЯЮ1; иеся в тине 16.

Регистр 24 может быть использоьан в качестве хронирующего счетчика времени, необходимого для подсчета определенного времени, например, в случае, когда необходима короткая выдержка. Это касается двухзначного, следовательно, щестнадцатибитового сдвигового регистра.

Регистр 24 реагирует на сигналы, появившиеся в шине 16, где производятся ариметические операции, поступившие в шину логической схемы 21. Один раз за цикл отсчеТ:В регистре 24 уменьшается на единицу, пока не достигнет нуля. Для того чтобы определить когда отсчет достигнет нуля, необходим периодический выборочный контроль регистра 24.

Сумматор 18 содержит однозначный накапливающий регистр 32 и объединенный логический контур 33. Регистр 32 может быть выбран логической схемой 11, как исходный регистри ш же как ре истр назначени и будет в дальнейшем вь.итолнять функцию ргистра суммировоиия. Кроме того, регистр 32 всегда выбирается Б качестве регистра назначения, когда в шине памяти 7 создаются командные сигналы и регистрируются логической схемой выбора регистра 11, Например, при переходе информации из од ного блока преобразования и выборе регист ра 1О информация также поступает в накапливающий регистр 32. Преимуществом по. стоянного выбора накапливающего регистра 32, реагирующего на сигналы в шине 16, когда на щину памяти 7 подань командные сигналы, является возможность накаплива- ния этих команд в ЗУ 3. Без этого устройства- при необходи,гости передвинуть символ из одного регистра 13 в другой регистр 13 и затем проконтролировать символ в суммирующем устройстве с целью определения его величины, требуется ряд команд: передвинуть символ в регистр, затем сдвинуть регистр, передвинуть его в суммирующее устройство и вновь сдви|нуть регистр и, наконец, проконтролировать символ.

В предлагаемом устройстве необходимо только передвинуть символ в регистр, и он атоматически попадает в сумматор 18 н готов для контроля.

Логическая часть 33 сумматора 18 рассчитана так, чтобы было возможно распознать коды, указывающие определенные команды.

Последним регистром, который мОжет быть выбран логшеской схемой выбора регистра 11, является буферн 1й регистр ввода и вывода, являющийся составной честью блоков ввода и вывода сигнала буферпэго накопителя 19, Этот регистр используется для промежуточного преобраэо вания данных, подаваемых в ЦВМ, Информация, поданная в буферный регистр, долж на быть информацией, содержащей данные или статус-информацию, поступающую из дополнительного отвода. Информация посту пает на определенный буферный/регистр только благодаря реагированию на соответ ствующую команду. Логические средства входят в состав средств ввода и вывода сигнала буферного накопителя 19 и заставляют средства вво да и вывода реагировать на соответствующие коды, Сигналы команды подаются в шину памяти 7. Выход буферного регистра в средствах ввод-вывод присоединен к шинам 14 и 15. Блоки ввода-вывода сигнала буферного накопителя 19 имеют четыре отводных вы борочных линии, которые соответственно соединены с периферийными блокамиу связанными схематически с ЦВМ. При появлении сигнала на одной из пк НИИ дополнительный отвод, к которому подается этот сигнал, находится под контролем ЦВМ, Блоки ввода-вывода сигнала буферного накопителя 19 имеют выходы, необходимые для приема шестнадцати сигналов, приходяших с периферийных блоков, соединенных с дополнительными отводами. Регистр блока индикации 34 не контролируется логической схемой выбора регист ра 11. Блок индикации 34 содержит простой индикаторный регистр 35 и соответствующую логическую схему 36, Блок индикации 34 реагирует на определенные кодовые сигналы, подаваемые с шины памяти 7, Один сигнал может бытв использован для того, чтобы один или более битов в регистре 35 перешли от логическо- то О до логической 1, а другой - для того чтобы один или 6oliee битов в регистре 35 перешли от логической 1 до ло- гического О, Следующий кодовый сигнал может быть использован для проверки значения одного или более битов в регистре 35 и. затем отделить или продолжить программу в зависимости от результатов проверки. Программный блок 4 реагирует на код, необходимый для команд, создаваемых в шине памяти 7, Шина ответа памяти 37 принимает сигналы из блока индикации 34, из блока средств ввода и вывода буферного накопителя 19, из сумматора 18 и с логической схемы выбора регистра 11, Затем эти сигналы подаются на логическую cxeNiy 9 в программном блоке 4. Сигналы, поданные в шину памяти 7, являются простыми IIM -пульсными сигналами, получаемыми в заданное время. Реакция программного счетчика 4 на сигнал, появ,аяюшийся в шине оч-вета памяти 1, определяется временем, в течение которого сигнал подается на эту шину. Время, в течение которого появляется импульс на шине ответа памяти 1, опр деляет, какое последовательное действие должно быть предпринято логическими схемами 9 в ответ на определенную команду, Все блоки, работаюшие по сигналам команды, соединены с шиной ответа памяти 1 через простой транзистор. При работе определенных блоков по сигналу, поступившему в шину ответа памяти 1, транзистор устанавливается на определенное время. При этом только один транзистор в активен в любое заданное время , .Исходная шиная 14 и шина назначения 15 используются для выборочных регисторов. Имеется пять возмол ных ответов на сигналы, находящиеся на шине ответа памяти 1, Логические схемы построены на полупроводниках, поэтому расчет времени не может быть описан в значениях временнь х битов. Формула изобретения 1, Цифровая вычислительная машшш для обработки данных, содержащая устройство управления, сумматор на накапливающем регистре с подключенной к нему логической схемой, считыБающее запоминающее устройство, входы которого соединены с выходами программного блока, состоящего из регистра адреса и подключенной к нему логической схемы, а выходы подключены к cooтвeтcтвyюlци входом преобразователя параллельного кода в последэвательный, блок индикации, состояший из индикаторного регистра и- подключенной к нему логической схемы, и буферный накопитель, первый вход которого соединен с выходом преобразователя параллельного кода в последовательный, с пepвы f входом логической схемы программного блока и со входами логических схем сумматора и блока индикации, а первый выход подключен ко втор- му входу логичоскрй схемы программного блока и к выходам логических схем сумматора и блока индикации, о т л и ча ю щ а я с я тс;м,что, сце,аьюупрошрния машины, она содержит блок преобразования и выбора регистра, первые вход и выход которого оединены соответственно с первыми входoIv. и выходом буфсрног 5 1{ак(1гтСЛЯ, о ист- ровое устройстьс, перга.о иход к котс.рогого полюючекы coovi:,eTCr -.c;7;i;o к тгорвоку и

11

третьему входам логической cxeNfbJ nporpawL много блока, и группы накаппивающих регистров, первые входы и выходы которых соединены лежду собой, а вторые входы подключены ко второму выходу блока преобразования и выбора регистра, ко вторым входам Буферного накопителя и регистрового устройства и ко входу накапливающего регистра сумматора, второй и третий выхо ды буферного накопителя соединены соответственно со вторым и третьим входами блока преобразования и выбора регистра, со вторым и третьим выходами регистрового устройства и с соответствующими выходами накапливающего регистра суммато.ра и группы накапливающих регистров. ;

2. ЦВМ по п. 1, о т л и ч а ю ш а 4 с я тем, что в ней блок преобразования и выбора регистра содержит присоединен12

ную к его первым входу и выходу лопгческую схему выбора регистра и схему сло жекия-вычитания, входы которой соединены

соответственно со вторым и третьим выходами блока и с выходом логической схемы выбора регистра, а вьгходы подключены к соответствующему входу упомянутой логической схемм и ко второму выходу блока.

3. ЦВМ по п. 1, отличающаяс я тем, что в ней регистровое устройство содержит последовательно включенные регистры сдвига, вход и выход первого из которых соединены соответственно с первыми входом и выходом, и логическую схему, входы и выходы которой подключены к соответствующим выходам и входам регистров сдвига, ко второму входу и ко второму и третьему выходам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Устройство для реализации логических функций | 1977 |

|

SU732878A1 |

| Устройство для ввода информации в ЭВМ | 1982 |

|

SU1043620A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

Авторы

Даты

1976-06-05—Публикация

1971-09-13—Подача