(54) УСТРОЙСТВО ПОЭЛЕМЕНТНОГО ФАЗИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство для синхронизации приемника телеграфных сигналов | 1980 |

|

SU970715A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1984 |

|

SU1160444A1 |

| Анализатор занятости канала связи | 1984 |

|

SU1225021A1 |

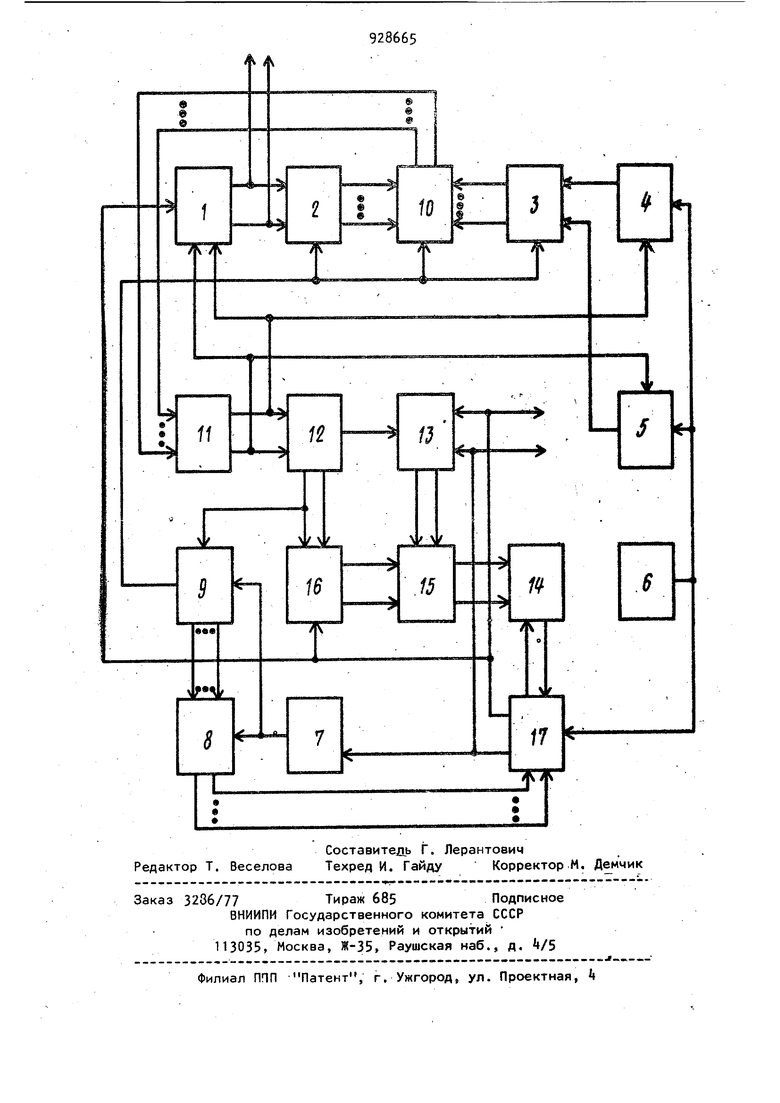

Изобретение относится к передаче дискретных сообщений и может быть использовано для обеспечения тактовой синхронизации приемной части аппаратуры. Известно устройств поэлементного фазирования, содержащее два реверсивных счетчика, два элемента И, формирователь фронтов сигналов, выход которого подключен к информационному входу интегратора, а также последовательно соединенные блок управления и управляемый делитель, к второму входу которого подключен выход задающего генератора, а первый выход управ ляемого делителя подключен к первому тактовому входу фазового дискриминатора и входу делителя, выход которого подключен к управляющему входу дешифратора, ко входам которого подключены выходы интегратора, а выходы дешифратора подключены к управляющим входам, управляемого делителя, второй выход которого подключен к тактовому входу блока управления l. Однако извecfнQe устройство обладает низкой помехоустойчивостью. . Цель изобретения - повышение поме хоустойчивости. Цел достигается тем, что устрой- ство поэлементного фазирования, сод жащеё-одва реверсивных счетчика, два элемента И, формирователь фронтов сигналов, выход которого подключен к информационному входу интегратора, а также последовательно соединенные блок управления и управляемый делитель, к второму входу которого подключен выход задающего генератора, а первый выход управляемого делителя подключен к первому тактовому входу фазового дискриминатора и входу делителя , выход которого подключен к управляющему входу дешифратора, ко, входам которого подключены выходы интегратора, а выходы деши(}(1эатора подключены к управляющим входам управляемого делителя, второй выход которого подключен к тактовому входу блока управления, введены преобразователь сигналов, блок регистрации, эычитающий блок, блок защиты регистрации и усредняющий блок, выходы которого подключены к суммирующему и вычитающему входам блока управления, а к первым и вторым суммирующим и вычитающим входам усредняющего блрка подключены соответственно выходы фа-; зового дискриминатора и блока защиты /регистрации, к тактовому входу которого, а также к тактовому входу блока регистрации и второму тактовому входу фазового дискриминатора подключен третий выход управляемого делителя, при этом к информационному входу фазового дискриминатора подключен второй выход формирователя фронтов сигналов, первый и третий выходы которого подключены соответственно к первому и второму входам блока защиты регистрации., а выход задающего генератора подключен к первым входам первого и второго элементов И, при этом первый выход преобразователя сигналов подключен к первом.у. входу формирователя фронтов сигналов, первому информационному входу блока регистрации и второму входу первого элемента И, а второй выход преобразователя сигналов подключен к второму входу формиров,ателя фронтов сигналов, второму входу второго элемента И и второму информационному входу блока регистрации, выходы которого подключены к суммирующему и вычитающему входам первого реверсивного счетчика, выходы которого Иодключены к соответствующим входам вычитающего блока, при этом выходы первого и второго элементов И подключены соответственно к суммирующему и вычитающему входам второго реверсивного счетчика, выходы которого подключены к другим соответствующим входам вычитающего блока, выходы которого подключены к управляющим входам преобразователя сигналов , а к сбросовым входам первого и второго реверсивных счетчиков, а также к управляющему входу вычитающего блока подключен соответствующий выход интегратора, к сбросовому входу .которого подключен выход делителя. На чертеже представлена структурная схема устройства. Устройство поэлементного фазирования содержит блок 1 регистрации, пер954 вый реверсивный счетчик 2, второй реверсивный счетчик 3, элементы И t и 5, задающий генератор 6, делитель 7, дешифратор 8, интегратор 9, вычитающий блок 10, преобразователь 11 сигналов, формирователь 12 фронтов сигналов, фазовый дискриминатор 13, блок управления , усредняющий блок 15, блок 16 защиты регистрации, управляемый делитель 17. Устройство работает следующим образом. Задающий генератор 6 формирует импульсы высокой частоты, вследствие чего на первом и третьем выходах управляемого делителя 17 формируются с частотой, близкой к скорости передачи (скорости телеграфирования),две импульсные последовательности, сдвинутые друг относительно друга на полоВину периода следования. Одновременно с этим на выходах преобразователя 11 сигналов формируются прямая и инверсная последовательности принимаемых элементов сообщения, а передние и задние фронты принимаемых элементов сообщения со второго выхода формиро- . вателя 12 фронтов сигналов поступают на информационный вход фазового дискриминатора 13. Фазовый дискриминатор 13 осуществляет сравнение фаз принимаемых элементов сообщения с 4)азой тактовых импульсов и в случае их несовпадения формирует корректирующие импульсы добавления или вычитания, которые поступают на первый суммирующий или вычитающий вход усредняющего блока 15, осуществляющего защиту устройства поэлементного формирования от ложной подстройки частоты при случайных искажениях в канале связи принимаемых элеме+нтов сообщения. . Усредненные корректирующие сигналы поступают на суммирующий или вычитающий входы блока 1 управления, вследствие чего производится подстройка фазы и частоты следования тактовых импульсов на выходе управляемого делителя 17. Шаг подстройки (шаг дискретизации) тактовой частоты устанавливается путем включения блока 14 управления между соответствующими разрядами управляемого делителя 17, причем место включения блока 1 управления определяется кодом числа на выходе дешифратора 8,- т.е. числом передних фронтов (средней частотой .чередования единичных и нулевых элементов принимаемого сообщения или их групп), поступивших на интегратор 9 13а промежуток между двумя сбросовыми импульсами на выходе делителя 7, коэ фициент пересчета которого определяет моменты ввода информации в дешифратор 8. Кроме того, прямая и инверс ная последовательности принимаемых элементов, сообщения с выходов преобразователя 11 сигналов поступают на входы блока 1 регистрации и вторы входы элементов И и 5 на первые входы которых поступают импульсы вы сокой частоты с выхода задающего генератора 6. На первом и втором выходах блока 1. регистрации формируются импульсы, соответствующие поступлени единичного или нулевого элемента при нимаемого сообщения, которые поступают соответственно на суммирующий и вычитающий входы первого реверсивн го счетчика 2, вследствие чего в первый реверсивный счетчик 2 записывается некоторое число, равное разности единичных и нулевых элементов принимаемого сообщения за промежуток времени между поступлениями импульсов на его сбросовый вход. Ана логичным образом во второй реверсивный счетчик 3 записывается число, которое характеризует разность едини ных и нулевых элементов принимаемого сообщения и разность длительностей отдельных единичных и нулевых элементов (величину преобладаний токовых и бестоковых элементов принимаемого сообщения) за тот же промежуток времени. Ввод информации в вычитающий блок 10 как и сброс реверсивных счетчиков 2 и 3 производится сигналом с выхода соответствующего разряда интегратора 9, т.е. промежуток времени, за который регистрируются показания реверсивных счетчиков 2 и 3, изменяется в зависимости от частоты чередования единичных и нулевых элементов в принимаемом сообщении . Вычитающий блок 10 обеспечивает сравнение чисел (с учетом удельного веса их разрядов), записанных в реверсивные счетчики 2 и 3, формирует на выходе код числа, который характеризует величину преобладаний прини маемых элементов сообщения. Сигналы с выхода вычитающего блока 10 поступают на управляющие входы преобразователя П сигналов, изменяя порог срабатывания его порогового элемента вследствие чего изменяется величина преобладаний единичных и нулевых 5 элементов на выходах преобразователя 11 сигналов. При первоначальном включении аппаратуры или после длительных перерывов в работе канала связи при наличии преобладаний возможна ошибочная установка стробирующего импульса, при которой блок 1 регистрации производит ошибочную регистрацию принимаемых элементов сообщения. Подстройка фазы тактовых импульсов посредством фазового дискриминатора 13 при больших преобладаниях затруднена. Поэтому функции грубого вывода стробирующего импуЛьса в правильное положение в этом случае осуществляет блок 16 защиты регистрации, который проверяет правильностьчередования между собой переднего фронта стробирующего импульса и заднего фронта принимаемого элемента сообщения. На выходах блока 16 защиты регистрации .в случае ложной синхронизации в зависимости от, вида преобладаний формируются импульсы добавления или вычитания, которые через усредняющий блок 15 и блок 14 управления воздействуют на управляемый делитель 17, изменяя фазу его выходных импульсов. Таким образом, устройство поэлементного фазирования обеспечивает повышение помехоустойчивости и .достоверности приема информации системой передачи сообщений в целом, так как регистрации подлежат элементы принимаемого сообщения, длительность которых откорректирована. формула изобретения Устройство поэлементного фазирования, содержащее два реверсивных счетчика, два. элемента И, формирователь фронтов сигналов, выход которого подключен к информационному входу ин« тегратора, а также последовательно соединенные блок управления и управляемый делитель, к второму входу которого подключен выход задающего генератора, а первый выход управляемого делителя подключен к первому тактовому входу фазового дискриминатора и входу делителя, выход которого подключен к управляющему входу дешифратора, ко входам которого подключе ш выходы интегратора,- а выходы дешифратора под ключены к управляющим входам управляемого делителя, второй выход которого подключен к тактовому входу блока

управления,отличающееся тем, что, с целью повышения помехоустойчивости, введены преобразователь сигналов, блок регистрации, вычитающий блок,блок защиты регистрации1, и усредняющий блок, выходы которого подключены к суммирующему и вычитающему входам блока управления, а к первым,и вторым суммирующим и вычитающим входам усредняющего блока подклю-10 к

чены соответственно выходы фазового дискриминатора и блока защиты регистрации, к тактовому входу которого, а также к тактовому входу блока регистрации и второму тактовому входу фазо- IS вого дискриминатора подключен третий выход управляемого делителя, при этом к информационному входу фазового дискриминатора подключен второй выход . формирователя фронтов сигналов, пер- м вый и третий выходы которого подключены соответственно к первому и второму входам блока защиты регистрации, а вывыход задающего генератора подключен к первым входам первого и второго эле-25 ментов И, при этом первый выход преобразователя сигналов подключен к с первому входу формирователя импульсов, первому информационному входу блока регистрации и второму входу первого

элемента И, а второй выход преобразователя сигналов подключен к второму входу формирователя фронтов сигналов, второму входу второго элемента И.и второму информационному входу блока регистрации, выходы которого подключены к суммирующему и вычитающему входам первого реверсивного счетчика, выходы которого подключены

блока, при этом выходы первого и второго элементов И подключены соответственно к суммирующему и вычитающему входам второго реверсивного счетчика , выходы которого подключены к другим соответствующим входам вычитающего блока, выходы которого подключены к управляющим входам преобразователя сигналов, а к сбросовым входам первого и второго реверсивных счетчиков, а также к управляющему входу вычитающего блока подключен соответствующий выход интеграторов, к сбросовому входу которого подключен выход делителя.

Источники информации, принятые по внимание при экспертизе

Авторы

Даты

1982-05-15—Публикация

1980-05-12—Подача