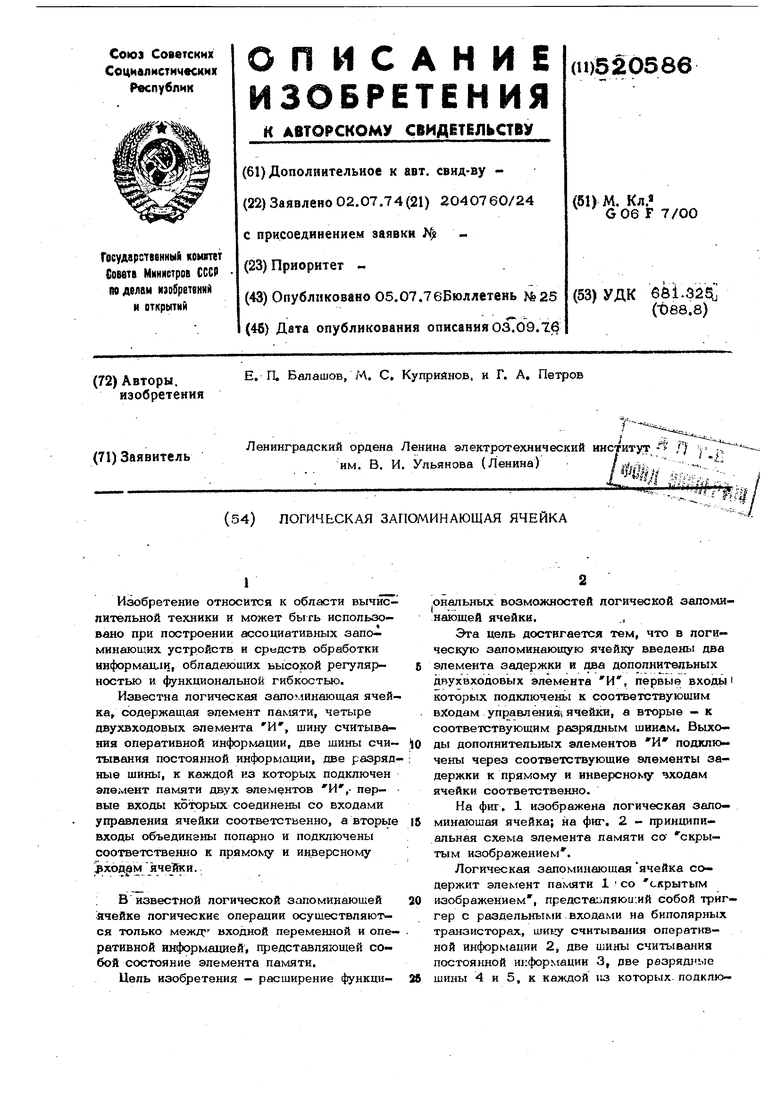

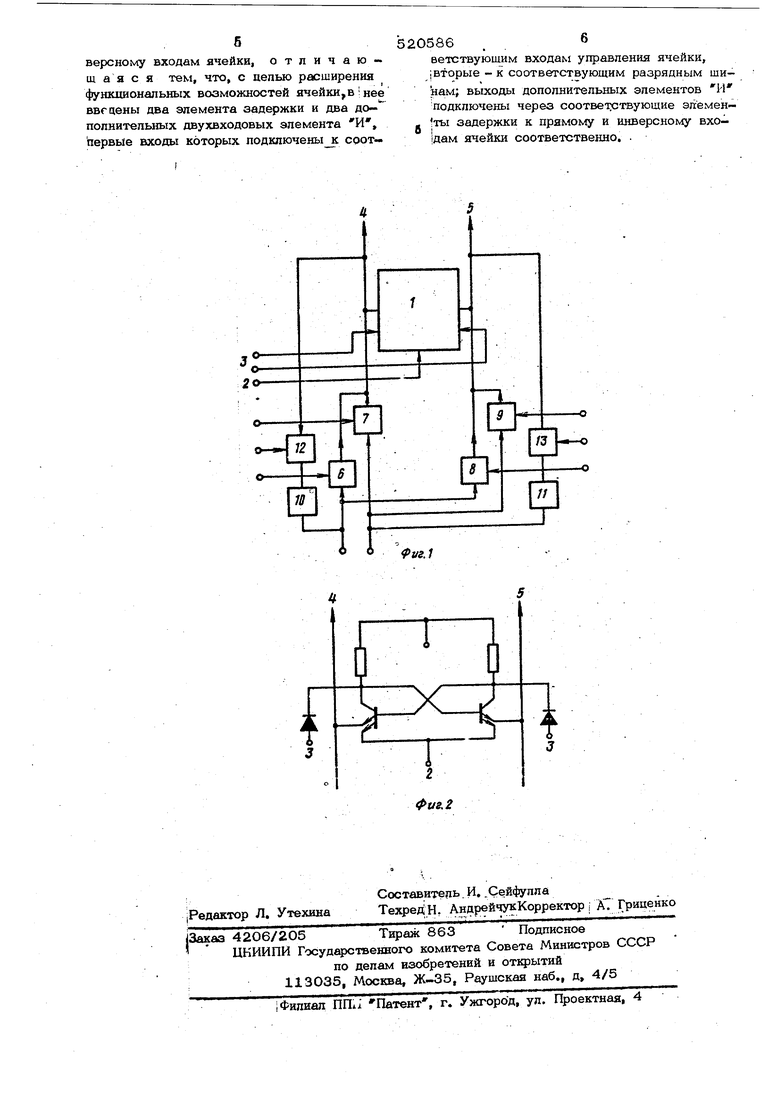

Изобретение относится к области вычйс питепьной техники и может быть использовано при построении ассоциативных запоминающих устройств и средств обработки информаДлШ, обладающих высокой регулярностью и функциональной гибкостью. Известна логическая запоминающая ячей ка, содержащая элемент памяти, четыре двухвходовых элемента И, шину считывания оперативной информации, две шины счи тывания постоянной информации, две разряд ные шины, к каждой из которых подключен элемент памяти двух элементов И,- первые входы Kotopbix соединены со входами управления ячейки соответственно, а вторые входы объединены попарно и подключены соответственно к прямому и инверсному jpxofl M ячейки. ; в известной логической запоминающей ячейке логические операции осуществляются только межд входной переменной и оперативной информацией, представляющей собой состояние элемента памяти. Цель изобретения - расширение функциональных возможностей логической запоминающей ячейки., Эта цель достигается тем, что в логическую запоминающую ячейку введены два элемента задержки и два дополнительных двухвходовых элемента И, первые входь i которых подключены к соответствующим входам управления ячейки, а вторые - к соответствующим разрядным шинам. Выхо- ды дополнительных элементов И подключены через соответствующие элементы задержки к прямому и инверсному входам ячейки соответственно. На фиг. 1 изображена логическая запо- минаюшая ячейка; на фиг, 2 - принципиальная схема элемента памяти са скрытым изображением. Логическая запоминающая ячейка содержит элемент памяти 1 со скрытым изображением , представляющий собой триггер с раздельными входами на биполярных транзисторах, шику считывания onepaTjm- ной информации 2, две шины считывания постоя шой информации 3, две резряшые шины 4 и 5, к каждой из которых подключен элемент памяти 1 и выходы двух элепамятиментов И6, И и HS, И-Э, первые входы которых соединены ее Елодами упpasneHiiJi ячейки соответственно, а вторые входы объединены попарно и подключены соответствещю к прямому и инверсному входам ячейки. В логическую запоминающую ячейку введены два элемента задерж ки 10, 11 и д,а дополнительных двухвходовых элементе HlS, первые входы которых подключены к соответствующим входам управления ячейки, а вторые - к соот« ветствующим разрядным шинам 4,5. Выходы элементов И., 13 подключены через соответствующие элементы задержки 10, 11 к прямому и инверсному входам ячейки соответственно.

Скрытое изображение создается подключ ЮЙм|диода (элемента И) к .плечу триггера. ,Лри подключении к одному плечу триггера он|создает скрытую 1, к другому - с1фытый О . При подключении двух . диодов (как показано на фиг. 2) можно хра нить в элементе памяти О и фытую 1.

Для считывания оперативной информации на шину 2 подается сигнал, который Ьбу- .славливает появление другого сигнала либо на шине 4, либо на шине 5 в завипимоста от хранимой информации. ГГри: записи новой информации сигнал подается одновременно Hf шину 2 и на одну из шин 4 или 5. При считывании постоянной информации сигнал подается одновремейб на шину 2 и одну, из шин 3,

Реализация логичесиах операций между входной переменной и, оперативной информахшей происходит при подаче управлзпощич сигналов на элементы - 9 и сигнала на шину 2. Вид лог-ической операции опре депяетс набором управляющих сигналов. Обозначим через двоичные переменные: О, - состояние элемента памяти, 5 - сигнал на единичном, а S, - сигнал на нулевом входе элемента памяти, появляющиеся на разрядных шинах при реализации логических операций, Z - сигнал на прямом выходе элемента памяти (прямой разрядной шине), Z - сигнал на инверсном выходе элемента памяти (инверсной разрядной шине), f; - управляющий сигнал (I -номер элемента И, на который подан данный управляющий сигнал), ХД - прямое и инверсное (Значения входной переменной,

Для триггера с дублированными переходами функция переходов запишется;

,t/ (

«()

ir

а входные сигналы S, СЧ) и .S2Ct)onpe- ;аеляются выражениями

- :s.a)xf6Vxf.l , (2)

Тс it

S2,Ct)tX-fgVXfg (3).

Подставляя выражения 2 и 3J в выражение (Д) и полагая ) P(y(t)), после соответствующих преобразований получим:

Cj,( )tfCyWCxfaVxfg)f(y)

(П

Таким образом, подавая определенный набор управляющих сигналов на элемент Иб-ИЭ, можно )еализовать любую из шестнадцати логических функций. Например, при подаче управляющего сигнала только на элемент И 6 реализуется логическая операция ИЛИ, при подаче управляющих сигналов на логические элементы И, логическая опёршвяя инверсия Х,

При реализации логических операций между оперативной и постоянной информациями запоминающая ячейка работает в два такта. В первом такте происходит считывание пос тоянной информации при подаче сигналов на шину 2 в одну из шин 3. В этoм жётak-j те подаются управляю аие сигналы на элементы И12, 13, благодаря чему считанная информация с разрядных шин 4 и 5 поступает на элементы задержки 16, 11. Во втором такте через время, определяемое элементом задержки, подаются управляющие на элементы Иб-И9 к сигнал на шииу 2. В результате реализуется логическая операция между постоянной и опера- тивной информациями, определяемая также выражением (4), в котором в качестве прямого и нверсного значений X выступают прямое и инверсное значения считанной постоянной информации, I

Таким образом, изобретение имеет рас- , ширенные функциональные возможности, заключающиеся в реализации логических операций между оперативной и постоянной информацией, хранящейся в элементе памяти со скрытым рзображением. ,,

Фор

мула изобретения

Логическая запоминающая ячейка, ctf- держащая элементы памяти, четыре двух- входовых элемента И, шину с эитывания оперативной информации, две шины считывания постоянной информации, две разряд- Hbie щины, к каждой из которых подключен элемент памяти и выходы двух ;злемент6в j И, дервые входы которых соединены со входами управления ячейки соответственно, а BTOpbfe входы объединены попарно и подключены соответственно к прямому и ин-

версному входам ячейки, отличающаяся тем, что, с цепью расширения функциональных возможностей ячейки,внее ввгцены два элемента задержки и два до полнитепыа1х двухвходовых элемента И, первые входы которых подключены к соот520586 6

ветствуюшим входам управления ячейки, j вторые - к соответствующим разрядным шинам; выходы дополнительных элементов И подключены через соответчзтвующие эггеменJJ |ты задержки к прямому и инверсному вхо1дам ячейки соответственно. .

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

| Ячейка оперативного запоминающего устройства | 2018 |

|

RU2688242C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Голографическое постоянное запоминающее устройство со сменным носителем голограмм | 1990 |

|

SU1691889A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

Авторы

Даты

1976-07-05—Публикация

1974-07-02—Подача