(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРА УСЛОВНОГО МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ

6ОГО ореобразователя, второй - с четвертым входом устоойства, а выход - со вторым входом умножителя. Второй, третий, четвертый н пятый выходы блока управления соединены с третьим входом второго блока сравнения, входом генератора сигналов, третьим входом умножителя и вторым входом сумматора соответственно.

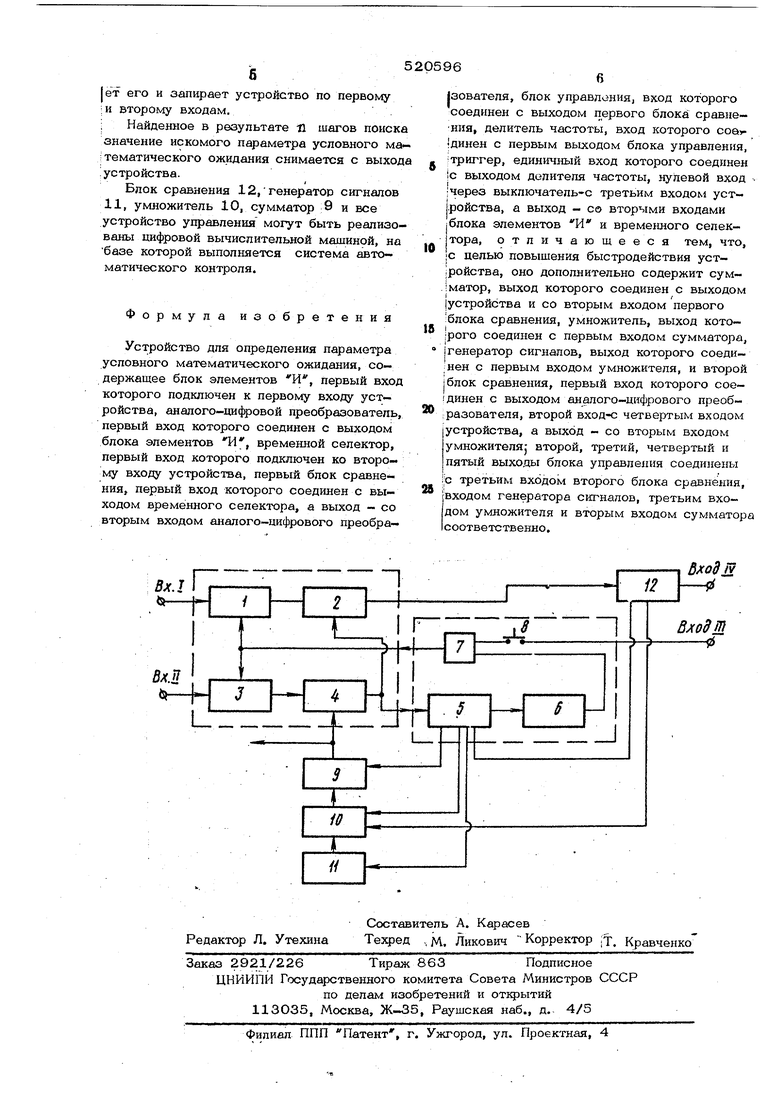

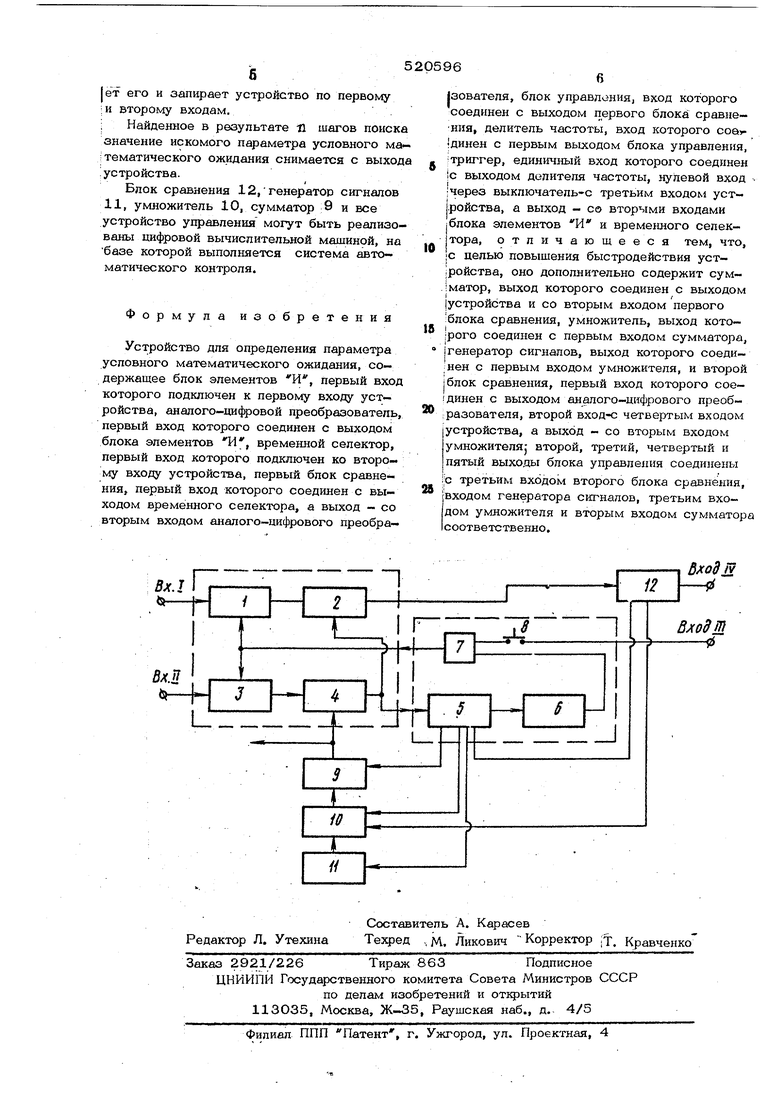

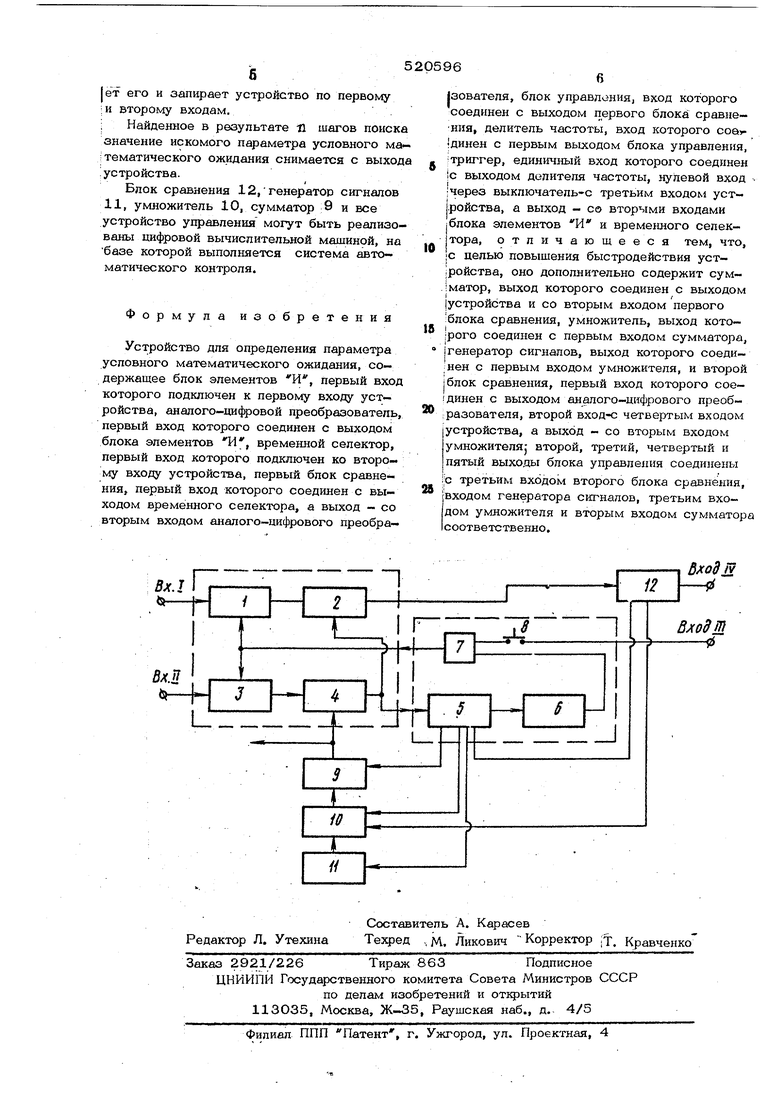

Функциональная схема устройства приведена на чертеже,

Устройство содержит блок формирования условного случайного процесса, включающий в себя блок 1 элементов И, пер. вый вход которого подключен к первому входу устройства, аналого-цифровой преоб- рааователь 2, первый вход которого соединен с выходом блока 1 элементов И, временной селектор 3, первый вход которого подключен ко второму входу устройства, первый блок сравнения 4, первый вход которого соединен с выходом временного селектора 3. Выход первого блока сравнения 4 соединен сО вторым входом преобразователя 2.

Управляет работой всего устройствауст ройство управления, -содержащее блок 5 управления, вход которого соединен с выходом блока сравнения 4, делитель частоты 6, делящий на Л , вход которого соединен с первым выходом блока 5 управпения, триггер 7, единичный вход которого соединен с выходом делителя частоты 6 нулевой через выключатель 8 - с третьим входом устройства, а выход - со вторыми (управляющими) входами блока элементов И 1 и временного селектора 3.

Сумматор 9 соединен с выходом устройства и со вторым входом блока сравнения 4, Выход умножителя 10 соединен с первым входом сумматора 9, а выход генсратора сигналов 11 соединен с первым входом умножителя 10. Первый вход второго блока сравнения 12 соединен с выходом преобразователя 2, второй вход - с четвертым входом устройства, а выход - с вторым входом умножителя 10. Второй третий, четвертый и пятый выходы блока управления 5 соединены с третьим входом второго блока сравнения 12, входом генератора сигналов 11, третьим входом умно жителя 10 и вторым входом сумматора 9 соответственно.

Принцип работы устройства заключается в последовательном подборе (поиске шагами, соотносящимися как члены расходящегося ряда) того значени$ параметра условного математического ожидания, при котором последнее, старювится равным за- данному значению.

К пботает устройство следующим образо

На входы и II устройства подаются случайные процессы у (t) и x(-t) соответствешю, а на втором входе первого блока ° сравнения 4 установлен опорный сигнал X (первре значение искомого параметра условного математического ожидания).

По команде с кнопочного выключателя 8 на триггер 7 начинается первый цикл работы устройства - поиск искомого значения параметра условного математического ожидания. Цикл состоит из формирования условного, случайного процесса у/х, сравнения его с заданным значением А и формирования X. jj (второго значения искомого параметра условного математического ожидания). Триггер 7 перебрасывается и отпирает блок 1 элементов И и времанной селектор 3. Таким образом, блок формирования условного случайного процесса начинает формировать первое аначение условного случайного процесса. В момент равенства случайного процесса X (i) значение Х с первого блока сравнения 4 выдается команда на преобразование в анаSлого-цифровой преобразователь 2 и синхронизирующий импульс в блок 5 управления и далее на делитель частоты 6.

С выхода преобразователя 2 первая; реализация условного случайного процесса поступает на второй блок сравнения 12, где сравнивается с заданным значением А. Разностный сигнал с выхода блока сравнения 12 подается на умножитель 10 в качестве одного из сомножителей. Вторым сомножителем служит первое значение сигнала с генератора сигналов 11, Произведение подается на сумматор 9с преобразователем, где формируется второе значение искомого параметра условного математического ожидания. На этом первый цикл поиска параметра условного математического ожидания заканчивается.

Последовательная работа в цикле вто.рого бпока сравнения 12, генератора сиг|Налов 11, умножителя 10 и сумматора 9 с преобразователем обеспечивается последовательными командами с блока управления 5.

. В последующих циклах поиска генератор сигналов IP выдает ступеньки, соотносящиеся как члены расходящегося ряда типа к/я , где п - номер очередного цикла (ш га поиска). Этим обеспечивается сходимость поиска. Число циклов(щагов поиска) определяется, исходя из требуемой точност и коэффициентом деления делителя частоты 6, который является счетчиком циклов По приходе- требуемого числа синхронизируюших импульсов делитель частоты 6 вы- дает импульс на триггер 7, перебрасыва- |ет его и запирает устройство по первому ; И второму входам. ; Найденное в результате tl шагов поиск значение искомого параметра условного м ; тематического ожидания снимается с выхо ,устройства. Блок сравнения 12,генератор сигналов 11, умножитель 10, сумматор 9 и все устройство управлении могут быть реализо ваны цифровой вычислительной машинрй, на базе которой выполняется система автоматического контроля. ормула изобретения Устройство для определения параметра условного математического ожидания, содержащее блок элементов И, первый вход которого подключен к первому входу устройства, аналого-цифровой преобразователь первый вход которого соединен с выходом блока элементов И, временной селектор, первый вход которого подключен ко второ му входу устройства, первый блок сравнения, первый вход которого соединен с выходом временного селектора, а выход - со вторым входом аналого-цифрового преобра1зователя, блок ynpaanoHHHj вход которого соединен с выходом первого блока сравнения, делитель частоты, вход которого сое, динен с первым выходом блока управления, )триггер, единичный вход которого соединен 1C выходом делителя частоты, нулевой вход ; через выключатель-с третьим входом уст|ройства, а выход - со вторыми входами .блока элементов И и временного селекiTOpa, о т л и ч а ю щ е е с я тем, что, jC целью повышения быстродействия уст|ройства, оно дополнительно содержит сум;матор, выход которого соединен с выходом устройства и со вторым входом первого Яблока сравнения, умножитель, выход котоiporo соединен с первым входом сумматора, генератор сигналов, выход которого соединен с первым входом умножителя, и второй I блок сравнения, первый вход которого сое динен с выходом аналого-цифрового преоб;разователя, второй входч: четвертым входом устройства, а выход - со вторым входом умножителя,- второй, третий, четвертый и пятый выходы блока управления соединены |;с третьим входом второго блока сравнения, входом генератора сигналов, третьим входом умножителя и вторым входом сумматора соответственно.

Авторы

Даты

1976-07-05—Публикация

1974-07-15—Подача