Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики логических блоков.

Цель изобретения - расширение номенклатуры контролируемых блоков за счет обеспечения проверки блоков, входные и выходные уровни которых соответствуют разным типам логики; или толькЬ ЭСЛ-логике, или только ТТЛ-логик, а также блоков, имеющих, как ТТЛ, так и ЭСЛ-уровни,

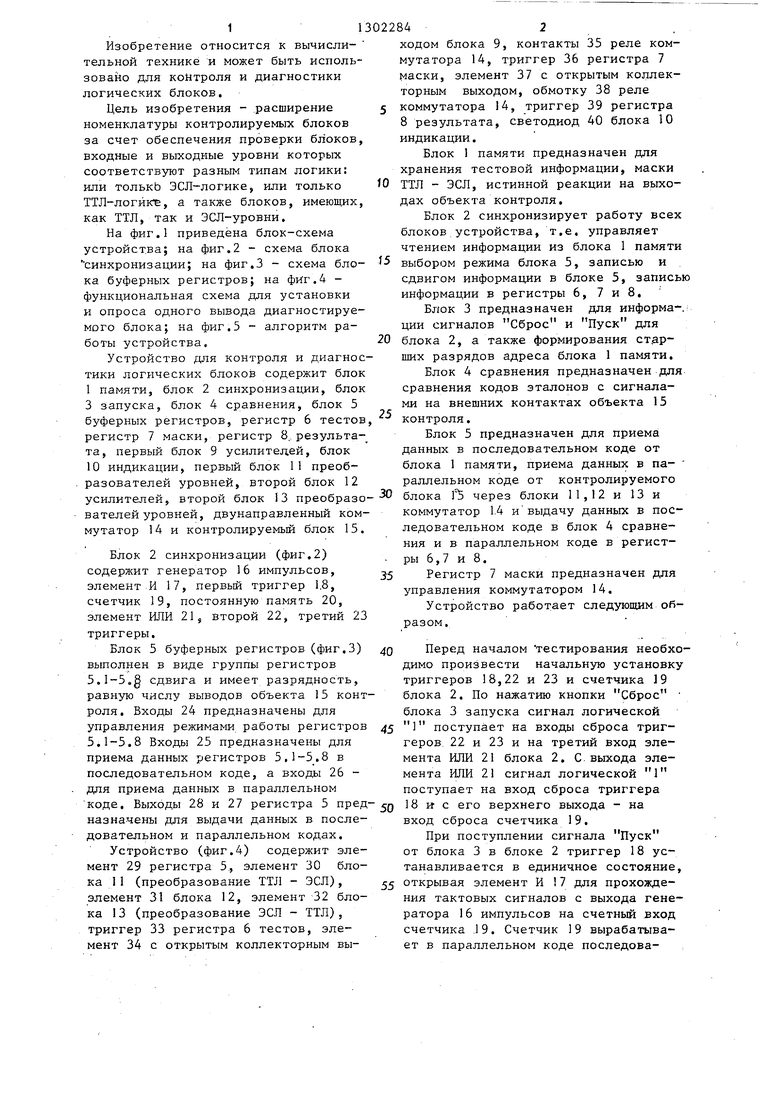

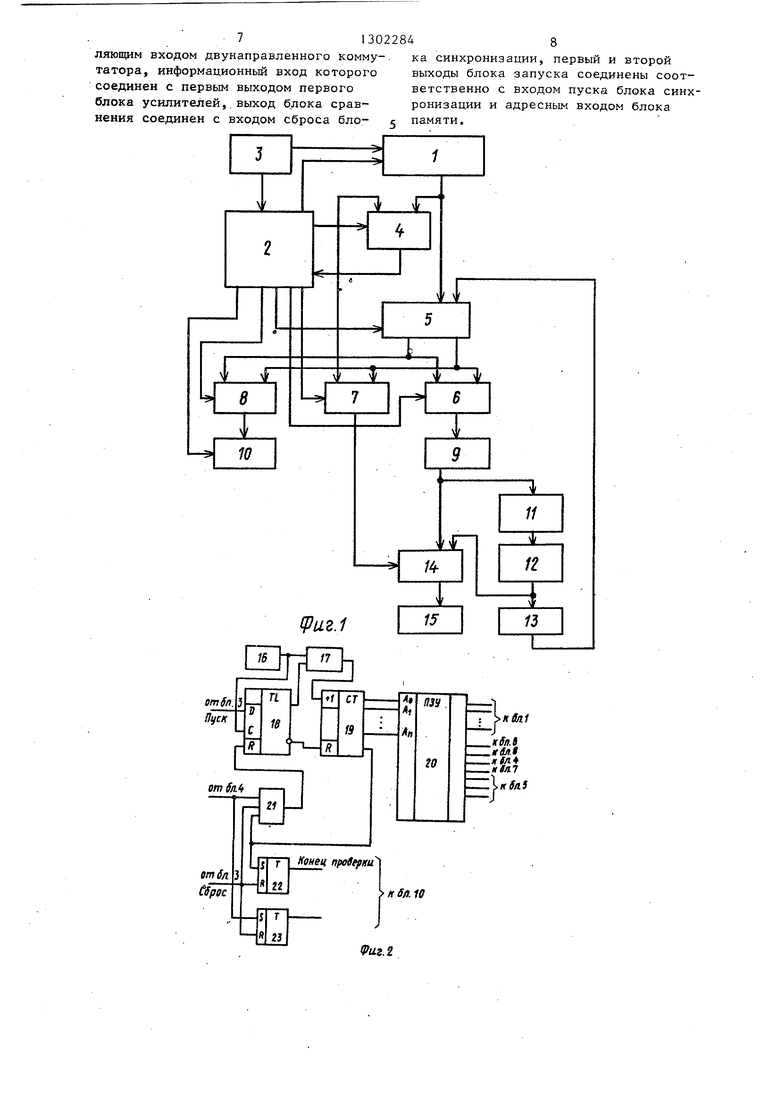

На фиг.1 приведена блок-схема устройства; на фиг.2 - схема блока

ходом блока 9, контакты 35 реле коммутатора 14, триггер 36 регистра 7 маски, элемент 37 с открытым коллекторным выходом, обмотку 38 реле 5 коммутатора 14, триггер 39 регистра 8 результата, светодиод 40 блока 10 индикации.

Блок 1 памяти предназначен для хранения тестовой информации, маски to ТТЛ - ЭСЛ, истинной реакции на выходах объекта контроля.

Блок 2 синхронизирует работу всех блоков устройства, т.е. управляет чтением информации из блока 1 памяти

синхронизации; на фиг.З - схема бло- 5 выбором режима блока 5, записью и ка буферных регистров; на фиг.4 - сдвигом информации в блоке 5, записью

функциональная схема для установки и опроса одного вывода диагностируемого блока; на фиг.З - алгоритм работы устройства.

Устройство для контроля и диагностики логических блоков содержит блок 1 памяти, блок 2 синхронизации, блок 3 запуска, блок 4 сравнения, блок 5

информации в регистры 6, 7 и 8.

Блок 3 предназначен для информа-. ции сигналов Сброс и Пуск для 20 блока 2, а также формирования старших разрядов адреса блока 1 памяти.

Блок 4 сравнения предназначен для сравнения кодов эталонов с сигналами на внешних контактах объекта 15

J OO-li V 4 Ч О. JJ J Л V-ЛIJ /1 ,,.i.

буферных регистров, регистр 6 тестов,контроля, регистр 7 маски, регистр 8, результа- Блок 5 предназначен для приема

та, первый блок 9 усилитедей, блокданных в последовательном коде от

10 индикации, первый блок 11 преоб-блока 1 памяти, приема данных в па- разователей уровней, второй блок 12раллельном коде от контролируемого усилителей, второй блок 13 преобразо-- блока f5 через блоки 11,12 и 13 и

вателей уровней, двунаправленный ком-коммутатор 1.4 и выдачу данных в последовательном коде в блок 4 сравнения и в параллельном коде в регистры 6 , 7 и 8 .

мутатор 14 и контролируемый блок 15.

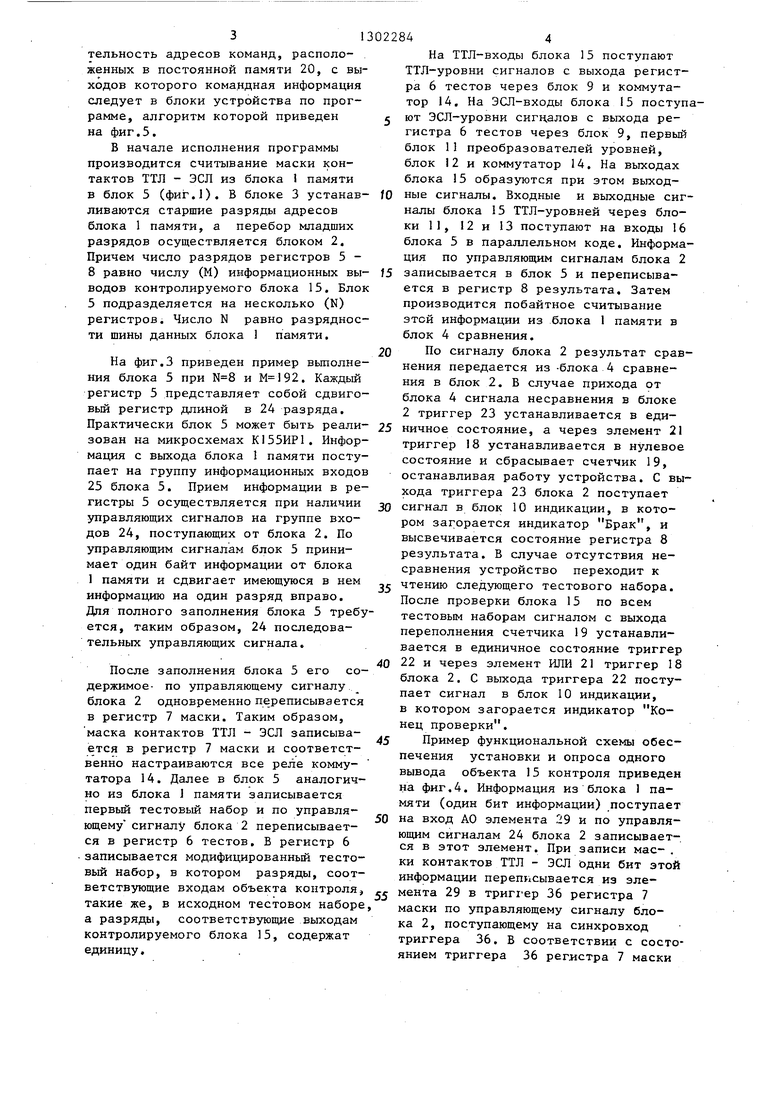

Блок 2 синхронизации (фиг.2) содержит генератор 16 импульсов, элемент И 17, первьм триггер 1.8, счетчик 19, постоянную память 20, элемент ИЛИ 21, второй 22, третий 23 триггеры.

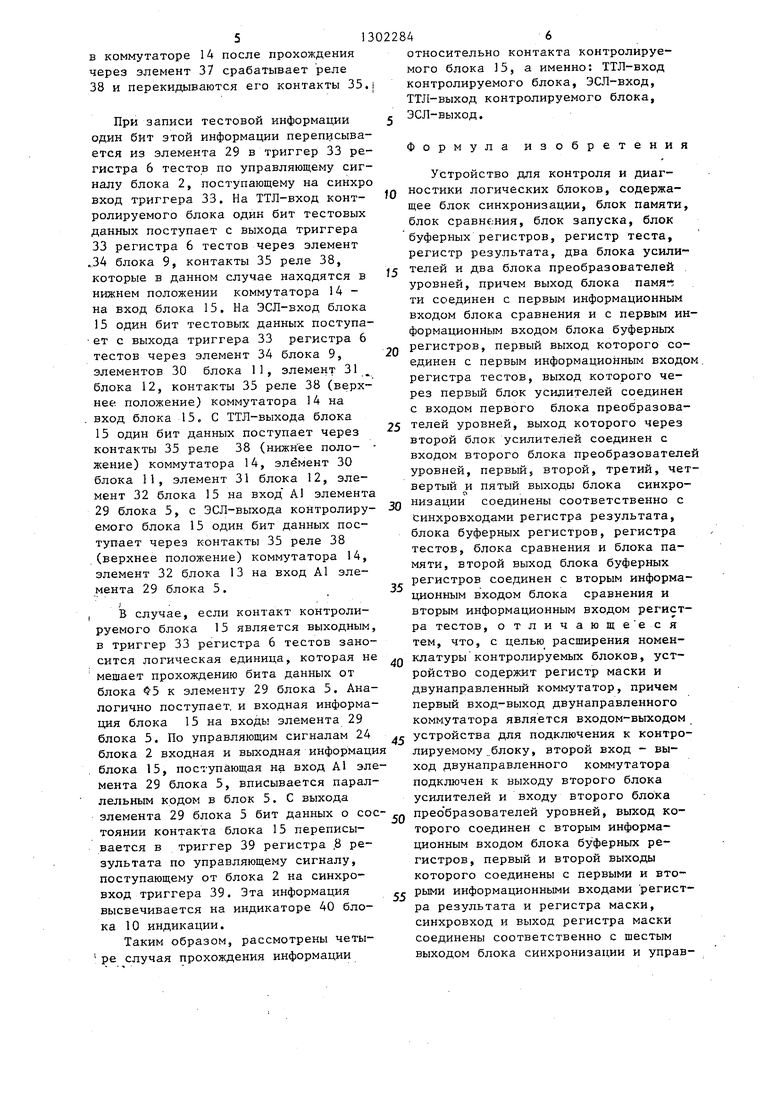

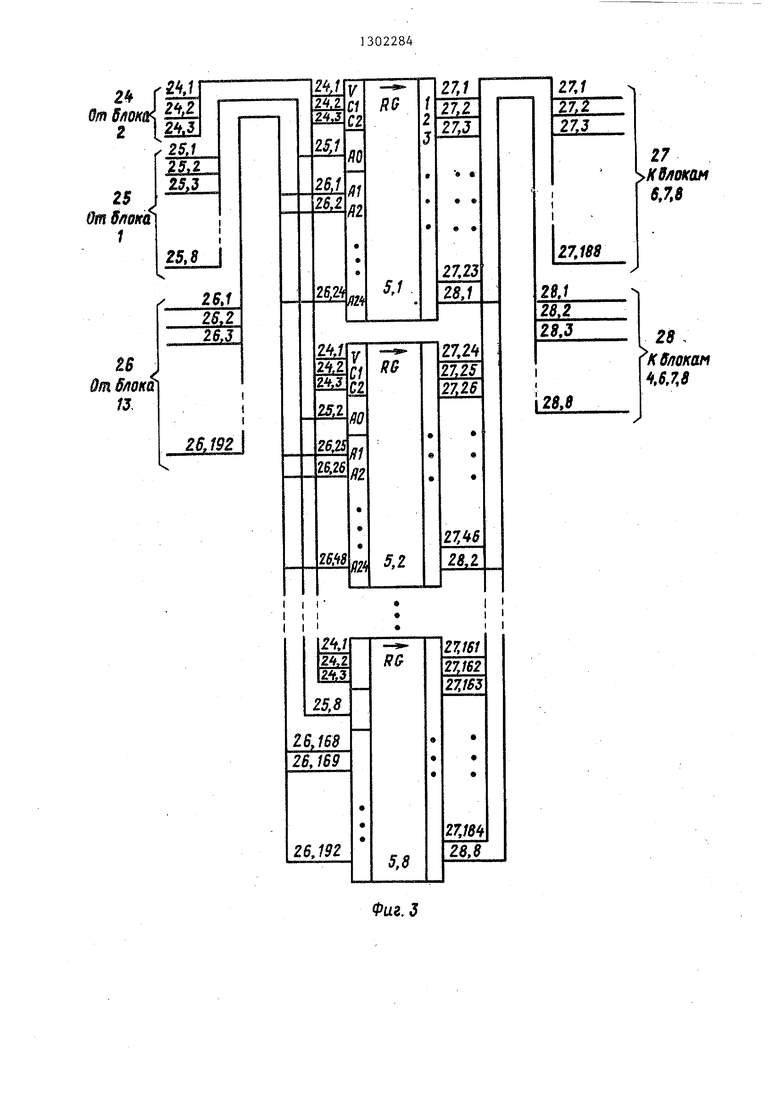

Блок 5 буферных регистров (фиг.З) выполнен в виде группы регистров 5.1-5.§ сдвига и имеет разрядность, равную числу выводов объекта 15 контроля. Входы 24 предназначены для управления режимами работы регистров 5.1-5.8 Входы 25 предназначены для приема данных регистров 5.1-5.8 в последовательном коде, а входы 26 - для приема данных в параллельном коде. Выходы 28 и 27 регистра 5 пред назначены для выдачи данных в последовательном и параллельном кодах.

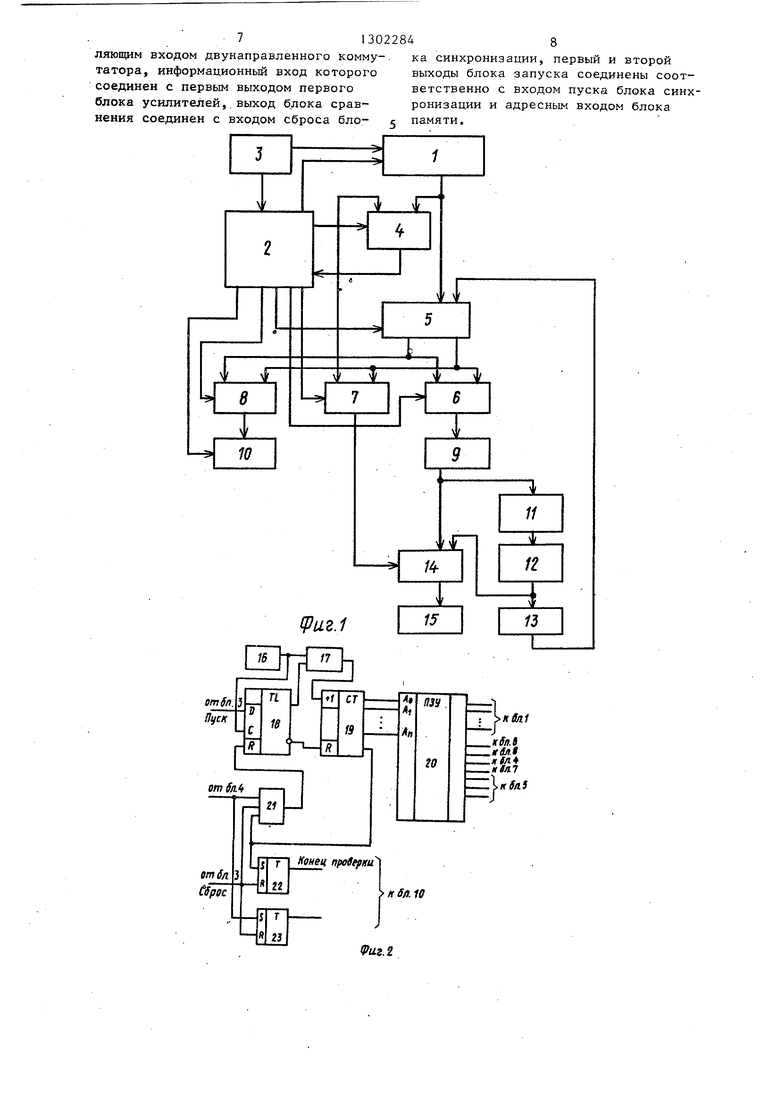

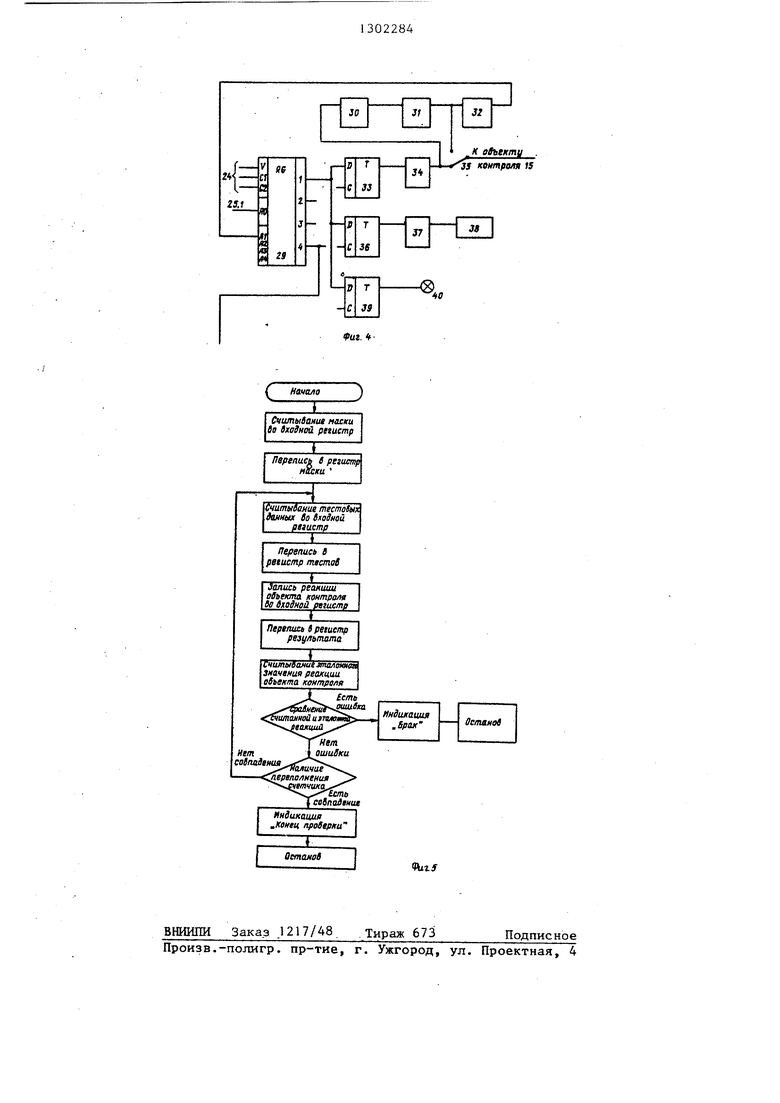

Устройство (фиг.4) содержит элемент 29 регистра 5, элемент 30 блока 1 1 (преобразование ТТЛ - ЭСЛ), элемент 31 блока 12, элемент 32 блока 13 (преобразование ЭСЛ - ТТЛ), триггер 33 регистра 6 тестов, элемент 34 с открытым коллекторным вы

ходом блока 9, контакты 35 реле коммутатора 14, триггер 36 регистра 7 маски, элемент 37 с открытым коллекторным выходом, обмотку 38 реле коммутатора 14, триггер 39 регистра 8 результата, светодиод 40 блока 10 индикации.

Блок 1 памяти предназначен для хранения тестовой информации, маски ТТЛ - ЭСЛ, истинной реакции на выходах объекта контроля.

Блок 2 синхронизирует работу всех блоков устройства, т.е. управляет чтением информации из блока 1 памяти

информации в регистры 6, 7 и 8.

Блок 3 предназначен для информа-.: ции сигналов Сброс и Пуск для блока 2, а также формирования старших разрядов адреса блока 1 памяти.

Блок 4 сравнения предназначен для сравнения кодов эталонов с сигналами на внешних контактах объекта 15

,,.i.

ледовательном коде в блок 4 сравнения и в параллельном коде в регистры 6 , 7 и 8 .

Регистр 7 маски предназначен для управления коммутатором 14.

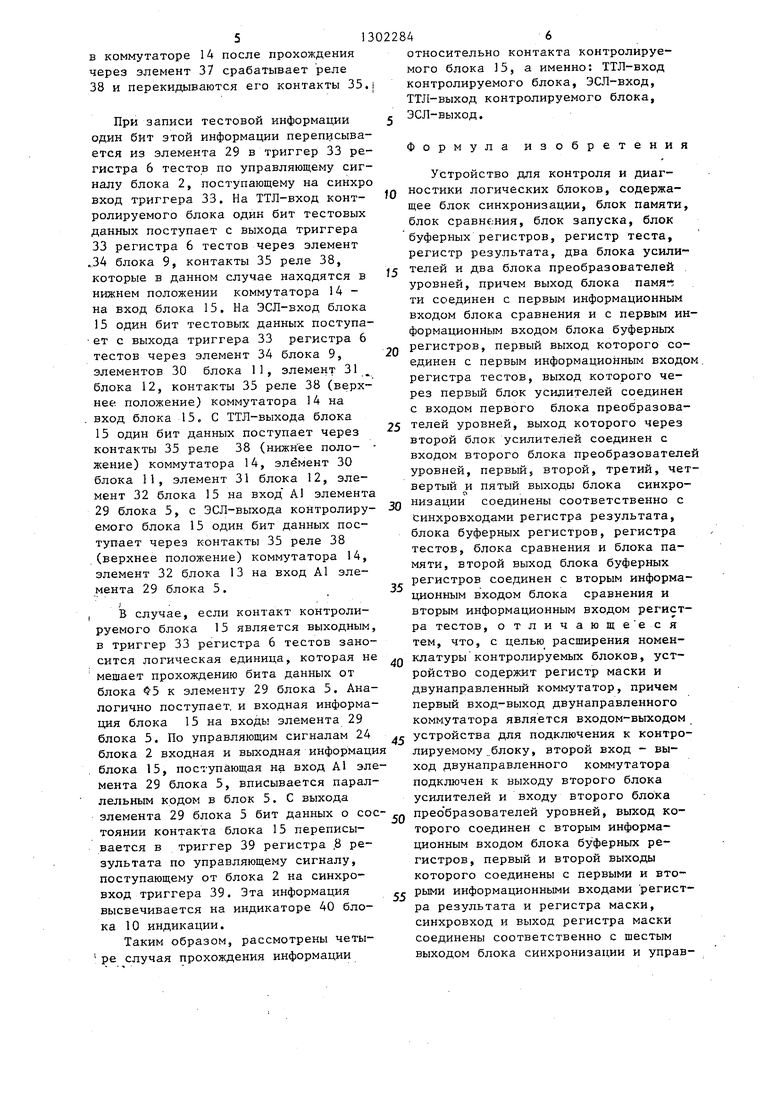

Устройство работает следующим образом.

Перед началом тестирования необходимо произвести начальную установку триггеров 18,22 и 23 и счетчика 19 блока 2. По нажатию кнопки Сброс блока 3 запуска сигнал логической 1 поступает на входы сброса тригQ

геров 22 и 23 и на третий вход элемента ИЛИ 21 блока 2. С.выхода элемента ИЛИ 21 сигнал логической 1 поступает на вход сброса триггера 18 н с его верхнего выхода - на вход сброса счетчика 19.

При поступлении сигнала Пуск от блока 3 в блоке 2 триггер 18 устанавливается в единичное состояние, 5 открывая элемент И 17 для прохождения тактовых сигналов с выхода генератора 16 импульсов на счетный вход счетчика .19. Счетчик 19 вырабатывает в параллельном коде последовательность адресов команд, расположенных в постоянной памяти 20, с выходов которого командная информация следует в блоки устройства по программе, алгоритм которой приведен на фиг.5.

В начале исполнения программы производится считывание маски контактов ТТЛ - ЭСЛ из блока 1 памяти в блок 5 (фиг.1). В блоке 3 устанавливаются старшие разряды адресов блока 1 памяти, а перебор младших разрядов осуществляется блоком 2, Причем число разрядов регистров 5 - 8 равно числу (М) информационных выводов контролируемого блока 15. Блок 5 подразделяется на несколько (N) регистров. Число N равно разрядности шины данных блока памяти.

На фиг.З приведен пример вьшолне- ния блока 5 при и . Каждый регистр 5 представляет собой сдвиго- вьй регистр длиной в 24 разряда. Практически блок 5 может быть реализован на микросхемах К155ИР1. Информация с выхода блока 1 памяти поступает на группу информационных входов 25 блока 5. Прием информации в регистры 5 осуществляется при наличии управляющих сигналов на группе входов 24, поступающих от блока 2. По управляющим сигналам блок 5 принимает один байт информации от блока 1 памяти и сдвигает имеющуюся в нем информацию на один разряд вправо. Для полного заполнения блока 5 требуется, таким образом, 24 последовательных управляющих сигнала.

После заполнения блока 5 его содержимое- по управляющему сигналу блока 2 одновременно переписывается в регистр 7 маски. Таким образом, маска контактов ТТЛ - ЭСЛ записывается в регистр 7 маски и соответственно настраиваются все реле коммутатора 14. Далее в блок 5 аналогично из блока памяти записывается первый тестовый набор и по управляющему сигналу блока 2 переписывается в регистр 6 тестов. В регистр 6 записывается модифицированный тестовый набор, в котором разряды, соответствующие входам объекта контроля, такие же, в исходном тестовом наборе а разряды, соответствующие выходам контролируемого блока 15, содержат единицу.

На ТТЛ-входы блока 15 поступают ТТЛ-уровни сигналов с выхода регистра 6 тестов через блок 9 и коммутатор 14. На ЭСЛ-входы блока 15 поступа- е ют ЭСЛ-уровни сигналов с выхода регистра 6 тестов через блок 9, первый блок 11 преобразователей уровней, блок 12 и коммутатор 14. На выходах блока 15 образуются при этом выходO ные сигналы. Входные и выходные сигналы блока 15 ТТЛ-уровней через блоки 11, 12 и 13 поступают на входы 16 блока 5 в параллельном коде. Информация по управляющим сигналам блока 2

5 записывается в блок 5 и переписывается в регистр 8 результата. Затем производится побайтное считьшание этой информации из блока 1 памяти в блок 4 сравнения.

0 По сигналу блока 2 результат сравнения передается из -блока 4 сравнения в блок 2. В случае прихода от блока 4 сигнала несравнения в блоке 2 триггер 23 устанавливается в еди5 ничное состояние, а через элемент 21 триггер 18 устанавливается в нулевое состояние и сбрасывает счетчик 19, останавливая работу устройства. С выхода триггера 23 блока 2 поступает

0 сигнал в блок 10 индикации, в котором загорается индикатор Брак, и высвечивается состояние регистра 8 результата. В случае отсутствия несравнения устройство переходит к

чтению следующего тестового набора. После проверки блока 15 по всем тестовым наборам сигналом с выхода переполнения счетчика 19 устанавливается в единичное состояние триггер

0 22 и через элемент ИЛИ 21 триггер 18 блока 2. С выхода триггера 22 поступает сигнал в блок 10 индикации, в котором загорается индикатор Конец проверки.

5 Пример функциональной схемы обеспечения установки и опроса одного вывода объекта 15 контроля приведен на фиг.4. Информация из блока 1 памяти (один бит информации) поступает

0 на вход АО элемента 29 и по управляющим сигналам 24 блока 2 записывается в этот элемент. При записи мае- . ки контактов ТТЛ - ЭСЛ одни бит этой информации переписывается из эле мента 29 в трип ер 36 регистра 7 маски по управляющему сигналу блока 2, поступающему на синхровход триггера 36. В соответствии с состоянием триггера 36 регистра 7 маски

в коммутаторе 14 после прохождения

через элемент 37 срабатывает реле

38 и перекидываются его контакты 35.1

При записи тестовой информации 5 один бит этой информации переписывается из элемента 29 в триггер 33 регистра 6 тестов по управляющему сигналу блока 2, поступающему на синхро вход триггера 33. На ТТЛ-вход конт- О ролируемого блока один бит тестовых данных поступает с выхода триггера 33 регистра 6 тестов через элемент

,34 блока 9, контакты 35 реле 38, которые в данном случае находятся в 5 нижнем положении коммутатора 14 - на вход блока 15. На ЭСЛ-вход блока 15 один бит тестовых данных поступает с выхода триггера 33 регистра 6 тестов через элемент 34 блока 9, 20 элементов 30 блока 11, элемент 31 блока 12, контакты 35 реле 38 (верхнее, положение) коммутатора 14 на

вход блока 15. С ТТЛ-выхода блока 15 один бит данных поступает через контакты 35 реле 38 (нижн ёе поло- женив) коммутатора 14, элемент 30 блока 11, элемент 31 блока 12, элемент 32 блока 15 на вход А1 элемента 29 блока 5, с ЭСЛ-выхода контролиру- 30 емого блока 15 один бит данных поступает через контакты 35 реле 38 (верхнее положение) коммутатора 14, элемент 32 блока 13 на вход А1 элемента 29 блока 5.35 . J . ,

В случае, если контакт контролируемого блока 15 является выходным, в триггер 33 регистра 6 тестов заносится логическая единица, которая не

мешает прохождению бита данных от блока Ф5 к элементу 29 блока 5. Аналогично поступает, и входная информация блока 15 на входы элемента 29 блока 5. По управляющим сигналам 24 блока 2 входная и выходная информация

блока 15, поступающая на вход А1 элемента 29 блока 5, вписывается параллельным кодом в блок 5. С выхода элемента 29 блока 5 бит данных о состоянии контакта блока 15 переписывается в триггер 39 регистра ,8 результата по управляющему сигналу, поступающему от блока 2 на синхро- вход триггера 39. Эта информация высвечивается на индикаторе 40 блока 10 индикации.

Таким образом, рассмотрены четыре случая прохождения информации

50

относительно контакта контролируемого блока 15, а именно: ТТЛ-вход контролируемого блока, ЭСЛ-вход, ТТЛ-выход контролируемого блока, ЭСЛ-выход.

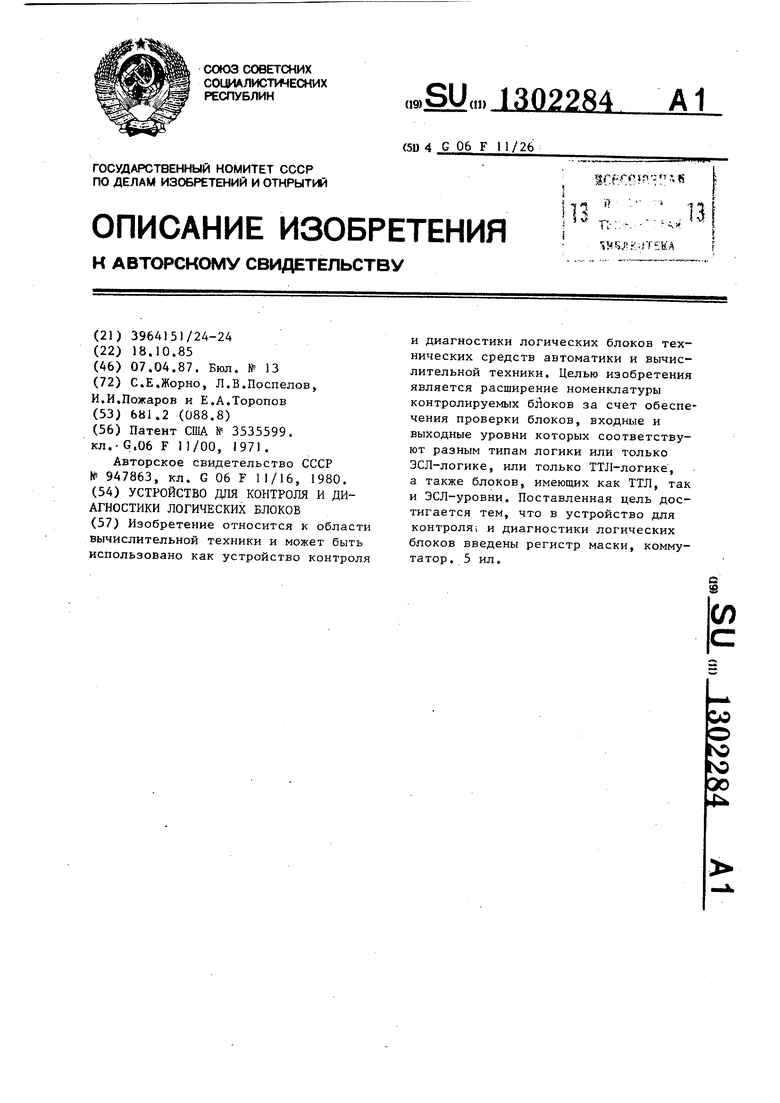

Формула изобретения

Устройство для контроля и диагностики логических блоков, содержащее блок синхронизации, блок памяти, блок сравнения, блок запуска, блок буферных регистров, регистр теста, регистр результата, два блока усили телей и два блока преобразователей уровней, причем выход блока памя- ти соединен с первым информационным входом блока сравнения и с первым информационным входом блока буферных регистров, первый выход которого соединен с первым информационным входом. регистра тестов, выход которого через первый блок усилителей соединен с входом первого блока преобразователей уровней, выход которого через второй блок усилителей соединен с входом второго блока преобразователей уровней, первый, второй, третий, четвертый и пятый выходы блока синхроо

низации соединены соответственно с синхровходами регистра результата, блока буферных регистров, регистра тестов, блока сравнения и блока памяти, второй выход блока буферных регистров соединен с вторым информационным входом блока сравнения и вторым информационным входом регистра тестов, о тлич ающе ес я тем, что, с целью расширения номенклатуры контролируемых блоков, устройство содержит регистр маски и двунаправленный коммутатор, причем первый вход-выход двунаправленного коммутатора является входом-выходом устройства для подключения к контролируемому блоку, второй вход - выход двунаправленного коммутатора подключен к Выходу второго блока усилителей и входу второго блока прео бразователей уровней, выход которого соединен с вторым информационным входом блока бу ферных регистров, первый и второй выходы которого соединены с первыми и вторыми информационными входами регистра результата и регистра маски, синхровход и выход регистра маски соединены соответственно с шестым выходом блока синхронизации и управ71302284

ляющим входом двунаправленного комму-. татора, информационный вход которого соединен с первым выходом первого блока усилителей, выход блока сравнения соединен с входом сброса бло-

8

ка синхронизации, первый и второй выходы блока запуска соединены соответственно с входом пуска блока синхронизации и адресным входом блока памяти.

Фаг. J

Начало

I

СчшпыЯанив Hoc/fu So бхайной petucmp

JПерепись S регистр

H&XU

Счшпнйание mecmaftix данных во бхоЗнай piiucmp

Перепись S petucmp mtanaS

J

ja/шсб реакции авьекта /сонтроля fa if одной регистр

Перепись в peiuemp результата

i

считыеамае зталштвл значения решщчи обмята контроля

9аг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для диагностики логических блоков | 1988 |

|

SU1672452A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1251085A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для цифрового контроля электронных схем | 1986 |

|

SU1413633A1 |

| Устройство для тестового контроля цифровых узлов | 1980 |

|

SU918949A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

Изобретение относится к области вычислительной техники и может быть использовано как устройство контроля и диагностики логических блоков технических средств автоматики и вычислительной техники. Целью изобретения является расширение номенклатуры контролируемых бйоков за счет обеспечения проверки блоков, входные и выходные уровни которых соответствуют разным типам логики или только ЭСЛ-логике, или только ТТЛ-логике, а также блоков, имеющих как ТТЛ, так и ЭСЛ-уровни. Поставленная цель достигается тем, что в устройство для контроля и диагностики логических блоков введены регистр маски, коммутатор. 5 ил.

ВНИИПИ Заказ .1217/48 . Тираж 673

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Подписное

| Патент США № 3535599 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-10-18—Подача