Изобретение относится к вычислительной технике и может быть использовано для диагностики неисправностей цифровых узлов

(ЦУ).

Цель изобретения - повышение точности диагностики

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - функциональная схема блока генерации тестов; на фиг. 3 - функциональная схема блока микропрограммного управления; на фиг. 4- функциональная схема сигнатурного анализатора; на фиг. 5 - функциональная схема фиксации конечного адреса.

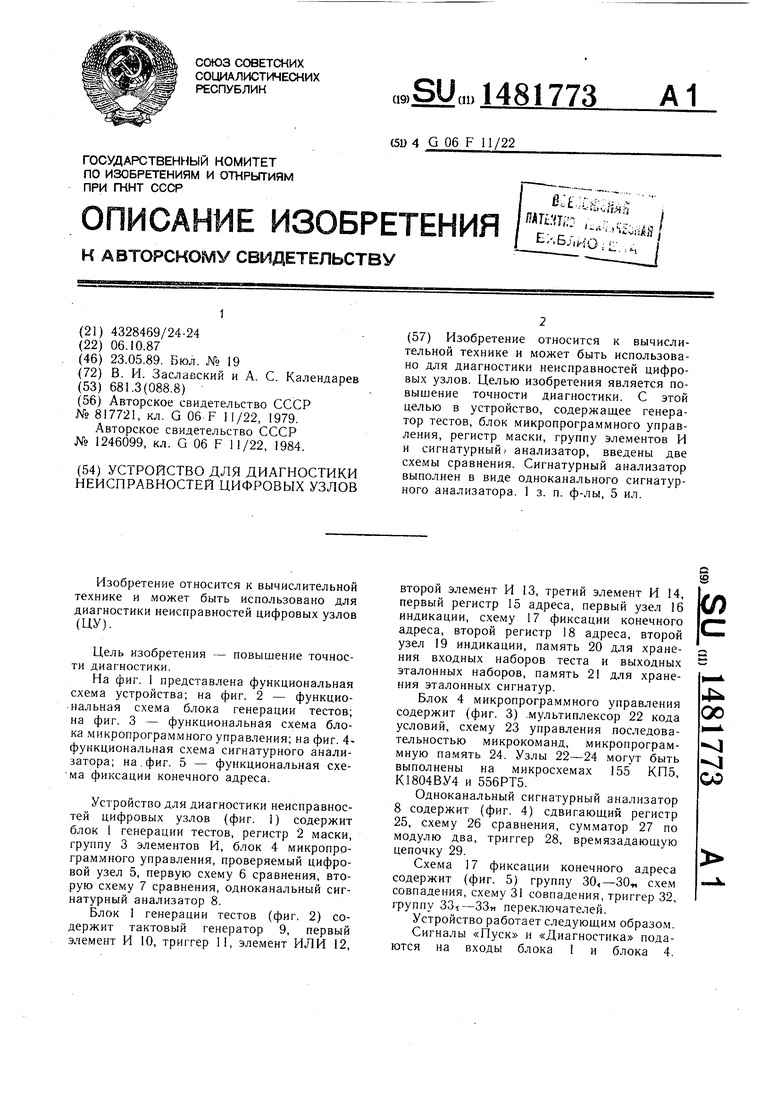

Устройство для диагностики неисправностей цифровых узлов (фиг. 1) содержит блок 1 генерации тестов, регистр 2 маски, группу 3 элементов И, блок 4 микропрограммного управления, проверяемый цифровой узел 5, первую схему 6 сравнения, вторую схему 7 сравнения, одноканальный сигнатурный анализатор 8.

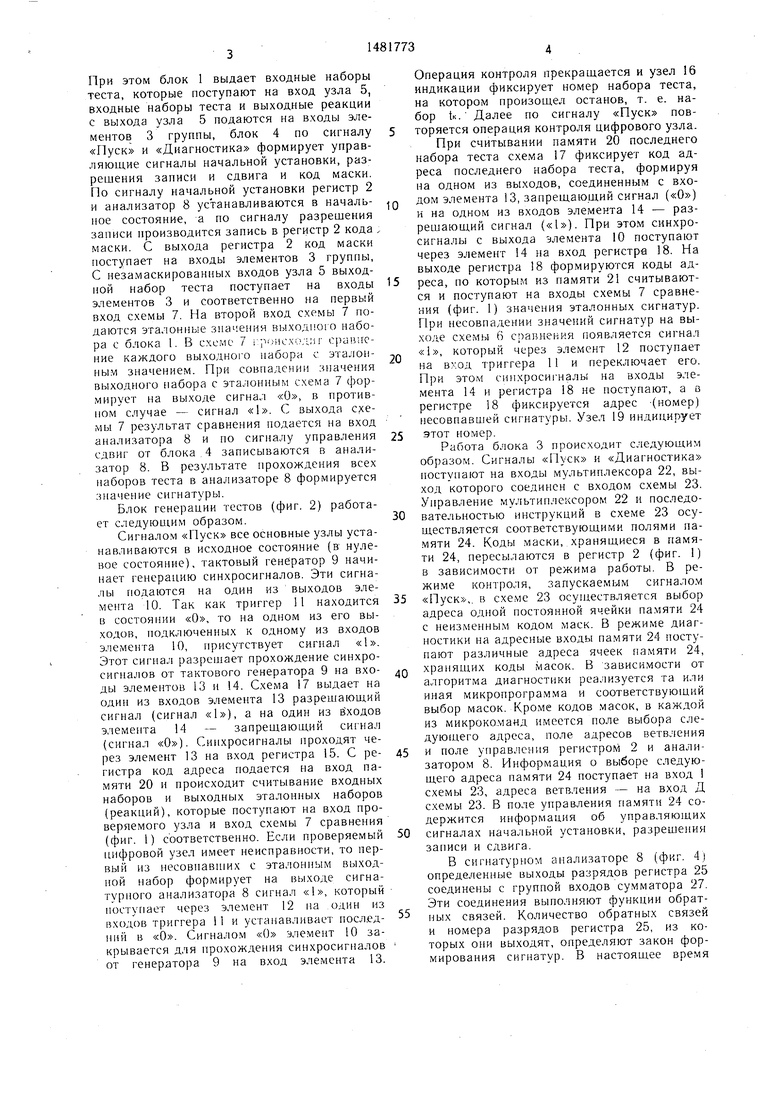

Блок 1 генерации тестов (фиг. 2) содержит тактовый генератор 9, первый элемент И 10, триггер 11, элемент ИЛИ 12,

второй элемент И 13, третий элемент И 14, первый регистр 15 адреса, первый узел 16 индикации, схему 17 фиксации конечного адреса, второй регистр 18 адреса, второй узел 19 индикации, память 20 для хранения входных наборов теста и выходных эталонных наборов, память 21 для хранения эталонных сигнатур.

Блок 4 микропрограммного управления содержит (фиг. 3) мультиплексор 22 кода условий, схему 23 управления последовательностью микрокоманд, микропрограммную память 24. Узлы 22-24 могут быть выполнены на микросхемах 155 КП5, К1804ВУ4 и 556РТ5.

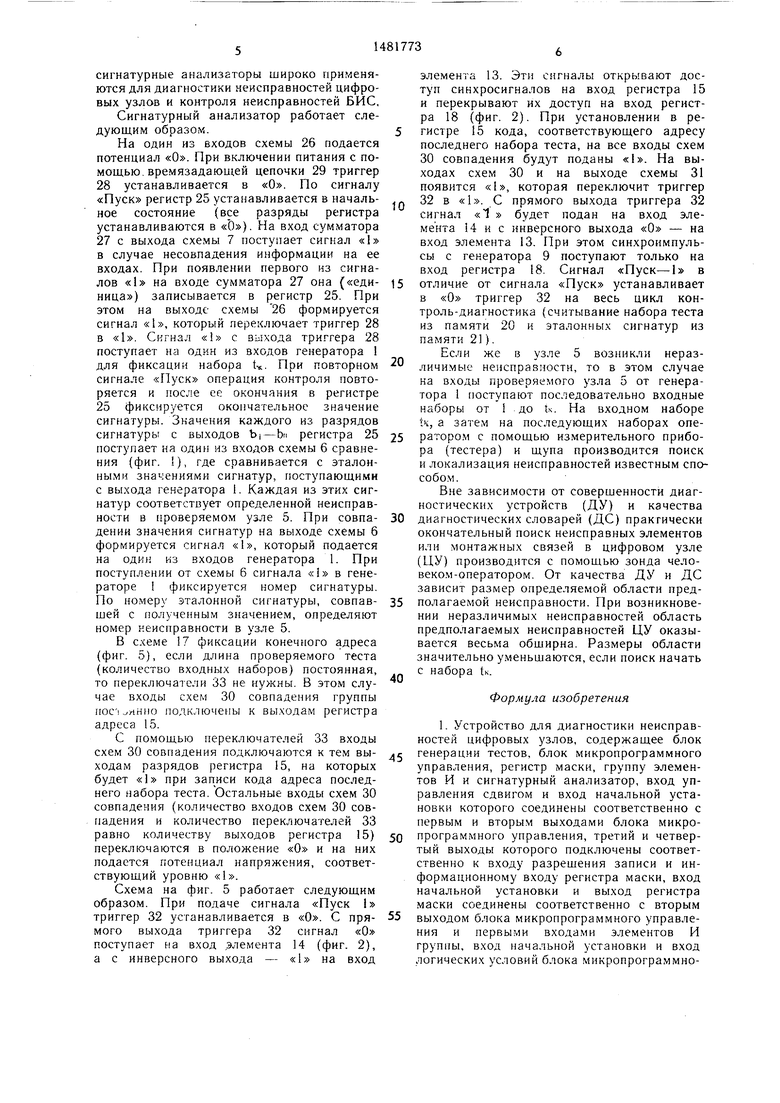

Одноканальный сигнатурный анализатор 8 содержит (фиг. 4) сдвигающий регистр 25, схему 26 сравнения, сумматор 27 по модулю два, триггер 28, времязадающую цепочку 29.

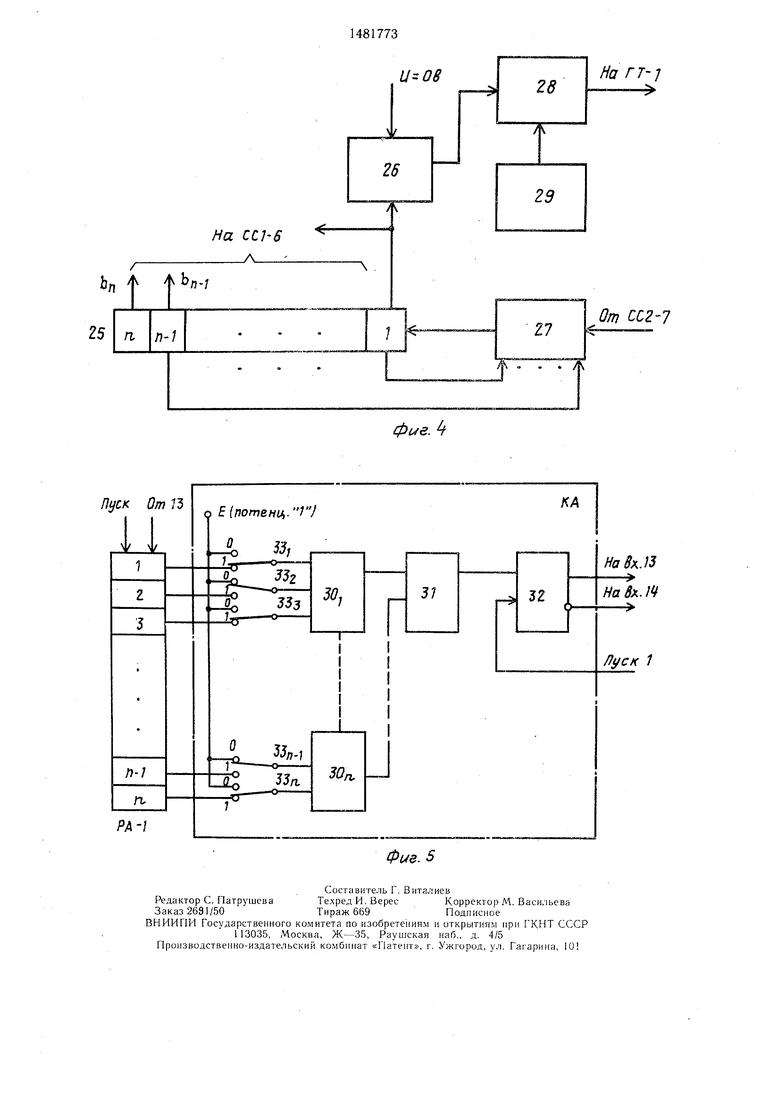

Схема 17 фиксации конечного адреса содержит (фиг. 5) группу схем совпадения, схему 31 совпадения,триггер 32, группу 33i-ЗЗя переключателей.

Устройство работает следующим образом.

Сигналы «Пуск и «Диагностика подаются на входы блока 1 и блока 4

S

(Л

Ј

х

vj

GO

При этом блок 1 выдает входные наборы теста, которые поступают на вход узла 5, входные наборы теста и выходные реакции с выхода узла 5 подаются на входы элементов 3 группы, блок 4 по сигналу «Пуск и «Диагностика формирует управляющие сигналы начальной установки, разрешения записи и сдвига и код маски. По сигналу начальной установки регистр 2 и анализатор 8 устанавливаются в началь- ное состояние, а по сигналу разрешения записи производится запись в регистр 2 кода маски. С выхода регистра 2 код маски поступает на входы элементов 3 группы, С незамаскированных входов узла 5 выходной набор теста поступает на входы элементов 3 и соответственно на первый вход схемы 7. На второй вход схемы 7 подаются эталонные значения выходною набора с блока 1. В схеме 7 i p..iicx,uii epau;ic- ние каждого выходного набора с эталон- ным значением. При совпадении значения выходного набора с эталонным схема 7 формирует на выходе сигнал «О, в противном случае - сигнал «1. С выхода схемы 7 результат сравнения подается на вход анализатора 8 и по сигналу управления сдвиг от блока 4 записываются в анализатор 8. В результате прохождения всех наборов теста в анализаторе 8 формируется значение сигнатуры.

Блок генерации тестов (фиг. 2) работает следующим образом.

Сигналом «Пуск все основные узлы устанавливаются в исходное состояние (в нулевое состояние), тактовый генератор 9 начинает генерацию синхросигналов. Эти сигналы подаются на один из выходов элемента 10. Так как триггер 11 находится в состоянии «О, то на одном из его выходов, подключенных к одному из входов элемента 10, присутствует сигнал «1. Этот сигнал разрешает прохождение синхросигналов от тактового генератора 9 на вхо- ды элементов 13 и 14. Схема 17 выдает на один из входов элемента 13 разрешающий сигнал (сигнал «1), а на один из выходов элемента 14 - запрещающий сигнал (сигнал «О). Синхросигналы проходят через элемент 13 на вход регистра 15. С ре- гистра код адреса подается на вход памяти 20 и происходит считывание входных наборов и выходных эталонных наборов (реакций), которые поступают на вход проверяемого узла и вход схемы 7 сравнения (фиг. 1) соответственно. Если проверяемый цифровой узел имеет неисправности, то первый из несовпавших с эталонным выходной набор формирует на выходе сигнатурного анализатора 8 сигнал «1, который поступает через элемент 12 па один из входов триггера 11 и устанавливает посл.ед- ний в «О. Сигналом «О элемент 10 закрывается для прохождения синхросигналов от генератора 9 на вход элемента 13.

Операция контроля прекращается и узел 16 индикации фиксирует номер набора теста, на котором произошел останов, т. е. набор 1к. Далее по сигналу «Пуск повторяется операция контроля цифрового узла.

При считывании памяти 20 последнего набора теста схема 17 фиксирует код адреса последнего набора теста, формируя на одном из выходов, соединенным с входом элемента S3, запрещающий сигнал («О) и на одном из входов элемента 14 - разрешающий сигнал («1). При этом синхросигналы с выхода элемента 10 поступают через элемент 14 на вход регистра 18. На выходе регистра 18 формируются коды адреса, по которым из памяти 21 считываются и поступают на входы схемы 7 сравнения (фиг. 1) значения эталонных сигнатур. При несовпадении значений сигнатур на выходе схемы 6 сравнения появляется сигнал «1, который через элемент 12 поступает на в---од триггера 11 и переключает его. При этом синхросигналы на входы элемента 14 и регистра 18 не поступают, а в регистре 18 фиксируется адрес (номер) несовпавшей сигнатуры. Узел 19 индицирует этот номер.

Работа блока 3 происходит следующим образом. Сигналы «Пуск и «Диагностика поступают на входы мультиплексора 22, выход которого соединен с входом схемы 23. Управление мультиплексором 22 и последовательностью инструкций в схеме 23 осуществляется соответствующими полями памяти 24. Коды маски, хранящиеся в памяти 24, пересылаются в регистр 2 (фиг. 1) в зависимости от режима работы. В режиме контроля, запускаемым сигналом «Пуск /, в схеме 23 осуществляется выбор адреса одной постоянной ячейки памяти 24 с неизменным кодом маек. В режиме диагностики на адресные входы памяти 24 поступают различные адреса ячеек памяти 24, хранящих коды масок. В зависимости от алгоритма диагностики реализуется та или иная микропрограмма и соответствующий выбор масок. Кроме кодов масок, в каждой из микрокоманд имеется поле выбора следующего адреса, поле адресов ветвления и поле управления регистром 2 и анализатором 8. Информация о выборе следующего адреса памяти 24 поступает на вход 1 схемы 23, адреса ветвления - на вход Д схемы 23. В поле управления памяти 24 содержится информация об управляющих сигналах начальной установки, разрешения записи и сдвига.

В сигнатурном анализаторе 8 (фиг. 4) определенные выходы разрядов регистра 25 соединены с группой входов сумматора 27. Эти соединения выполняют функции обратных связей. Количество обратных связей и номера разрядов регистра 25, из которых они выходят, определяют закон формирования сигнатур. В настоящее время

сигнатурные анализаторы широко применяются для диагностики неисправностей цифровых узлов и контроля неисправностей БИС,

Сигнатурный анализатор работает следующим образом.

На один из входов схемы 26 подается потенциал «О. При включении питания с помощью времязадающей цепочки 29 триггер 28 устанавливается в «О. По сигналу «Пуск регистр 25 устанавливается в начальное состояние (все разряды регистра устанавливаются в «О). На вход сумматора 27 с выхода схемы 7 поступает сигнал «1 в случае несовпадения информации на ее входах. При появлении первого из сигналов «1 на входе сумматора 27 она («еди- ница) записывается в регистр 25. При этом на выходе схемы 26 формируется сигнал «1, который переключает триггер 28 в «1. Сигнал «1 с выхода триггера 28 поступает на один из входов генератора 1 для фиксации набора t. При повторном сигнале «Пуск операция контроля повторяется и после ее окончания в регистре 25 фиксируется окончательное значение сигнатуры. Значения каждого из разрядов сигнатуры с выходов bj-bi регистра 25 поступает на один из входов схемы 6 сравнения (фиг. ), где сравнивается с эталонными значениями сигнатур, поступающими с выхода генератора 1. Каждая из этих сигнатур соответствует определенной неисправности в проверяемом узле 5. При совпа- дении значения сигнатур на выходе схемы 6 формируется сигнал «1, который подается на один из входов генератора 1. При поступлении от схемы 6 сигнала « в генераторе фиксируется номер сигнатуры. По номеру эталонной сигнатуры, совпав- шей с пол ценным значением, определяют номер неисправности в узле 5.

В схеме 17 фиксации конечного адреса (фиг. 5), если длина проверяемого теста (количество входных наборов) постоянная, то переключатели 33 не нужны. В этом слу- чае входы схем 30 совпадения группы нос 1-.rtrino подключены к выходам регистра адреса 15.

С помощью переключателей 33 входы схем 30 совпадения подключаются к тем вы- ходам разрядов регистра 15, на которых будет «1 при записи кода адреса последнего набора теста. Остальные входы схем 30 совпадения (количество входов схем 30 совпадения и количество переключателей 33 равно количеству выходов регистра 15) переключаются в положение «О и на них подается потенциал напряжения, соответствующий уровню «1.

Схема на фиг. 5 работает следующим образом. При подаче сигнала «Пуск 1 триггер 32 устанавливается в «О. С пря- мого выхода триггера 32 сигнал «О поступает на вход .элемента 14 (фиг. 2), а с инверсного выхода -- «1 на вход

элемента 13. Эти сигналы открывают доступ синхросигналов на вход регистра 15 и перекрывают их доступ на вход регистра 18 (фиг. 2). При установлении в регистре 15 кода, соответствующего адресу последнего набора теста, на все входы схем 30 совпадения будут поданы «1. На выходах схем 30 и на выходе схемы 31 появится «1, которая переключит триггер 32 в «1. С прямого выхода триггера 32 сигнал «1 будет подан на вход элемента 14 и с инверсного выхода «О - на вход элемента 13. При этом синхроимпульсы с генератора 9 поступают только на вход регистра 18. Сигнал «Пуск-1 в отличие от сигнала «Пуск устанавливает в «О триггер 32 на весь цикл контроль-диагностика (считывание набора теста из памяти 20 и эталонных сигнатур из памяти 21).

Если же в узле 5 возникли неразличимые неисправности, то в этом случае на входы проверяемого узла 5 от генератора 1 поступают последовательно входные наборы от до к. На входном наборе К, а затем на последующих наборах оператором с помощью измерительного прибора (тестера) и щупа производится поиск и локализация неисправностей известным способом.

Вне зависимости от совершенности диагностических устройств (ДУ) и качества диагностических словарей (ДС) практически окончательный поиск неисправных элементов или монтажных связей в цифровом узле (ЦУ) производится с помощью зонда человеком-оператором. От качества ДУ и ДС зависит размер определяемой области предполагаемой неисправности. При возникновении неразличимых неисправностей область предполагаемых неисправностей ЦУ оказывается весьма обширна. Размеры области значительно уменьшаются, если поиск начать с набора 1к.

Формула изобретения

1. Устройство для диагностики неисправностей цифровых узлов, содержащее блок генерации тестов, блок микропрограммного управления, регистр маски, группу элементов И и сигнатурный анализатор, вход управления сдвигом и вход начальной установки которого соединены соответственно с первым и вторым выходами блока микропрограммного управления, третий и четвертый выходы которого подключены соответственно к входу разрешения записи и информационному входу регистра маски, вход начальной установки и выход регистра маски соединены соответственно с вторым выходом блока микропрограммного управления и первыми входами элементов И группы, вход начальной установки и вход логических условий блока микропрограммного управления подключены соответственно к входу пуска и входу признака диагностики устройства, вход пуска блока генерации тестов соединен с входом пуска устройства, вторые входы элементов И группы являют- ся входом устройства для подключения к выходу проверяемого цифрового узла, а первый информационный выход блока генерации тестов является выходом устройства для подключения к входу проверяемого циф- рового узла и кроме того подключен к третьим входам элементов И группы, отличающееся тем, что, с целью повышения, точности диагностики, оно содержит две схемы сравнения, а сигнатурный анализатор выполнен в виде одноканального сиг- натурного анализатора, причем первый и второй входы и выход первой схемы сравнения соединены соответственно с первым информационным выходом сигнатурного анализатора, вторым информационным выходом блока генерации тестов и первым входом останова блока генерации тестов, первый и второй входы и выход второй схемы сравнения подключены соответственно к выходам элементов И группы, третьему информационному выходу блока генерации тес- тов и информационному входу сигнатурного анализатора, второй информационный выход которого соединен с вторым входом останова блока генерации тестов..

2. Устройство по п. 1, отличающееся тем, что блок генерации тестов содержит тактовый генератор, триггер, три элемента И, элемент ИЛИ, два регистра адреса, два узла индикации, схему фиксации конечного

адреса, память входных наборов теста и выходных эталонных наборов и память эталонных сигнатур, адресный вход и информационный выход которой соединены соответственно с выходом второго регистра адреса и вторым информационным выходом блока, адресный вход и первый и второй информационные выходы памяти входных наборов теста и выходных эталонных наборов подключены соответственно к выходу первого регистра адреса, к первому и третьему информационным выходам блока, вход и выход тактового генератора соединены соответственно с входом пуска блока и первым входом первого элемента И, вход установки и выход триггерыа подключены соответственно к входу пуска блока и второму входу первого элемента И, выход которого соединен с первыми входами второго и третьего элементов И, первый и второй входы и выход элемента ИЛИ соединены соответственно с первым и вторым входами останова и входом сброса триггера, первый и второй входы и первый и второй выходы схемы фиксации конечного адреса подключены соответственно к выходу первого регистра адреса, входу пуска блока, второму входу второго элемента И и второму входу третьего элемента И, выходы второго и третьего элементов И соединены с информационным входом соответственно первого и второго регистров адреса, входы начальной установки которых подключены к входу пуска блока, а входы первого и второго узлов индикации соединены с выходами соответственно первого и второго регистров адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля многовыходных цифровых узлов | 1984 |

|

SU1246099A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

Изобретение относится к вычислительной технике и может быть использовано для диагностики неисправностей цифровых узлов. Целью изобретения является повышение точности диагностики. С этой целью в устройство, содержащее генератор тестов, блок микропрограммного управления, регистр маски, группу элементов И и сигнатурный анализатор, введены две схемы сравнения. Сигнатурный анализатор выполнен в виде одноканального сигнатурного анализатора. 1 з.п.ф-лы, 5 ил.

Диаеност. Ъ

гт

От С С1-6 От С А-8

Диагностика.

На ЦУ и cx.U(SuS)

М

На ее 2-7

Нассп

Фие.г

БПУ

Гс У

А 24

Ни ч у cm он

Код маска

Разреш зал сдвие .

Составитель Г. Виталиев

Редактор С. ПатрушеваТехред И. ВересКорректор М. Васильева

Заказ 2691/50Тираж 669Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГК.НТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-издательский комбинат «Патент, г. Ужгород, ул. Гагарина, 10

фие. 4

Фиа. 5

| Устройство для контроля многовы-ХОдНыХ цифРОВыХ узлОВ | 1979 |

|

SU817721A1 |

| Устройство для функционального контроля многовыходных цифровых узлов | 1984 |

|

SU1246099A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-06—Подача