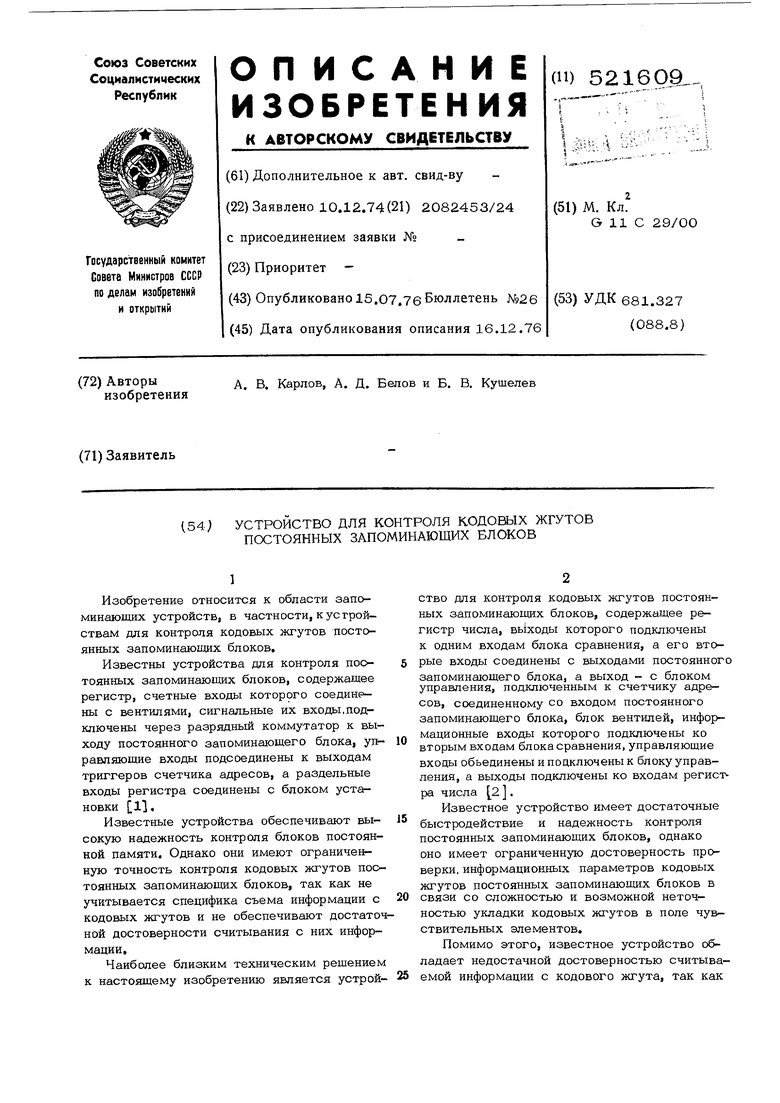

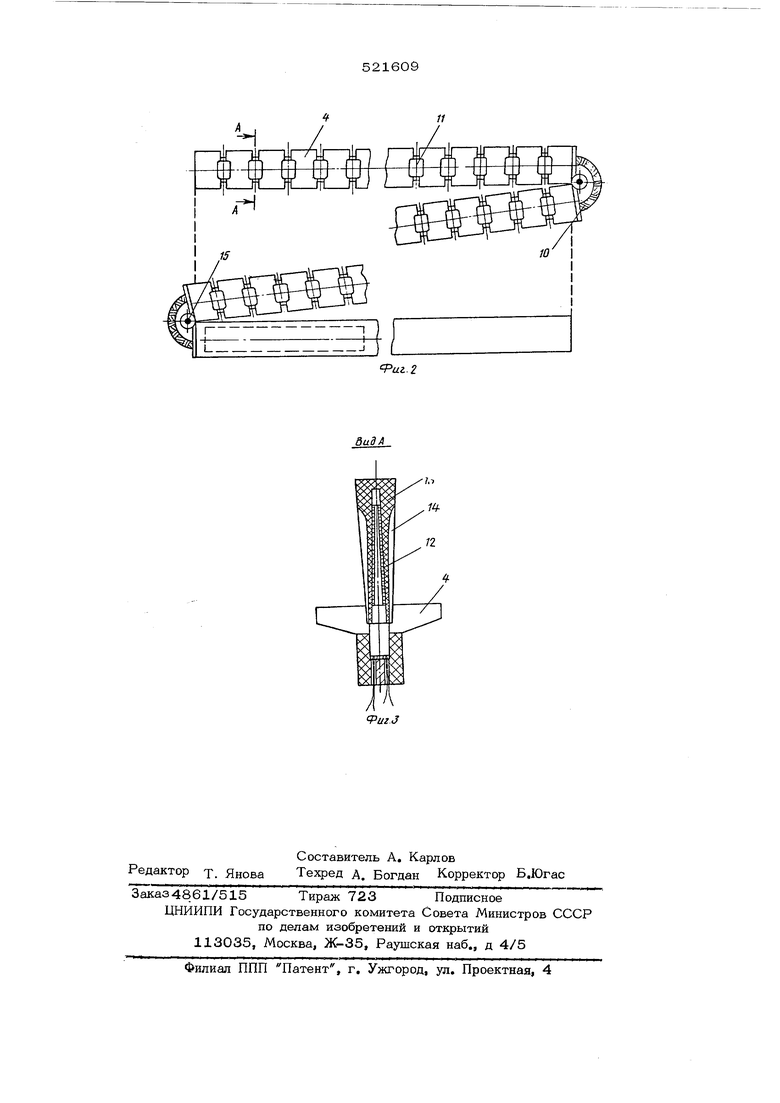

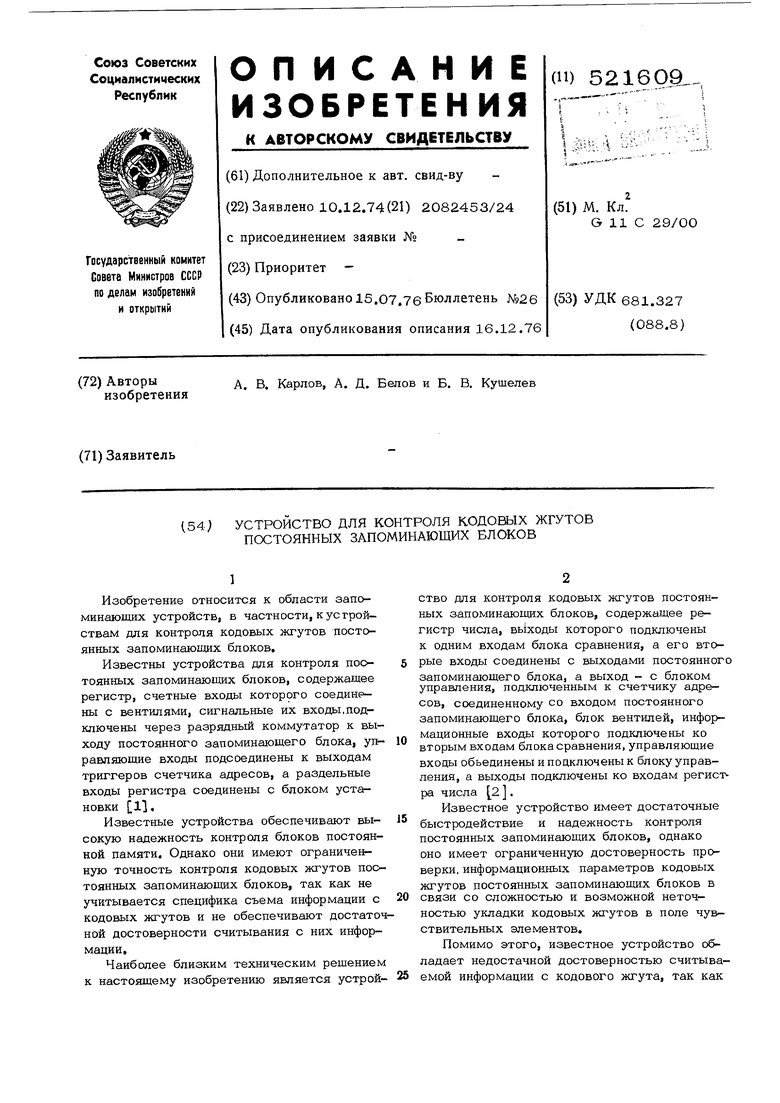

считываемая информация зависит от целест ности сердечников, плотности прижатия ярм к сердечнику , зависимсхзти достоверности информации от параметров магнитопровода. Кодовый жгут при проверке на известном устройстве может быть поврежден (обрыв, нарушение изоляции, замыкание кодовых ши между собой и т.п.) в результате укладки его в поле сердечников, замыкания магнито провода и при извлечении жгута из последнего. С целью повышения надежности работы устройства, точности и достоверности результатов контроля оно содержит блок интегрирования и блок компенсации помех, входы которого подключены к соответствующим выходам программного блока и адресного коммутатора, а выходы - к входам блока воспроизведения и адресного коммутатора и первым входам блока интегрирования и дискриминатора, выход блока воспроизведения через последовательно соединенные коммутатор разрядов и блок дифференци альных усилителей подключен к второму вхо ду блока интегрирования, второй вход диокриминатора подключен к выходу блока инте рирования, а выход - к второму входу блока сравнения. На фиг. 1 изображена схема предлагаемо го устройства ; на фиг. 2 - общий вид воспроизведения ; на фиг. 3 - индуктивный датчик. Устройство для контроля кодовых жгутов постоянных запоминающих блоков содержит программный блок 1, подключенный к адресному коммутатору 2 и первому входу и выходу блока 3 сравнения, блок 4 воспроизведения, коммутатор 5 разрядов, блок 6 дифференциальных усилителей, блок 7 интегрирования, дискриминатор 8, блок 9 компенсации помех, соединенный с проверяемым кодовым жгутом 1О. Входы блока 9 компенсации помех подклю

чены к соответствующим выходам программного блока 1 и адресного коммутатора 2, а выходы - к входам блока 4 воспроизведения, адресного коммутатора 2, первым входам блока 7 интегрирования и дискриминатора 8. Выход блока 4 воспроизведения через последовательно соединенные коммутатор 5 разрядов и блок 6 дифференциальных усилителей подключен к второму входу блока 7 интегрирования, второй вход дискриминатора 8 подключен к выходу блока 7 интегрирования, а выход - к второму входу блока 3 сравнения

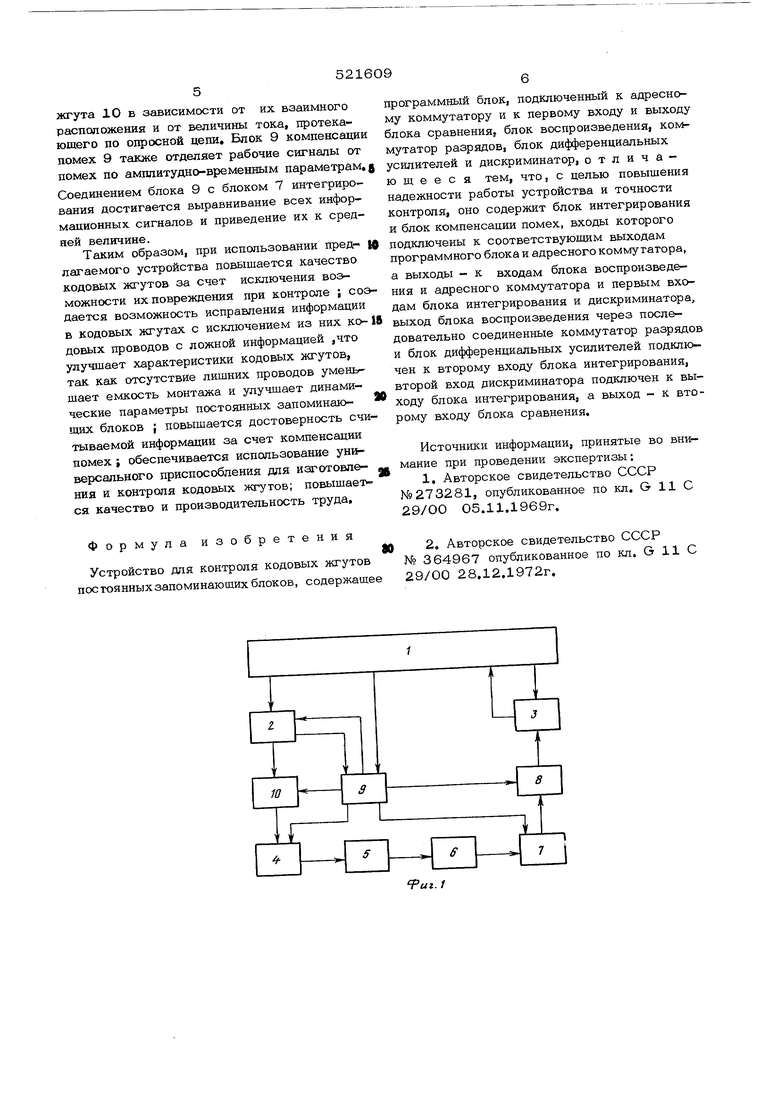

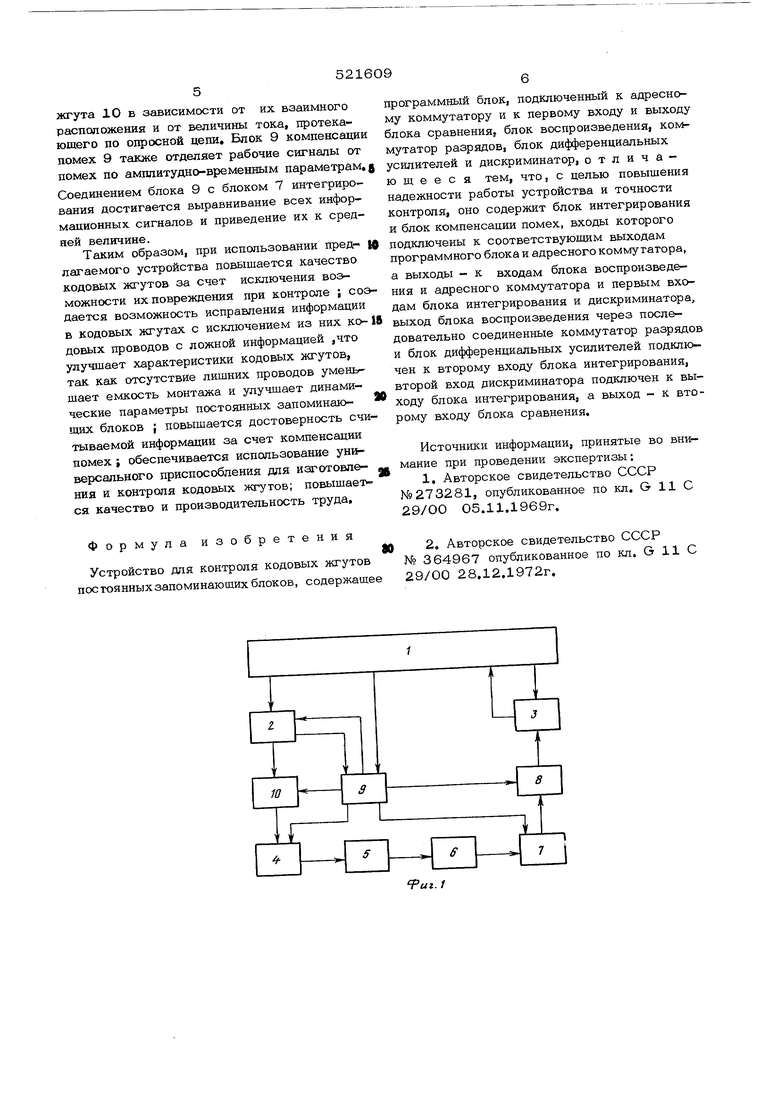

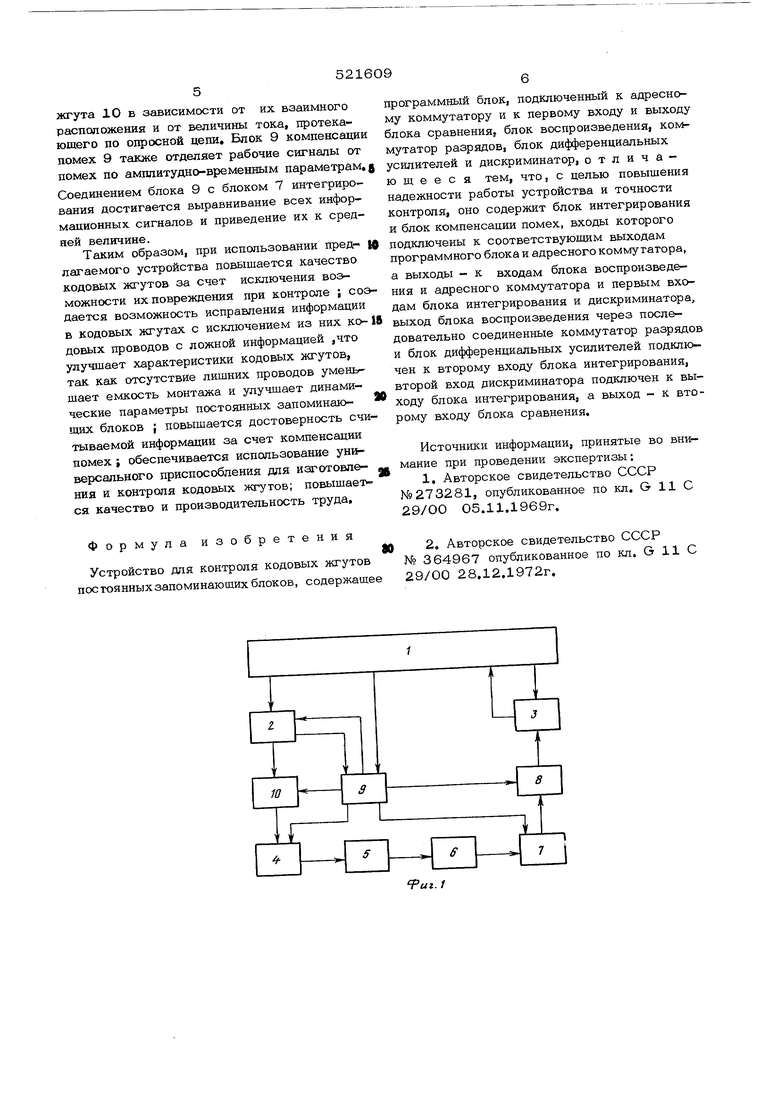

Блок 4 воспроизведения выполнен (фиг 2 и 3) в виде набора индук тивных датчиков 11,

ным программным блоком 1. При однозначном соответствии информации, считанной с кодового жгута 10, и эталонной информации, блк 3 сравнения выдает соответствующую команду на переход к проверке следующего информационного участка кодового жгута 10.

С целью выравнивания токов опроса, для обеспечения равнозначной передачи разрядных сигналов с кодового жгута 10 на блок 4 воспроизведения и для исключения зависимости параметров сигналов от положения выбранной разрядной шины кодового жгута 10 в цепь опроса разрядных шин включен выход блока 9 компенсации помех, выравнивающего сигналы опроса между кодовыми шинами на которых размещены проверяемый кодовый жгут 10. Каждый из датчиков 11 содержит по две бифилярные обмотки 12, Начало первой и конец второй обмоток 12 объединены, закрыты защитными колпачками 13, имеющими вертикальные прорези 14 для обвяэки кодовых жгутов lOf а группы диэлектрических индуктивных датчиков 4 соединены посредством шарниров 15 в последовательную цепь. Устройство для контроля кодовых жгутов постоянных запоминающих блоков работает следующим образом. Прогаммный блок 1 выдает на адресный коммутатор 2 код адреса числовой шины кодового жгута 10, по которому адресный коммутатор 2 посылает импульс тока опроса. В зависимости от того, с какой стороны от датчика 11 проходит выбранная числовая шина кодового жгута 10, на обмотках 12 наводятся разнополярные сигналы. определяющие заложенную в жгут информацию, соответствующуюсостоянию . На один из индуктивных датчиков 11 (среднююточку обмоток 12) подается с адресного коммутатора 2 импульс стробирования, выво коммутатор 5 разрядов усили-. ° ° ствительную к сигналам выбранной группы индуктивных датчиков 11, Сигналы с других (невыбранных) индуктивных датчиков 11 не поступают на усилители блока 6 за счет запирающего действия сигналов коммутатора 5 разрядов. Информационные сигналы, предварительно усиленные блоком 6, поступают в блок 7 интегрирования, в котором они преобразуются в однопол)ярный сигнал, а затем поступают на вход дискриминатора 8, с выхода последнего информационные сигналы поступают в блок 3 сравнения, определяющий соответствие этих сигналов сигналам, заданжгута 10 Б зависимости от их взаимного расположения и от величины тока, протекающего по опрсйной цепи. Блок 9 компенсации помех 9 также отделяет рабочие сигналы от помех по амплитудно-временным параметрам, j Соединением блока 9 с блоком 7 интегрирования достигается выравнивание всех информационных сигналов и приведение их к средней величине. Таким образом, при использовании предлагаемого устройства повышается качество кодовых жгутов за счет исключения возможности их повреждения при контроле ; соз дается возможность исправления информации в кодовых жгутах с исключением из них кодовых проводов с ложной информацией ,что улучшает характеристики кодовых жгутов, так как отсутствие лишних проводов уменьшает емкость монтажа и улучшает динамические параметры постоянных запоминающих блоков ; повышается достоверность считываемой информации за счет компенсации помех ; обеспечивается использование универсального приспособления для иаготовления и контроля кодовых жгутов; повышает ся качество и производительность труда. Формула изобретения Устройство для контроля кодовых жгутов посгоянныхзапоминаюшихблоков, содержаш ее

программньтй блок, подключенный к адресному коммутатору и к первому входу и выходу блока сравнения, блок воспроизведения, Koivtмутатор разрядов, блок дифференциальных усилителей и дискриминатор, отличающееся тем, что, с целью повышения надежности работы устройства и точности контроля, оно содержит блок интегрирования и блок компенсации помех, входы которого подключены к соответствующим выходам программного блока и адресного коммутатора, а выходы - к входам блока воспроизведения и адресного коммутатора и первым входам блока интегрирования и дискриминатора, выход блока воспроизведения через последовательно соединенные коммутатор разрядов и блок дифференциальных усилителей подключен к второму входу блока интегрирования, второй вход дискриминатора подключен к выходу блока интегрирования, а выход - к второму входу блока сравнения. Источники информации, принятые во внимание при проведении экспертизы: 1, Авторское свидетельство СССР N9273281, опубликованное по кл, G 11 С 29/ОО 05,11,1969г, 2. Авторское свидетельство СССР № 364967 опубликованное по кл. G 11 С 29/ОО 28,12,1972г,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля кодовых жгутов постоянного запоминания блока | 1974 |

|

SU514348A1 |

| Устройство для автоматическогоКОНТРОля элЕКТРичЕСКиХ цЕпЕй | 1979 |

|

SU842640A1 |

| Способ контроля прошивки кодовых жгутов постоянного запоминающего устройства и устройство для его осуществления | 1984 |

|

SU1247950A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU886059A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU622175A2 |

| Устройство для контроля блоков памяти | 1975 |

|

SU526954A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

Авторы

Даты

1976-07-15—Публикация

1974-12-10—Подача