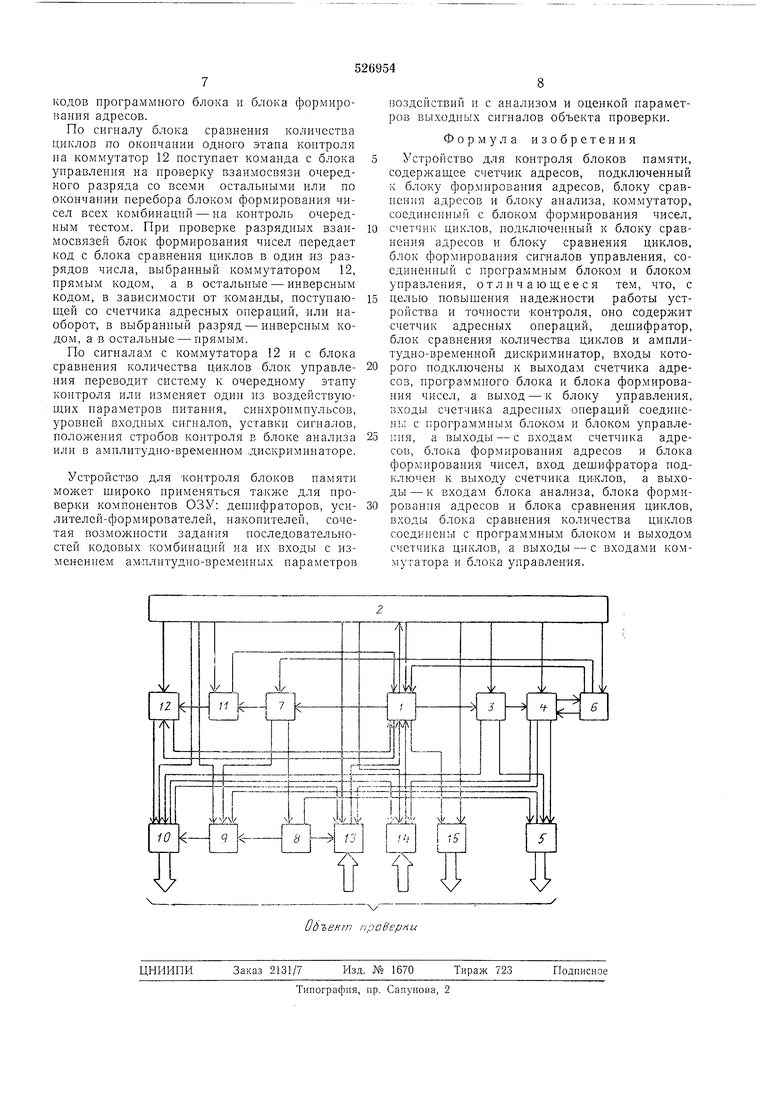

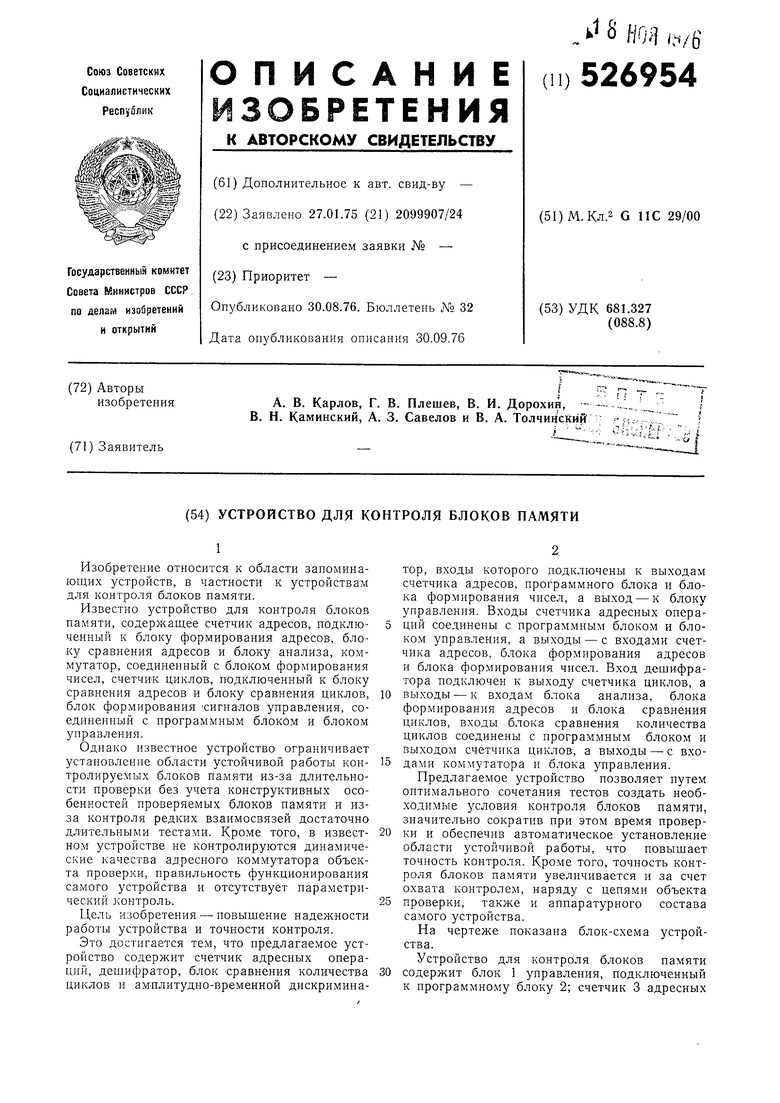

операций, соединенный с блоком управления, программным блоком 2 и счетчиком 4 адресов, который соединен с программным блоком 2, блоком 5 формирования адресов и блоком 6 сравнения адресов, подключенным к программному блоку 2 и к счетчику циклов, который соединен с блоком управления, а также непосредственно и через дешифратор 8 с блоком 9 сравнения циклов, соединенным с блоком формирования адресов, с программным блоком и с блоком 10 формирования чисел, который подключен также к счетчику адресных операций и к программному блоку; блок И сравнения, количества циклов, соединенный со счетчиком циклов, блоком управления, программным блоком и коммутатором 12, который подключен к программному блоку, к блоку управления и к блоку формирования чисел, соединенному также с блоком 13 анализа и с амплитудно-временным дискриминатором 14, каждый из которых подключен к программному блоку, а блок анализа дополнительно подключен к счетчику адресов; блок 15 формирования сигналов управления, соединенный с программным блоком и с блоком управления; блок формирования адресов соединен со счетчиком адресных операций и с дешифратором. Предлагаемое устройство производит тестовый контроль взаимосвязей между адресными ячейками и между разрядами блоков памяти, контроль работоспособности адресного коммутатора, расположенного в объекте, проверки, а также динамический контроль амплитудно-временных параметров с установлением области устойчивой работы. При этом устройство позволяет проверять блоки памяти динамическими тестами «бегаюпхая «1 или «О, «шахматный порядок и переменное циклирование. Тесты «бегающая «1 или «О проверяют надежность хранения информации в каждой ячейке при многократном обращении ко всем ячейкам заданного поля адресов и взаимосвязь между адресными ячейками. Этот тест является наиболее тяжелым тестом для работы усилителей воспроизведения, что позволяет наиболее полно судить о работоспособности запоминающих устройств. Недостатком теста является его большой объем, что не позволяет производить многократные проверки данным тестом для установления области устойчивой работы объекта проверки, особенно нри lipoBepKe блоков памяти большой емкости. Тест «шахматный порядок (чередование циклически-переменного количества единиц и нулей) не позволяет выявлять некоторых редких взаимосвязей между ячейками памяти, однако применение этого теста дает возможность оценить работоспособность большеобъемных блоков памяти за приемлемое время и с установлением области устойчивой работы. Совмещение теста «шахматный порядок с тестами «бегающая «1 или «О в рациональном соотношении позволяет за относительно короткое время производить оптимальную оценку блоков памяти. Например, при проверке адресных взаимосвязей тестом «бегающая «1, а разрядных - тестом «шахматный порядок, обеспечивается оптимальный контроль всех возможных взаимосвязей с резким уменьшением времени проверки, что полезно при установлении области устойчивой работы блоков памяти. Сокращение времени проверки с обеспечением достаточной точности контроля получается также при проверке блоков памяти, состоящих из нескольких конструктивно законченных накопителей. При этом целесообразно контроль взаимосвязей внутри каждого накопителя проводить тестом «бегающая единица, а взаимосвязи между накопителями могут выявляться значительно коротким тестом «шахматный порядок. Тест «переменного циклирования (с произвольно выбранным положением единиц и нулей в поле адресов) является специальным тестом для проверки конкретных взаимосвязей между определенными группами элементов памяти и позволяет судить о работоспособности блоков памяти в заданных конкретных ситуациях. На разных этапах создания блоков памяти и их эксплуатации (лабораторно-отработочных испытаниях и исследованиях возможностей, типовых, приемо-сдаточных и периодических испытаниях) необходимо иметь различные по глубине данные об их работоспособности, для чего ограничивают полноту контроля тем или иным тестом, с той или иной степенью достоверности результатов контроля, достаточными для каждого конкретного случая. Устройство для контроля блоков памяти работает следующим образом. Блок управления по команде с программного блока посылает сигналы «+1 в счетчик адресных операций, модуль пересчета в котором установлен программным блоком в соответствии с тестом проверки и с выбранным видом проверки (проверка накопителя, усилителей воспроизведения, адресного коммутатора объекта проверки), а также в соответствии с типом объекта проверки (блок памяти, накопитель, дешифратор и т. д.) и в зависимости от заданной полноты контроля (от этапа контроля). Блок формирования адресов производит поочередную выдачу адресов в объект проверки в соответствии с кодом счетчика адресов, начальное состояние в котором (начальный адрес) установлено программным блоком. В зависимости от команды, выдаваемой счетчиком адресных операций, и в соответствии с состоянием дешифратора, в свою очередь зависящего от состояния счетчика циклов( от порядкового номера цикла), блок формирования адресов осуществляет преобразование кода счетчика адресов, обеспечивая необходимый порядок перебора ячеек объекта проверки (естественный, многократный, чередование выбора ячеек с прямым и инверсным соотношением адресоБ и разрядов адреса и т. д.).

Обращение к той или иной ячейке памяти в необходимом режиме (записи, считывания, считывания без регенерации и т. д.) осуществляется посредством сигналов, выдаваемых блоком 15 формирования сигналов управления по командам блока управления и проггамА ного блока.

Счетчик адресов производит пересчет ячеек памяти, к которым производилось обращение, в естественном порядке. Начальный и конечный адреса, задаваемые программным блоком соответственно счетчику адресов и блоку сравнения адресов, определяют поле контролируемых ячеек памяти каждого этапа проверки (цикл проверки). При переходе от одного цикла проверки к другому счетчик циклов осуществляет пересчет этих циклов. В зависимости от типа проверяемого блока и от вида проверок производится задание программпым блоком 2 в блок сравнения количества циклов кода, по достил :епии которого счетчиком циклов в блок управления выдается команда на переход к следующему этапу контроля. ОдЕоврелтенно выдается в коммутатор 12 команда на изменение порядка следования разрядов числовой информации, записываемой -в проверямый блок памяти блоком формирования чисел.

В первом цикле обращение к выбранному полю адресов производится в режиме «запись. На блок формирования чисел поступает сигнал с блока сравнения циклов, являющийся признаком наличия во всех разрядах числа одних единиц либо нулей.

Блок сравнения циклов имеет соединение с блоком формирования адресов, код которого сравнивается или с кодо.м счетчика циклов или с кодом программного блока, а разряды, участвующие в сравнении, задаются программным блоком или дешифратором.

Бели программный блок задает режим контроля «щахматный порядок, то в блоке сравнепия циклов сравниваются коды блока формирования адресов и программного блока, а разряды сравнения задаются дешифратором.

В случае реализации режима «бегающая «1 или «О в блоке 9 сравнения циклов сравниваются коды блока 5 формирования адресов и счетчика циклов, а разряды сравнения задаются программным блоком 2. Нри исключении из сравнения старших разрядов изменяется период следования «изолированных единиц либо «нулей, а исключая младщие разряды из сравнения, изменяется количество «единиц в каждой группе, количество которых в заданном поле адресов определено старшими разрядами.

Для осуществления режима «переменного циклироваипя код сравнения я разряды сравнения задаются программным блоком 2 каждый раз при переходе от одного цикла «запись - считывания по всему заданному

полю адресов к другому циклу. Кроме этого, при переменном циклированпи в формировании чисел принимает участие счетчик адресных операций, изменяю1ЦИ кодовую комбинацию в заданных разрядах с прямой на пиверсную и. наоборот, од -1с;;ременно со сменой адреса в блоке формирования адресов при неизменном состоянии счетчика адресов. Нерсмениое циклирование задает снециальные режимы работы, необходимые при исследовании работоспособности блоков па.мятп на этапе их лабораторно-отработочных испытаний, а также для создания необходимых проверок компонентов блоков памяти.

После осуществления цикла «запись по всему полю адресов блок управ.тения по сигналу блока срав 1ения адресов переводит систему на режим «Считывание, посылая соответствующий сигнал в блок формирования сигналов управления и разрешая работу блока анализа и амплитудно-временного дискриминатора.

Блок анализа осуществляет в каждом цикле обращения сравнение кодов из блока памяти с кодами, поступающими с блока формирования чисел, в режиме «бегающая «1 или «О, а также с кодом счетчика адресов и командами дещифратора в режиме «шахматный порядок и в режиме «переменного циклирования. В последнем случае происходит охват контролем аппаратурного состава самого устройства, что повышает точность контроля, и в случае возникновения неисправностей разграничивает неустойчивую работу блока памяти от устройства.

Амплитудно-временной дискриминатор 14 производит в цикле считывания из блока памяти оценку амплитудно-временных параметров в заданный программным блоком момент: амплитуды «единицы и «нуля и периода обращения амплитуды единичного и нулевого сигналов в соответствии с эталонной эпюрой или уровней «единицы и «нуля, задаваемыми программным блоком 2, и в соответствии с признаками «больще - «меньше, указываемыми блоком управления. То есть, наряду с установлением факта неисправности в предлагаемом устройстве производится установление характера неисправности в динамическом непрерывном режиме, что резко повышает точность результатов контроля по сравпепию с результатами, получаемыми при проверке блоков памяти известными устройствами и системами.

В случае отсутствия сигналов «Брак с блока анализа и с амплитудно-временного дискримипатора к содержимому счетчика циклов после окопчания цикла обхода заданного поля адресов прибавляется «I, и цикл запись - считывание продолжается. При этом в режиме «бегающая «1 или «О информация перемещается на один адрес. В режиме «шахматный порядок информация является функцией сравнения следующего (старшего) разряда, выбираемого дешифратором, и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU711636A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1513523A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1348912A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

Авторы

Даты

1976-08-30—Публикация

1975-01-27—Подача