; , , 1. ;

Изобретение относится к запоминающим устройствам и может быть исполь зовано для контроля кодовых жгутов блоков постоянной памяти. .,. Известно устройство для контроля блоков постоянной памяти, содержащее блок считывания счётчик адреса, схему сравнения, блок синхронизации и буферную память, в которых контроль достигается сравнением информации контролируемого объекта с информацией, нанесенной на программоноситель или предварительно размещенной в устройстве 13Недостатком этого устройства является жёсткий формат эталонного слова, что приводит к увеличению ёмкости накопителя ЗУ и повышению стоимости устройства контроля.

Наиболее близким к предлагаемому по текническойсущности является усгройтво для контроля блоков постоянной памяти, содержащее блок считывания информации, блок очерёдности ввода, адресный блок, блок анализа ошибок.

дополнительный счетчик, блок управления очередностью ввода, блок задания режиг мов проверки и блок сИнхроимпуяьсовГ2.Недостатками этого устройства являются низкая надёжность вследствие трудоёмкости процесса контроля, а также постоянная разрядность эталонного слова, что снижает возможности его применения при различных типах кодовых жгутов в контролируемых блоках постоянной памяти.

Цель изобретения - повьшение надёжности устройства.

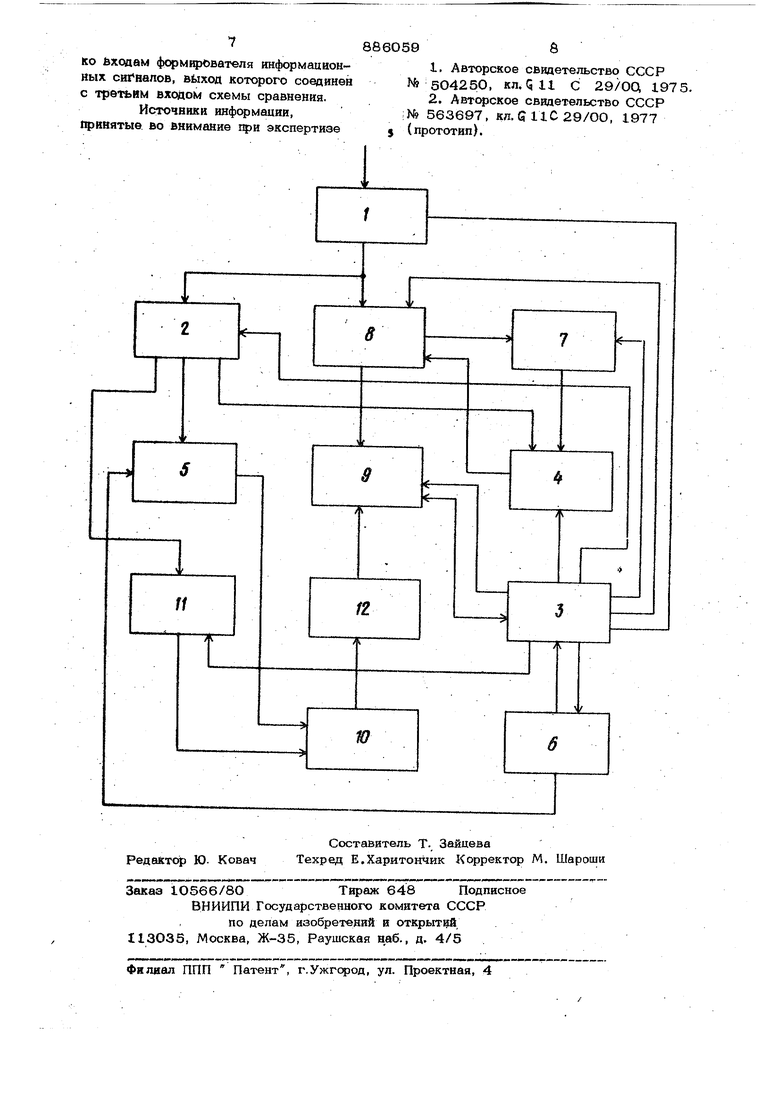

.Поставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее блок ввода контрольных сигналов, формирователь адресных сигналов, блок ухравления, схему сравнения, накопитель и первый блок местного управления, причём выход блока ввода контрольных сигналов подключен к первому входу формирователя адресных сигналов, а первый вход - к первому выходу блока управления, второй Выход которого соединен со вторым входом формирователя адресных, сигналов, третий выход,и первый вход соединены соответгственно с первым входом и выходом первого блока местного управления, а четвёртый выход и второй вход соответственно с первыми входом и выходом схемы сравнения, первый и второй входы накопителя подключены соответственно к пятому выходу блока управления и первому выходу формирователя адресных сигналов, второй вход блока ввода контрольных сигналов является входом устройства, введены группа индуктивных датчиков, группа генераторов токовых импульсов, формирователь контрольных сигналов, формирователь информационных сигналов, распределитель сигналов и второй блок местного управлении, причем первый вход формирователя контрольных сигналов подключен к первому выходу распределителя сигналов, второй вход - к шестому выходу блока управления, а выход - к третьему входу накопителя, первый, второй и третий входы распрецелигеля сигналов соединены соответственио с выходом блока входа контрольных сигналов, с выходом накопителя и с седьмым выходом блока управления, а выход распределителя сигналов подклю чен ко второму входу схемы сравнения, один из входов генераторов токовых импульсов группы соединены со вторым вы ходом первого блока местного управлени другие входы - со вторым выходом формирователя адресных сигналов, а выходы с одними из входов индуктивных датчико группы, другие входы которых подключены к выходу второго блока местного управления, первый и второй входы которого соединены соответственно с трет им выходом формировагеля адресных сигнал и с восьмым выходом блока управления, вых индуктивных датчиков группы подключены ко входам формирователя информационны сигналов, выход которого Соединен с третьим входом схемы сравнения. На чертеже изображена функциональна схема предлагаемого .устройства. Устройство содержит блок 1 ввода контрольных сигналов, формирователь 2 адресных сигналов, блок 3 управления, накопитель 4, труппу 5 генераторов токовых импульсов, первый блок б местного управления, предназначенный для синхронизации работы устройства, форми рователь 7 контрольных сигналов, распределитель 8 сигналов, схему 9 сравнения, группу 10 индуктивных датчиков, второй блок 11 местного управления, 594 предназначенный аля регулирования чувствительности индуктивных датчиков, и формирователь 12 информационных сигналов. Выход блока 1 ввода контрольных сигналов подключен к первому входу формирователя 2 адресных сигналов, а первый вход - к первому выхоау блока 3 управления. Второй вход блока 3 управления соединен со вторым входом формироьагеля 2 адресных сигналов, третий выход и первый вход соединены соответственно с первыми вхс(дами и выходом первого блока 6 местного управления, а четвертый выход и второй вход - соответственно с первыми входом и выходом схемы 9 сравнения. Первый и второй входы накопители 4 подключены соответственно к пятому выходу блока 3 управления, и к первому выходу формирователя 2 адресных сигналов. Первый вход формирователя 7 контрольных сигналов подключен к первому выходу распределителя 8 сигналов, второй вход - к шестому выходу блока 3 управления, а выход - к третьему входу накопителя 4. Первый, второй и третий входы распределителя 8 сигна лов соединены соответственно с выходом блока 1 ввода контрольных сигналов, с выходом накопителя 4 и седьмым входом блока 3 управления. Выход распределит.еля 8 сигналов подключен ко второму вхору схемы 9 сравнения. Одни из входов генераторов токовых импульсов группы 5 соединены со вторым выходом первого блока 6 местного управления, другие входы - со вторым выходом формирователя 2 адресных сигналов, а выходы - с одними из входов индуктивных датчиков группы 10, другие входы которой подключены к выходу второго блока 11 местного управления. Первый и второй входы второго блока 11 местного управления соединены соответственно с третьим выходом формирователя 2 адресных сигналов и с восьмым выходом блока 3 управления. Выходы индуктивных датчиков группы 1О подключены ко входам формирователя 12 информационных сигналов, выход которого соединен с третьим входом схемы 9 сравнения. Второй вход блока 1 ввода контрольных сигналов лвляется входом устройства. Вход устройства подключается к программоносителю (не показав). Выходы генераторов токовых импульсов группы 5 подключаются к контролируемому кодовому жгуту блока .постоянной памяти, кото|:)Ь1Й укл дываетс ; на сердечники игщуктивных датчиков группы 1О. Устройство работает следующим образ Блок 3 управлении задаёт режим проверки. В результате протекания импульсного тока по выбранному проводу контролируемого кодового жгута в индуктивных датчиках группы 10 формируются си1налы в соответствии с кодом заложен ного в них кодового жгута. Регулировке чувствительности индуктивных датчиков группы 10, осуществляемаи вторым блоком 11 местного управлении, повышает достоверность считываемой с кодового жгута информации, исключа, ложные ерабатывания индуктивных датчиков группы 10 от тока помехи. Сигналы с индуктивных датчиков группы 1О поступают в формирователь 12. информационных сигналов, гце формируется число в цвоичном коце, которое пос тупает на вход схемы 9 сравнения, на другой вход которой поступает число со второго входа распределителя 8 сигналов

Контроль правильности прошивки кодового жгута производите ; по контрольной информации, поступающей с программоносителя в блок 1 ввода контрольных сигналов и далее в распределитель 8 сигналов. С выхода распределителя 8 сигналов контрольные числа поступают на схему 9 сравнения и одновременно через формирователь 7 контрольных сигналов в накопитель 4. Если при записи в накопитель 4 цлина слова превышает разр 1дность оддой ячейки, то дли записи в один цикл обращения подключается более одной ячейки. При считываний данного слова опрашивается одновременн несколько ячеек накопител. 4. Если в процессе контроля не обнаружено ошибок в, прошивке кодового жгута, то проверка заканчивается после опроса провода, имеющего последний адрес.

Записанная в накопитель информация используется для последующих проверок кодового жгута без ввода контрольной информации с программоносителя. При обнаружении ошибки дальнейший код контрольных чисел в накопитель 4 прекращается и работа устройства перестраивается на режим долбления со считыванием информации с накопителя 4, и продолжается до исправления ошибки или исключения провода из кодового жгута.

Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надёжности , а также в обеспечении возможности конвёртый выход и второй вход - соответственно с первыми входом и выходом схемы сравнения, первый и второй входы накопителя подключены соответственно к пятому выходу блбка управления и к первому выходу формирователя адресных сигналов, . второй вход блока ввоца контрольных сигналов является входом устройства, отличающееся тем, что, с целью повышения надёжности устройства, оно, содержит группу индуктивных датчиков, группу генераторов токовых импульсов, формирователь контрольных сигналов, формирователь информационных сигналов, распределитель сигналов и второй блок местного управления,

тричем первый вход формирователя контрольных сигналов подключен к

первому выходу распределителя сигналов. второй вход - к .шестому выходу блока управлени 5, а выход - к третьему входу накопителя, первый, второй и третий входы распределители сигналов соединены соответственно с выходом блока ввода контрольных сигналов, с выходом накопителя и с седьмым выходом блока управления, а выход распределителя сигналов подключен ко второму входу схемы сравнения, одни из входов генераторов токовых импульсов группы соединены со вторым выходом первого блока местного управления, другие входы - со вторым выходом формирователя адресных сигналов, а выходы - с одним из входов индуктивных (Датчиков группы, другие входы которых подключены к выходу второго блока местного управления, первый и второй входы которого соединены соответственно с третьим выходом формирователя адресных сигналов я с восьмым выходом блока управления, выходы индуктивных датчиков группы подключены троля различных типов кодовых жгутов блоков ПОСТО/1НПОЙ памяти. Формула изобретения Устройство для контроля блоков постоянной памяти, содержащее блок ввода контрольных сигналов, формирователь адресных сигналов, блок управления1 схему сравнения, накопитель и первый блок мест ного управления, причём выход блока ввода контрольных сигналов подключен к шервомУ входу формирователя адресных сигналов, а первый вход - к первому входу блока управления, второй выход которого соединен со вторым входом формирователи адресных сигналов, третий выход и первый вход соединены соответственно с первыми входом и выходом первого блока местного управления, а четко бхолам 4н:рм1фс вателя информационных сигнапов, Bbixoa которого соединен с TpetbHM входом схемы сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

N 5О4250, кл. Q11 С 29/OQ 1975.

2.Авторское свидетельство СССР ;№ 563697, кл. G ИС 29/ОО, 1977

5 (прототип).

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для управления прошивкой постоянных накопителей | 1979 |

|

SU894788A1 |

| Устройство изготовления кодовых жгутов для постоянных накопителей | 1977 |

|

SU736168A1 |

| Устройство для контроля кодовых жгутов постоянных запоминающих блоков | 1974 |

|

SU521609A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU1023398A1 |

| Устройство для контроля металлизированных переходов печатной платы | 1985 |

|

SU1308955A1 |

| Устройство для контроля кодовых жгутов постоянного запоминания блока | 1974 |

|

SU514348A1 |

4

б

Авторы

Даты

1981-11-30—Публикация

1980-02-11—Подача