(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Преобразователь кода Фибоначчи в двоичный код | 1986 |

|

SU1432789A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

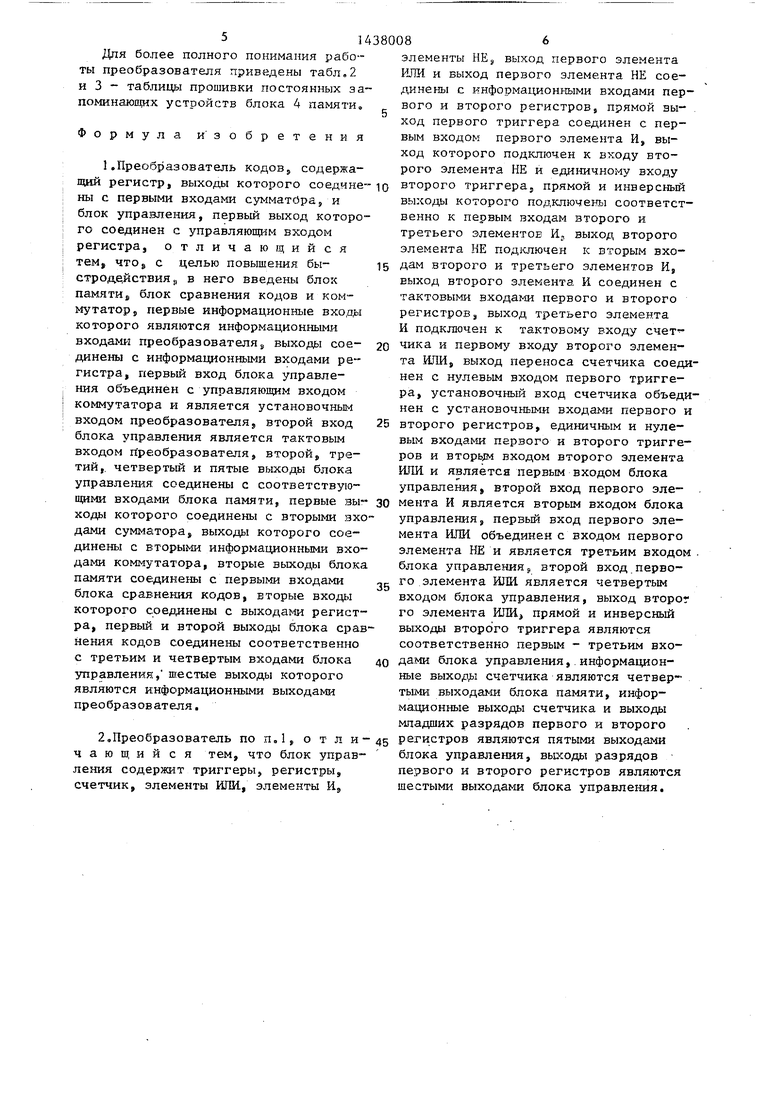

Изоб ретение относится к вычислительной технике и может быть использовано для преобразования двоич ного кода в код Фибоначчи. Целью изобретения является повышение быстродействия. Преобразователь содержит коммутатор 1, сумматор 2, регистр 3, блок 4 памяти, блок 5 сравнения кодов, блок 6 управления. 1 з.п. ф-лы, 3 табл., 3 ил.

fflLi

lz

4:

СО 00

00

9U2.1

Изобретение относится к вычнслк- тельной технике и может быть использовано для преобразования двоичного кода в код Фибоначчи.

Цель изобретения - повьшение быстродействия преобразователя.

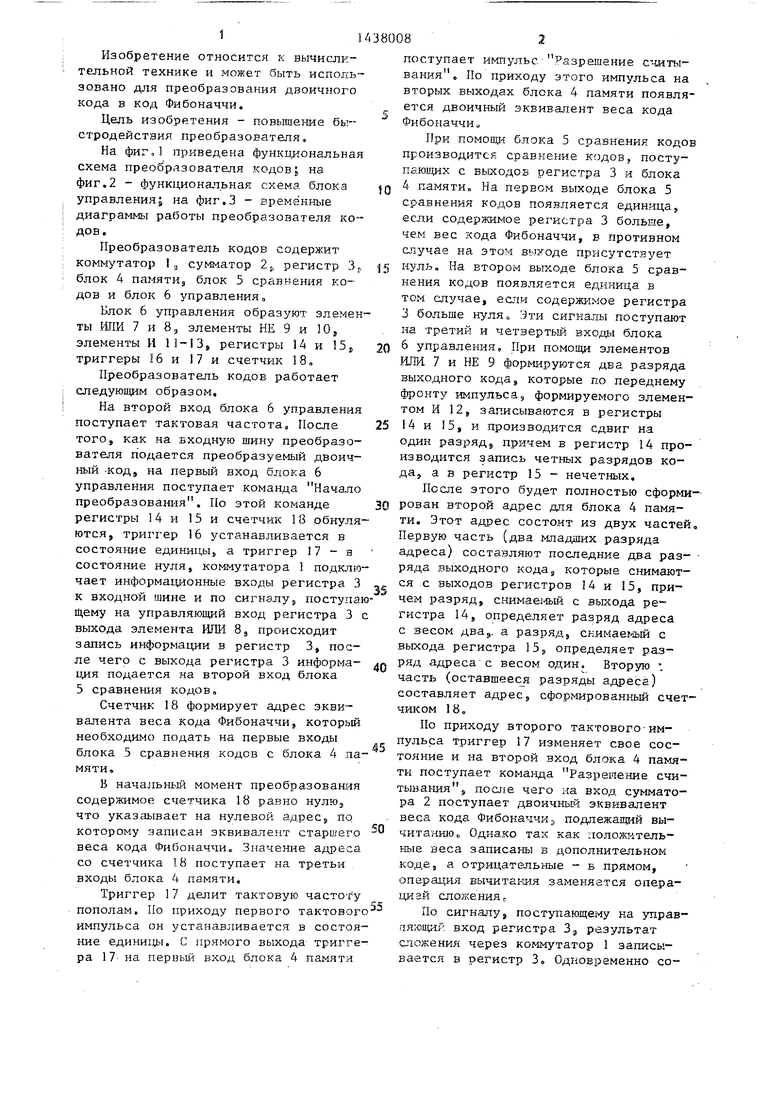

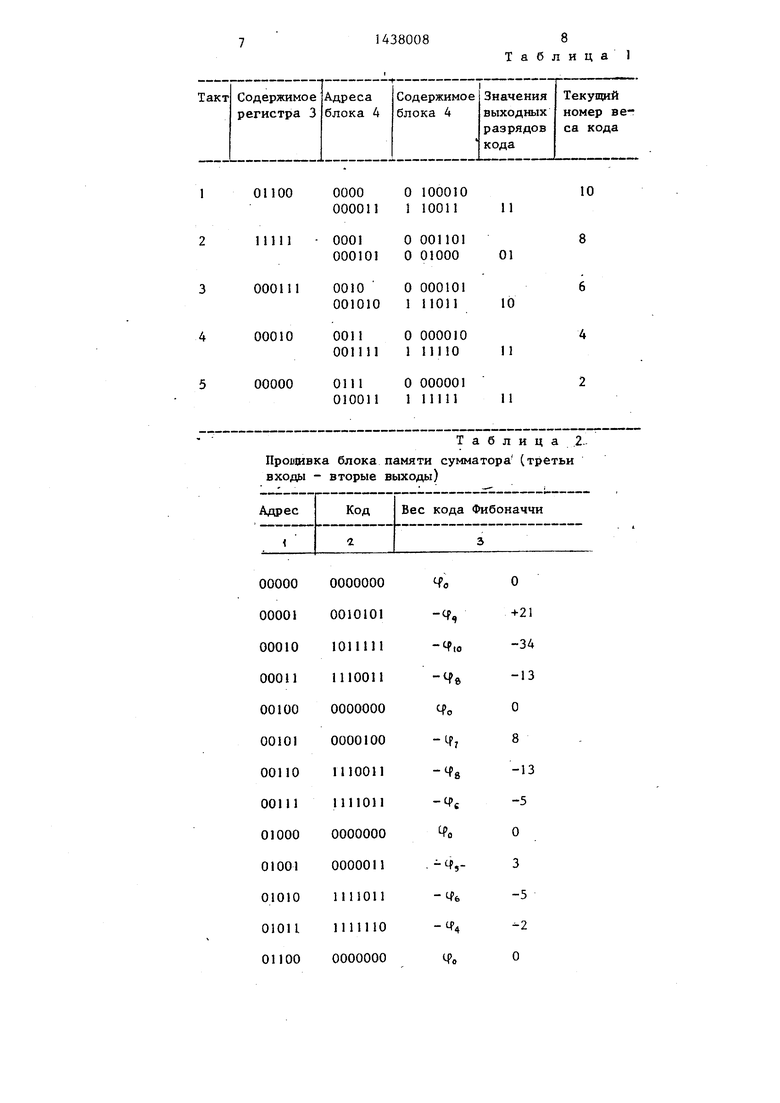

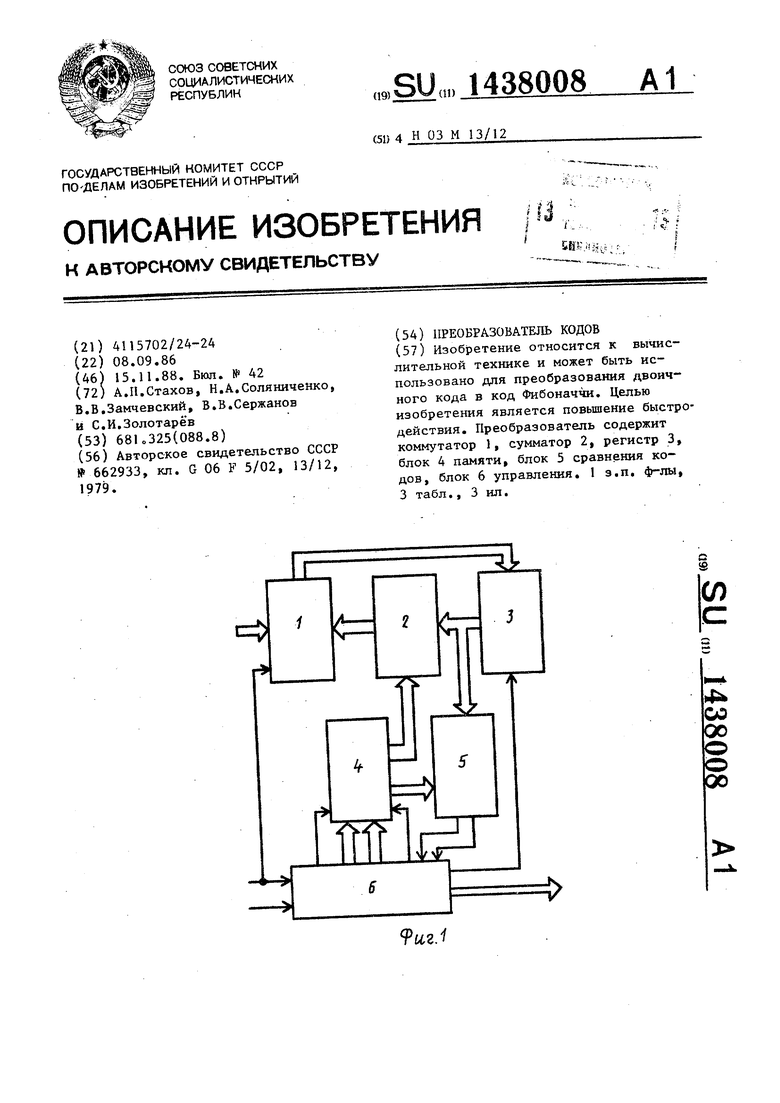

На фиг,, 1 приведена фyнкu Joнaпьнaя схема преобразователя кодов; на фиг.2 - функциональная схема блока управленияJ на фиг.З - временные диаграммы работы преобразователя кодов.

Преобразователь кодов содержит коммутатор I,, сумматор 2 регистр 3, блок 4 памяти, блок 5 сравнения кодов и блок 6 управления,

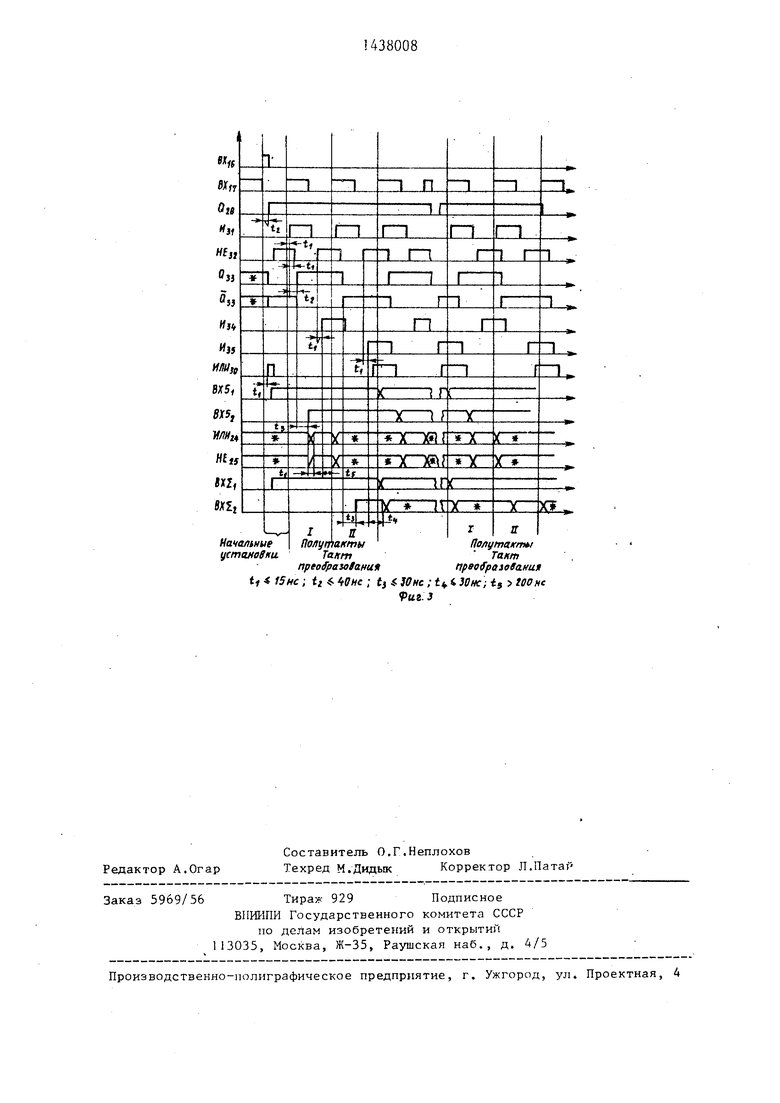

Блок 6 управления образуют элементы И.ПИ 7 и 8,, элементы НЕ 9 и 10, элементы И 11-13, регистры 14 и 5, триггеры 16 и 17 и счетчик 18„

Преобразователь кодов работает следующим образом.

На второй вход блока 6 управления поступает тактовая частота. После TorOj как на входную шину преобразователя подается преобразуемый двоичный -код, на первый вход блока 6 управления поступает команда Начаао преобразования. По этой команде регистры 14 и 15 и счетчик 18 обнуляются, триггер 16 устанавливается в состояние едини1;ы, а триггер 17 - в состояние нуля, коммутатора 1 подключает информагудонные входы регистра 3 к входной шине и по сигналу в поступаю 1Дему на управляющий вход регистра 3 с выхода злемента ИЛИ 83 происходит запись информации в регистр 3, после чего с выхода регистра 3 информа- подается на второй вход блока 5 сравнения кодов

Счетчик 18 формирует адрес эквивалента веса кода Фибоначчи, которьш необходимо подать на первые входы блока 5 сравнения кодов с блока 4 памяти,

В начальный момент преобразования содержимое счетчика 18 равно нулЮэ что указаывает на нулевой адресj по которому записан эквивалент старшего веса кода Фибоначчи Значение адреса со счетчика 18 по.ступает на третьи входы блока 4 памяти.

Триггер 17 делит тактовую частоту пополам. По приходу первого тактовог импульса он устанавливается в состояние единихщ. С прямого выхода триггера 17- на первый вход блока 4 памяти

-

iO

15

380082

поступает импульс Разрешение с-шты- вания. По приходу этого импульса на вторых выходах блока 4 памяти появляется двоичный эквивалент веса кода Фибоначчи

При помощи блока 5 сравнения кодов производится сравнение кодов, посту- паюищх с выходов регистра 3 и блока 4 памяти На первом выходе блока 5 сравнения кодов появляется единицаj если содержимое регистра 3 больше, чем вес кода Фибоначчи, в противном случае на этом присутствует нуль. На втором выходе блока 5 сравнения кодов появляется единица в том случае, если содержимое регистра 3 больше нуля. Эти сигналы поступают на третий и четвертый входы блока 6 управления. При помощи элементов ИЛИ 7 и НЕ 9 формируются два разряда выходного кода, которые по переднему фронту импульса 3 формируемого элементом И 12, записываются в регистры 14 и 15, и производится сдвиг на один разряд причем в регистр 14 производится запись четных разрядов ко- да, а в регистр 15 - нечетных.

После этого будет полностью сформирован второй адрес для блока 4 памяти. Этот адрес состоит из двух частей, Первую часть (два младших разряда адреса) составляют последние два раз- ряда выходного кода которые снимаются ,с выходов регистров 14 и 15, причем разряд, снимаег-ьш с выхода ре20

25

30

35

0

5

0

5

гистра 14, определяет разряд адреса с весом два9. а разряд, скимае 1ый с выхода регистра 15., определяет разряд адреса с весом один. Вторую . часть (оставшееся разряды адреса) составляет адрес, сформированный счетчиком 18„

По приходу второго тактового-импульса триггер 17 изменяет свое состояние и на второй вход блока 4 памяти поступает команда Разрешение, счи- тываь-шя, после чего на вход сумматора 2 поступает двоичный эквивалент веса кода Фибоначчи, подлежащий вычитанию Однако так как положительные веса записаны в дополнительном коде, а отрицательные - в прямом, операция вычитакия .заменяется опера- цизй сложения;

По сигналу, поступающему на управ- аяю.ш;ий вход регистра 3, результат сложения через коммутатор 1 записывается в регистр 3 Одновременно со

держимое счетчика 18 увеличивается на единицу.

Первый такт преобразования закончен.

Все такты преобразования, кроме последнего, отличаются от описанного тем, что в них не производится обнуление регистров и не записывается информация из входной шины ( отсутствует команда Начало преобразования) .

Последний такт преобразования отличается тем, что по приходу п-го тактового импульса на выходе переноса счетчика 18 появляется импульс переноса, который устанавливает тригге 16 в нулевое состояние, что, в свою очередь, запрещает прохождение тактовых импульсов через элемент И 1I. К этому моменту выходной код полностью сформирован и записан в регистрах 14 и 15, начиная с вторых разрядов, так как после записи информации происходит сдвиг.

Таким образом, цикл преобразования закончен, выходной код находится в регистрах 14 и 15, выходы которых образуют выходную шину, причем выходы регистра 14 - четньш, а выходы регистра 15 - нечетные разряды выходного кода.

Пусть разрядность выходного кода . На вход преобразователя поступает число +12. В двоичном коде оно представляется как

Зн. 16 8 4 2 1

О 01100

По приходу команды Начало преобразования коммутатор 1 подключает входную шину к входам регистра 3 и импульсом с элемента ИЛИ 8 входная информация записьшается в регистр 3 и подается на первый вход сумматора 2 и второй вход блока 5 сравнения ко дев. Одновременно обнуляются регистры 14 и 15 и счетчик 18, а триггер ;16 устанавливается в состояние единицы.

На третьи входы блока 4 памяти по ступает нулевой адрес, по которому записан двоичный эквивалент десятого

ТО 9 34 -21 1 1

87654321 12 -8 5 -3 2 -1 10 О 1 10 11 11,

что соответствует максимальной форме числа +12 в коде Фибоначчи, причем

0

0

5

веса кода Фибоначчи. При переходе в единичное состояние триггера 17 на первый вход блока 4 памяти поступает команда Разрешение считывания, после чего на первые,входа блока 5 сравнения кодов поступает информация из блока 4 памяти. Таким образом, блок 5 анализирует два кода: с выхода регистра 3 - О 01100 и с вторых выходов блока 4 памяти - О 100010. В дан ном случае преобразуемая величина : меньше веса кода Фибоначчи и больше нуля..Поэтому на третий и четвертый 5 входы блока 6 поступают соответственно 1 и 1 . В результате этого элементы ИЛИ 7 и НЕ 9 формируют два разряда выходного кода 1 1, которые по переднему фронту импульса с элемента К 12 записьшаются соответственно в регистры 14 и 15, и происходит сдвиг информации в этих регистрах.

Теперь полностью сформирован адрес для блока 4 памяти, поступающий на его четвертые входы. Адрес будет равен 000011. Первые четыре старших би- , та - это адрес, сформированный счетчиком 18, а последние два бита - последние биты выходного , которые снимаются с вторых разрядов выходов регистров 14 и 15. По приходу второго тактового импульса происходит сложение кода, записанного в регистре 3, и кода, поступаклцего на вторые входы сумматора 2 с блока 4 памяти.

0

5

5

0

0

0011

1100

О О

1

1

Регистр 3 Блок 4 памяти (первые выходы)

Ц 111111

По переднему фронту импульса с выхода элемента ИЛИ 8 результат операции сложения записывается в регистр 3.

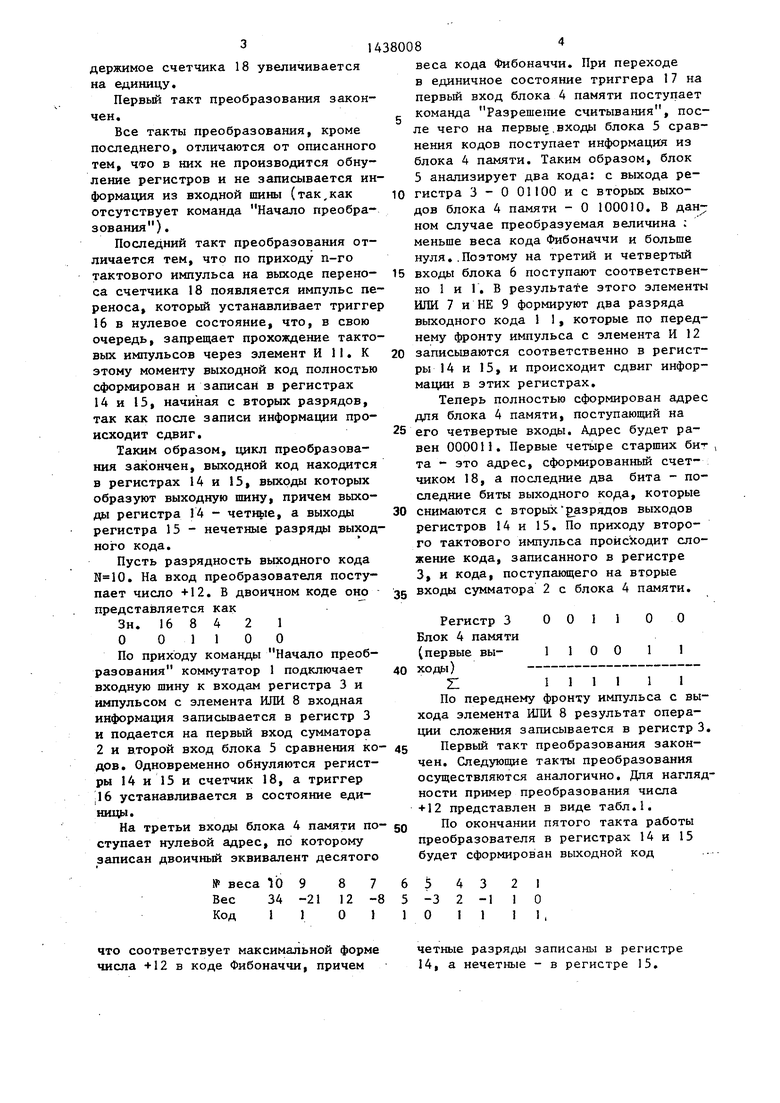

Первый такт преобразования закончен. Следующие такты преобразования осуществляются аналогично. Дпя наглядности пример преобразования числа +12 представлен в виде табл.1.

По окончании пятого такта работы преобразователя в регистрах 14 и 15 будет сформирован выходной код -

четные разряды записаны в регистре 14, а нечетные - в регистре 15.

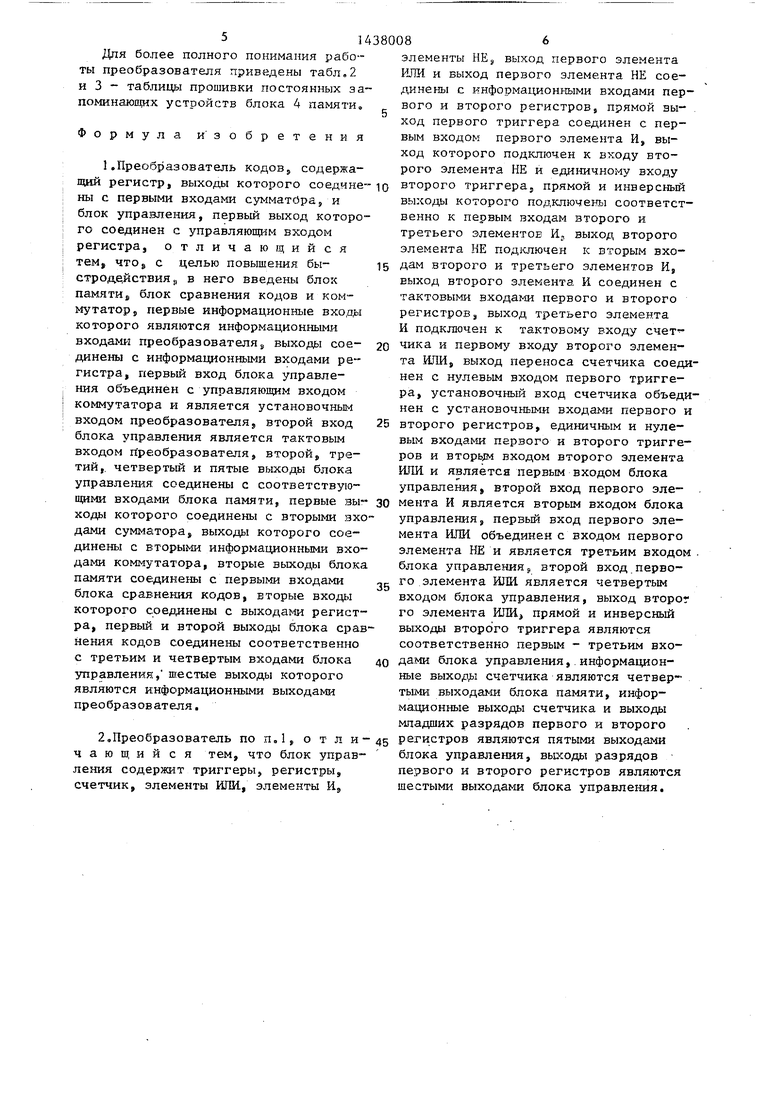

Для более полного понимания работы преобразователя приведены табл.2 и 3 - таблицы прошивки постоянных эа

поминающих устройств блока 4 памяти

Формула и зобретения

2,Преобразователь по п.1s о т л и чающийся тем, что блок управления содержит триггеры, регистры, счетчик, элементы ИЛИ, элементы И

элементы HEj выход первого элемента ИЛИ и выход первого элемента НЕ соединены с информационными входами первого и второго регистровS прямой вы- ход первого триггера соединен с первым входом первого элемента И, выход которого подключен к входу второго элемента НЕ и единичному входу второго триггера, прямой и инверсный выходы которого подключены соответственно к первым входам второго и третьего элементов И.,, выход второго элемента НЕ подключен к вторым входам второго и третьего элементов И, выход второго элемента И соединен с тактовыми входами первого и второго регистровj выход третьего элемента И. подключен к тактовому входу счет - чика и первому входу второго элемента ИЛИ, выход переноса счетчика соединен с нулевым входом первого триггера, установочный вход счетчика объединен с установочными входами первого и второго регистров, единичным и нулевым входами первого и второго триггеров и вторьдм входом второго элемента ИЛИ и являетсй первым входом блока управления, второй вход первого элемента И является вторым входом блока управления, первый вход первого элемента ИЖ объединен с входом первого элемента НЕ и является третьим входом блока управленияJ второй вход первого элемента ИЛИ является четвертым входом блока зшравления, выход второ го элемента ИЛИ прямой и инверсный выходы второго триггера являются соответственно первым - третьим входами блока управления,.информационные выходы счетчика являются четвер- тьши выходами блока памяти, инфор- махщонные выходы счетчика и выходы младших разрядов первого и второго регистров являются пятыми выходами блока управления, выходы разрядов первого и второго регистров являются шестыми выходами блока управления.

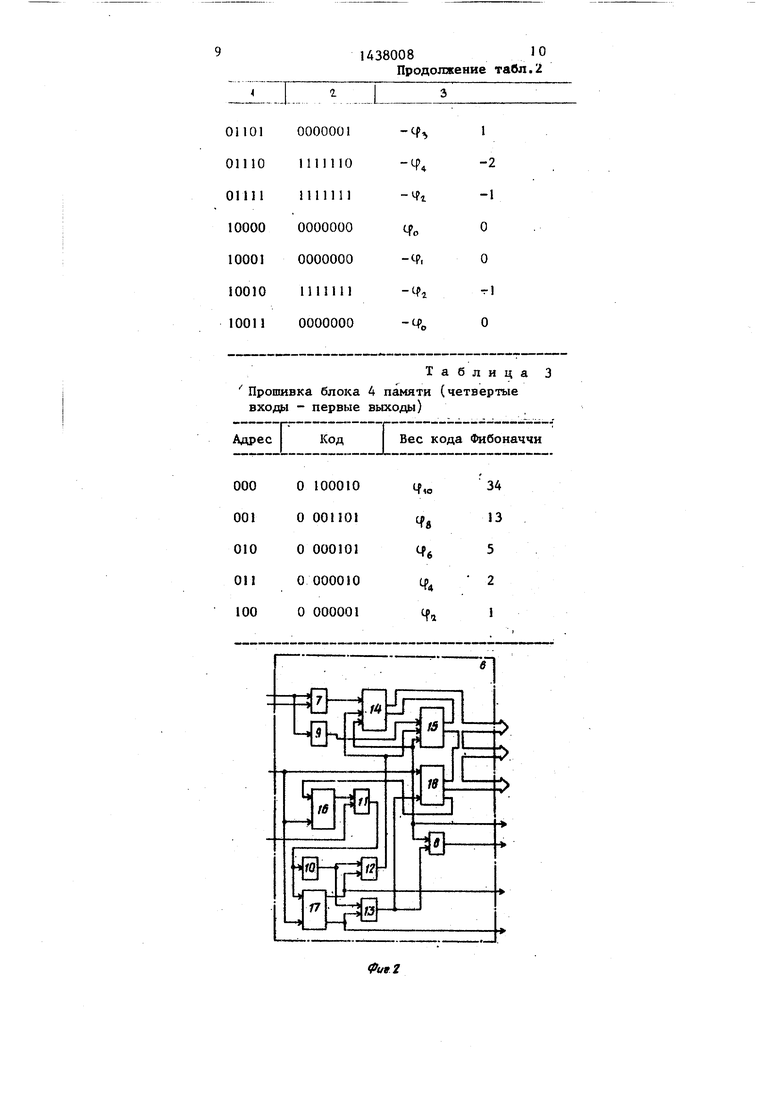

Таблица 2.

Проидавка блока памяти сумматора (третьи входы - вторые выходы)

Таблица 1

ТаблицаЗ

Прошивка блока А памяти (четвертые входы - первые выходы)

I Код I

О Ю0010 О 001101 О 000101 О 000010 О 000001

Вес кода Фибоначчи

34 13 5 2

1

nptofpauldHUHnpfofpaieffaffuf

ii 15нс; it 4ffw ; Cj 4: WHC ; t. 4 ЗОнс; if too не

Раг. 3

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-15—Публикация

1986-09-08—Подача