мащюнным входом формирователя допо.)г нительного кода, выход которого соединен с первыми входами второго сумматора и четвертого элемента И, выход которого соединен с первым вход ом блока умножения, второй вход которого соединен с выходом переключателя основания, информационный вход второго регистра сдвига соединен со своим выходом, со вторым входом второго,сумматора и первым входом пятого элемента И, выход которого через первый элемент задержки соединен с вторым входом первого сумматора, прямой выход первого триггера соединен с вторым входом элемента ИЛИ, которого соединен с входом управления формирователя дополнительного кода, выход третьего .сумматора соединен с информационным входом третьего регистра сдвига, входы ввода данных которого соединены с выходами переключателя диапазона прямой выход второго триггера соедине с входом управления коммутатора, выход которого соединен с вторым вхо дом третьего сумматора, выход третьего регистра сдвига -соединен с первым входом шестого элемента И с первым информационным входом коммутатора, второй информат- ионный вход которого соединен через второй элемент заде.ржки с выходом шестого элемента И, второй вход которого соединен с инверсным выходом первото триггера, вход сброса формирователя дополнительного кода соединен с вторыми входами первого и второго элементов И и вькодом элемента задержки блока управления, вход запуска генератора одиночных импульсов которого соединен с входом Пуск преобразователя первый вход элемента ИЛИ соединен с вькодом первого разряда распределителя блока управления, входы управления занесением информации первого, второго и третьего сдвиговых регистров соединен с выходом генератора одиночных импульсов блока управления выход второго элемента И которого содинен -с входами управления сдвигом первого и второго регистров сдвига, вход управления сдвигом третьего регистра сдвига соединен с выходом третьего элемента И блока управления, выход второго разряда распределителя которого соединен с вторыми входами четвертого и пятого элементов И, нулевые входы первого и второго триггеров соединены с импульсным выходом третьего разряда распределителя блока управления, входы ввода данных первого и второго регистров сдвига являются первым и вторым информационными входами преобразователя, выходом которого является данных третьего сдвигового реiHCTpa.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

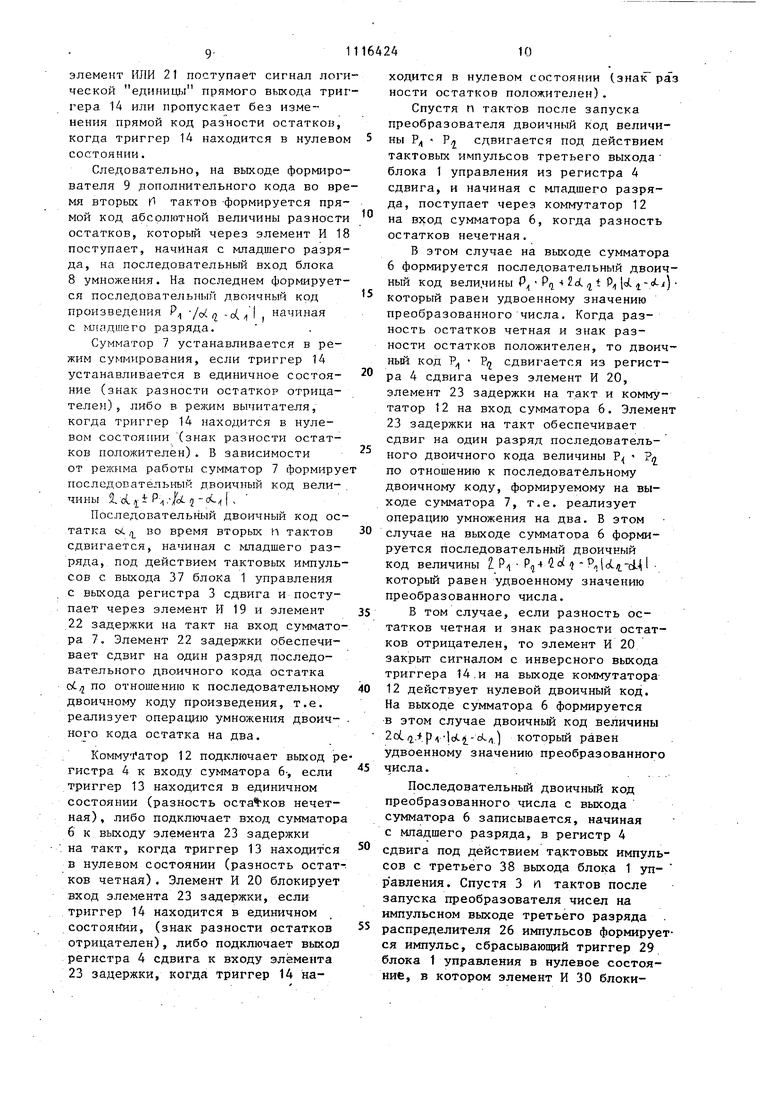

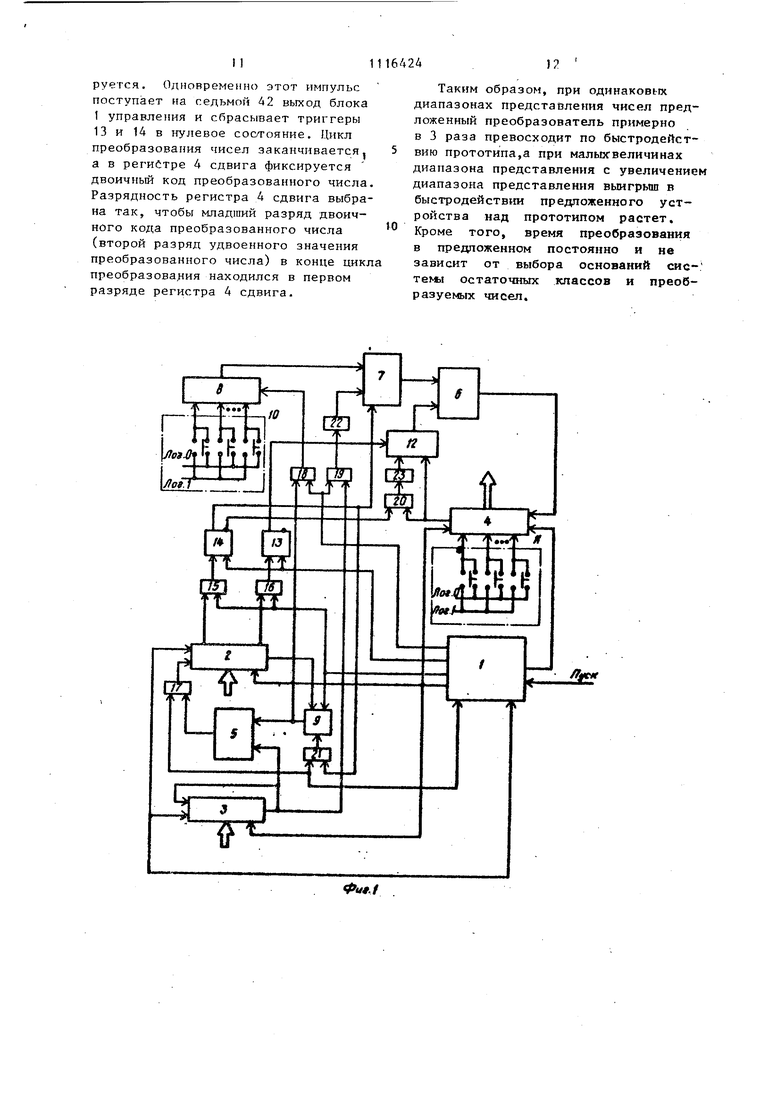

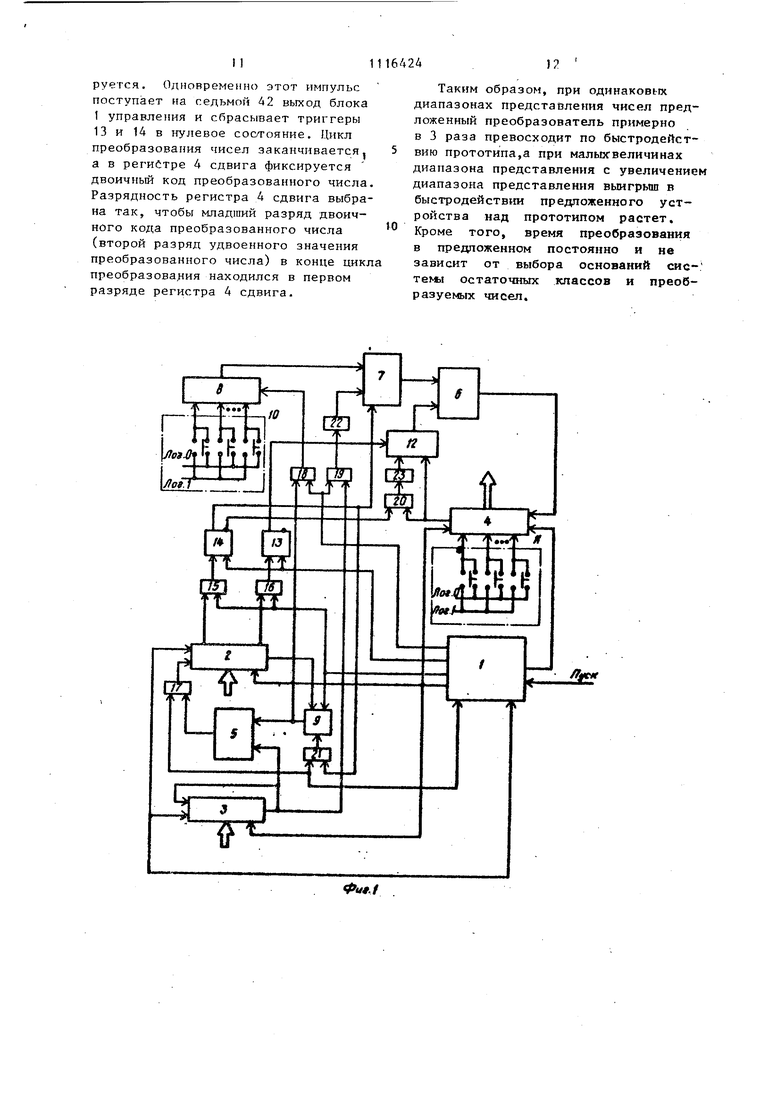

ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕ, Ш ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД, содержащий блок управления, первый сумматор, первый триггер, два элемента И, элемент Ш1И, причем прямой выход первого триггера соединен с управляющим входом сумматора, блок управления содержит генератор тактовых импульсов, триггер и элемент И, причем выход генератора тактовых импульсов соединен с первым входом элемента И, второй вход которого соединен с прямым выходом триггера, отличающийся тем, что, с целью повышения быстродействия, преобразователь содержит три регистра сдвига, блок умножения, два сумматора, формирователь дополнительного кода, переключатель основания, переключатель диапазона, коммутатор, четьфе элемента И, два элемента задержки, второй триггер, блок управления содержит делитель частоты, распределитель, генератор одиночных импульсов, второй и третий элементы И, первый и второй элементы ИЛИ, элемент задержки,, причем вь1ход первого элемента И соединен с информационным входом делителя частоты и с первыми входами второго и третьего элементов И, инверснмн выход генератора тактовых импульсов соединен с тактовым входом генератора одиночных импульсов, выход которого соединен с единичным входом триггера, вторые входы второго и третьего элементов И соединены соответственно с выходами первого и второго элементов ИЛИ, выход делителя частоты соединен с входом распределителя и входом элемента задержки, первые входы первого и второго элементов ИЛИ соединены с выходом второго разряда распределителя и myльcoв, выходы первого и третьего разрядов которого соединены соответственно с вторыми входами первого и второго элементов ИЛИ, импульсный выход треjbero разряда распределителя импульсов соединен с нулевым входом триггера, причем в преобразователе единичные входы первого и второго триггеров ,соединены соответственно с выходами первого и второго элементов И, первый вход первого и первый вход второго элементов И соединены соответственнос выходами последнего и первого разрядов первого регистра сдвига, информационный вход которого соединен с выходом третьего элемента И, первый и второй выходы которого соединены соответственно с первым входом элемента ИЛИ и выходом второго сумматора, выход блока умножения соединен с первым входом первого сумматора, выход которого соединен с первым входом третьего сумматора, выход первого регистра сдвига соединен с инфор

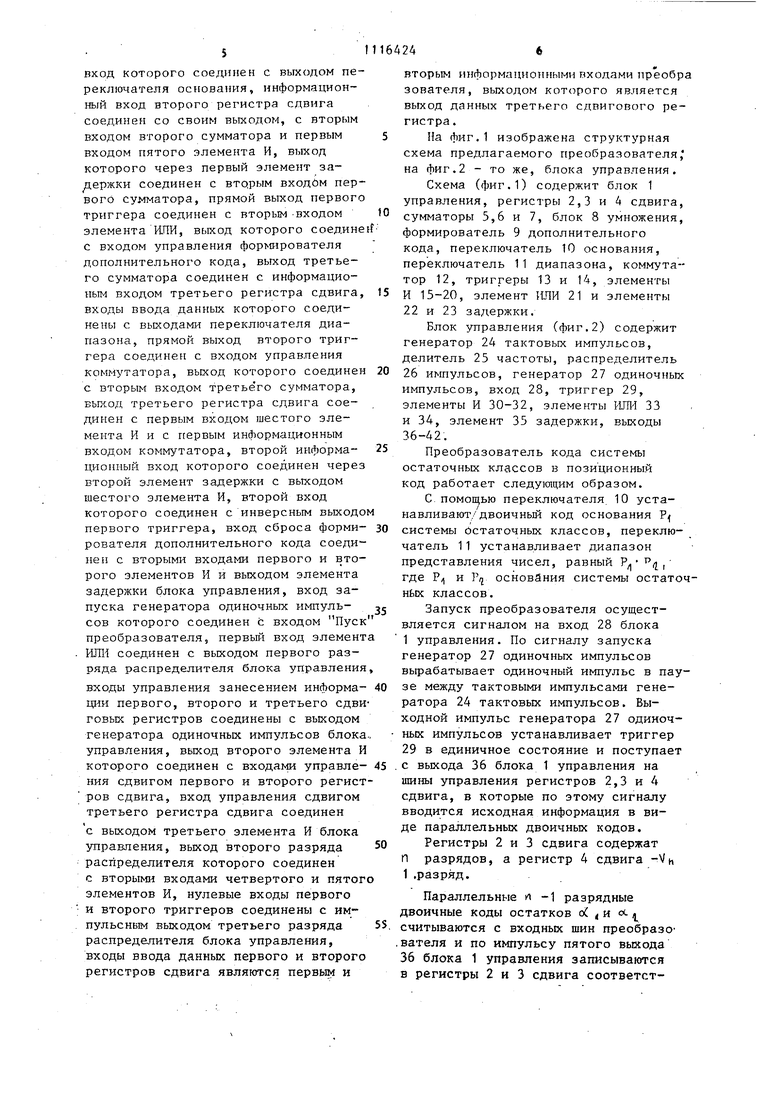

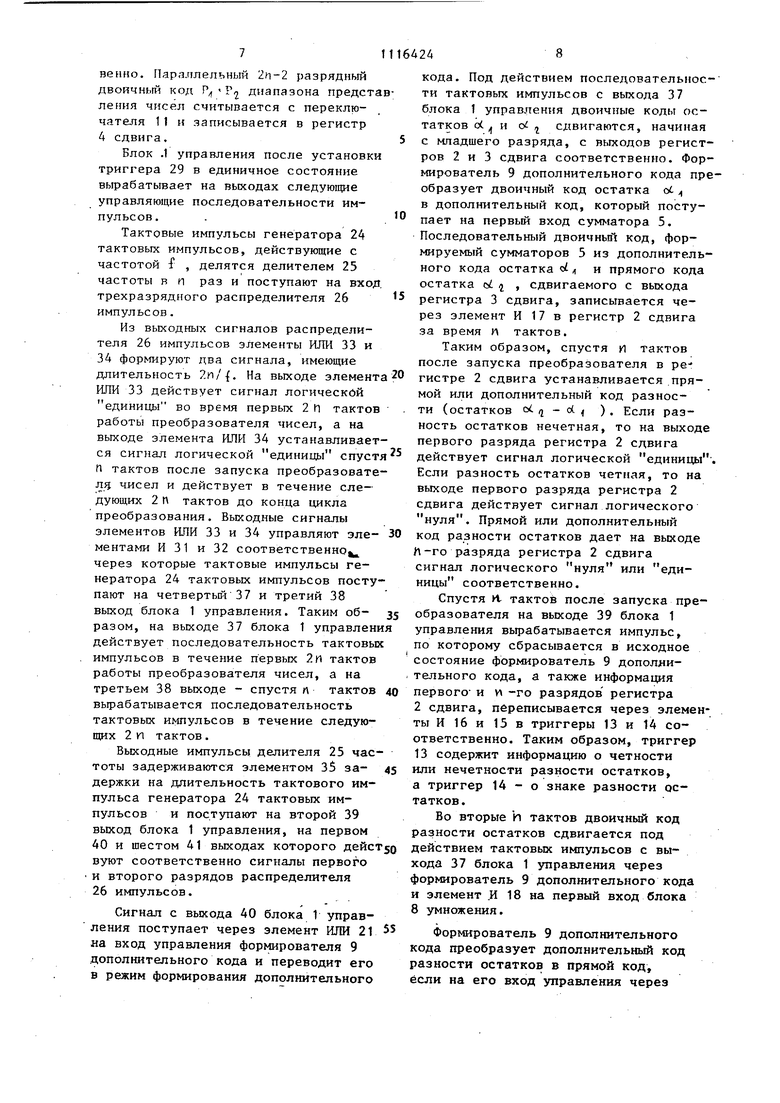

Изобретение относится к вычислительной технике, предназначено для преобразования чисел из системы остаточньк классов в позиционный код и может быть использовано в циф- 5 ровых системах автоматики и телемеханики.

Известен преобразователь чисел, содержапщй двоччный накапливающий ю счетчик, элемент сравнения, приемный регистр двоичного числа, суммирующий счетчик по модулю, элемент поразрядного сравнения, приемный регистр остатка кодового слова, J5 многовходовой элемент И, триггер

управления и переключатель режима работы til.

Недостаток известного преобразователя - низкое быстродействие.

Наиболее близким по технической сущности к изобретению является преобразователь кода системы остаточных классов в позиционный код, содержащий блок управления, сумматор, блок констант, п+1 счетчиков, триггер, два элемента И и элемент : ИЛИ, причем установочные входы первых п счетчиков являются входами преобразователя, счетные их входы подключены к первому входу элемента ИЛИ и первому выходу блока управления, второй выход которого соединен единичным входом триггера и первым входом управления сумматора, второй управляющий вход которого соединен с выходом триггера, первым входой первого элемента И и управляющим входом Сп+1)-го счетчика, установочный вход которого соединен с выходом блока констант, вход которого соединен с выходом п -го счетчи ка, выход устройства соединен с выходом сумматора, вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен со.счетным входом (h-t-l)-ro счетчика и выходом первого элемента И, второй вхо которого соединен с третьим выходом блока управления, первый и второй входы которого соединены с входом Пуск преобразователя и выходом вто рого элемента И, первый и второй вхо ды которого соединены с выходами соответствующих счетчиков, кроме того, блок управления.содержит гене ратор тактовых импульсов, триггер и элемент И, причем выход генератора тактовых импульсов соединен с третьим выходом блока управления и первым входом элемента И, второй вход которого соединен с вторым выходом блока управления и выходом триггера единичный и нулевой входы которого соединены с первым и вторым входами блока управления, первый выход которого соединен с вькодом элемента И Недостатком данного преобразователя является также низкое быстродействие . Цель изобретения - повышение быст родействия. Поставленная цель достигается тем что преобразователь кода системы остаточных классов в позиционный код содержащий блок управления, первый сумматорj первый триггер, первый и второй элементы И, элемент ИЛИ, причем прямой выход первого триггера соединен с управляющим входом сумматора, а также блок управления, содер жащий генератор тактовых импульсов, триггер и элемент И, причем выход генератора тактовых импульсов соедин с первым входом элемента И, второй вход которого соединен с прямым выходом триггера, содержит.первый, второй и третий регистры сдвига, блок умножения, два сумматора, формирователь дополнительного кода, переключатель основания, второй триггер, переключатель диапазона, коммутатор, третий, четвертьй, пятый и шестой элементы И, первый и второй элементы задержки, а блок управления содержит делитель частоты, распределитель, генератор одиночных импульсов, второй и третий элементы И, первый и второй элементы ИЛИ, элемент задержки, причем выход первого элемента И соединен с информационным входом делителя частоты и с первыми входами второго и третьего элементов И, инверсный выход генера- тора тактовых импульсов соединен с тактовым входом генератора одиночных импульсов, выход которого соединен с единичным входом триггера, вторые входы второго и третьего элементов И соединены соответственно с вь хода№1 первого и второго элементов И-ШИ, выход делителя частоты соединен с входом распределителя и входом элемента задержки, первые входы первого и второго элементов ИЛИ соединены с выходом второго разряда распределителя и тульсов, выходы первого и третьего разрядов которого соединены соответ.ственно с вторыми входами первого и второго элементов ИЛИ, импульсный выход третьего разряда распределителя импульсов соединен с нулевым входом триггера, причем в преобразователе единичные входы первого и второго триггеров соединены, соответственно с выходами первого / и второго элементов И первый вход nepBoro и первый вход второго элементов И соединены соответственно с выходами последнего и первого разрядов первого регистра сдвига, информационный вход которого соединен с выходом третьего элемента И, первый и второй входы которого соединены соответственно с первьм входом элемента ИЛИ и выходом второго сумматора, выход блока умножения соединен с первым входом первого сумматора, выход которого соединен с первым входом третьего сумматора, выход первого регистра сдвига соединен с информационным входом формирователя дополнительного кода, выход которого соединен с первыми входами второго сумматора и четвертого элемента И, выход которого соединен с первым входом блока умножения, второй вход которого соединен с выходом переключателя основания, информационный вход второго регистра сдвига соединен со своим выходом, с вторым входом второго сумматора и первым входом пятого элемента И, выход которого через первый элемент задержки соединен с вторым входим первого сумматора, прямой выход первого триггера соединен с вторым -входом элемента RHH, выход которого соедине с входом управления формирователя дополнительного кода, выход третьего сумматора соединен с информационым входом третьего регистра сдвига входы ввода данньк которого соединены с выходами переключателя диапазона, прямой выход второго триггера соединен с входом управления коммутатора, выход которого соединен с вторым входом третьего сумматора, выход третьего регистра сдвига соединен с первым входом шестого элемента И и с первым информационным входом коммутатора, второй информационный вход которого соединен через второй элемент задержки с выходом шестого элемента И, второй вход которого соединен с инверсным выходо первого триггера, вход сброса формирователя дополнительного кода соединен с вторыми входами первого и второго элементов И и выходом элемента задержки блока управления, вход запуска генератора одиночных импульсов которого соединен с входом Пуск преобразователя, первьй вход элемент ИЛИ соединен с выходом первого разряда распределителя блока управления входы управления занесением информации первого, второго и третьего сдви говых регистров соединены с выходом генератора одиночных импульсов блока управления, выход второго элемента И которого соединен с входами управления сдвигом первого и второго регист ров сдвига, вход управления сдвигом третьего регистра сдвига соединен с выходом третьего элемента И блока управления, выход второго разряда расг1ределителя которого соединен с вторыми входами четвертого и пятог элементов И, нулевые входы первого и второго триггеров соединены с импульснБм выходом третьего разряда распределителя блока управления, входы ввода данных первого и второго регистров сдвига являются первьм и вторым информационными входами прёобра зователя, выходом которого является выход данных третьего сдвигового регистра . На фиг,1 изображена структурная схема предлагаемого преобразователя, на фиг.2 - то же, блока управления. Схема (фиг.1) содержит блок 1 управления, регистры 2,3 и 4 сдвига, сумматоры 5,6 и 7, блок 8 умножения, формирователь 9 дополнительного кода, переключатель 10 основания, переключатель 11 диапазона, коммутатор 12, триггеры 13 и 14, элементы И 15-20, элемент ИЛИ 21 и элементы 22 и 23 задержки. Блок управления (фиг,2) содержит генератор 24 тактовых импульсов, делитель 25 частоты, распределитель 26 импульсов, генератор 27 одиночных импульсов, вход 28, триггер 29, элементы И 30-32, элементы ИЛИ 33 и 34, элемент 35 задержки, выходы 36-42. Преобразователь кода системы остаточных классов в позиционный код работает следующим образом. С помощью переключателя 10 устанавливают/двоичный код основания Р системы Остаточных классов, переключатель 11 устанавливает диапазон представления чисел, равный , где Р и P,j основания системы остаточнЫх классов. Запуск преобразователя осуществляется сигналом на вход 28 блока 1 управления. По сигналу запуска генератор 27 одиночных импульсов вырабатывает одиночный импульс в паузе между тактовыми импульсами генератора 24 тактовых импульсов. Выходной импульс генератора 27 одиночных импульсов устанавливает триггер 29 в единичное состояние и поступает с выхода 36 блока 1 управления на шины управления регистров 2,3 и 4 сдвига, в которые по этому сигналу вводится исходная информация в виде параллельных двоичных кодов. Регистры 2 и 3 сдвига содержат п разрядов, а регистр 4 сдвига -Ун 1 .разряд. Параллельные л -1 разрядные двоичные коды остатков о( и ос считываются с входных шин преобразо вателя и по импульсу пятого выхода 36 блока 1 управления записываются в регистры 2 и 3 сдвига соответственно. Параллельный 2п-2 разрядный двоичный код Р/ диапазона предст ления чисел считывается с переключателя 11 и записывается в регистр 4 сдвига. Блок .1 управления после установк триггера 29 в единичное состояние вырабатывает на выходах следующие управляющие последовательности импульсов. Тактовые импульсы генератора 24 тактовых импульсов, действующие с частотой f , делятся делителем 25 частоты в п раз и поступают на вхо трехразрядного распределителя 26 импульсов. Из выходных сигналов распределителя 26 импульсов элементы ИЛИ 33 и 34 формируют два сигнала, имеющие длительность .n/i(. На выходе элемен

ИЛИ 33 действует сигнал логический единицы во время первых 2 И тактов работы преобразователя чисел, а на выходе элемента ИЛИ 34 устанавливается сигнал логической единицы спустя (1 тактов после запуска преобразователд чисел и действует в течение следующих 2 П тактов до конца цикла преобразования. Выходные сигналы элементов ИЛИ 33 и 34 управляют элементами И 31 и 32 соответственно через которые тактовые импульсы генератора 24 тактовых импульсов поступают на четвертый 37 и третий 38 выход блока 1 управления. Таким образом, на выходе 37 блока 1 управлени действует последовательность тактовых импульсов в течение первых 2 И тактов работы преобразователя чисел, а на третьем 38 выходе - спустя л тактов вьфабатывается последовательность тактовых импульсов в течение следующих 2 и тактов.

Выходные импульсы делителя 25 частоты задерживаются элементом 35 задержки на длительность тактового импульса генератора 24 тактовых импульсов и поступают на второй 39 выход блока 1 управления, на первом 40 и шестом 41 выходах которого дейсТ5о

вуют соответственно сигналы первого и второго разрядов распределителя 26 импульсов.

Сигнал с вькода АО блока 1 управления поступает через элемент ИЖ 21 55 на вход управления формирователя 9 дополнительного кода и переводит его в режим формирования дополнительного

мой или дополнительный код разности (остатков /I - ( ) . Если разность остатков нечетная, то на выходе первого разряда регистра 2 сдвига действует сигнал логической единицы Если разность остатков четная, то на выходе первого разряда регистра 2 сдвига действует сигнал логического нуля. Прямой или дополнительный код разности остатков дает на выходе М-го разряда регистра 2 сдвига

нуля

сигнал логического

или еди. ницы соответственно.

Спустя И тактов после запуска пробразователя на выходе 39 блока 1 управления вьфабатывается импульс, по которому сбрасывается в исходное состояние формирователь 9 дополлительного кода, а также информация первого- и V -го разрядов регистра 2 сдвига, переписывается через элемты И 16 и 15 в триггеры 13 и 14 соответственно. Таким образом, тригге 13 содержит информацию о четности или нечетности разности остатков, а триггер 14 - о знаке разности остатков.

Во вторые И тактов двоичный код разности остатков сдвигается под

хода 37 блока 1 управления через формирователь 9 дополнительного кода и элемент .И 18 на первый вход блока В умножения.

Формирователь 9 дополнительного кода преобразует дополнительный код разности остатков в прямой код, если на его вход управления через кода. Под действием последовательноети тактовых импульсов с выхода 37 блока 1 управления двоичные коды остатков оС и сдвигаются, начиная с младшего разряда, с выходов регистров 2 и 3 сдвига соответственно. Формирователь 9 дополнительного кода преобразует двоичный код остатка оС в дополнительный код, который поступает на первый вход сум 1атора 5. Последовательный двоичньп код, формируемый сумматоров 5 из дополнительного кода остатка к и прямого кода остатка Ы . , сдвигаемого с выхода регистра 3 сдвига, записывается через элемент И 17 в регистр 2 сдвига за время тактов. Таким образом, спустя и тактов после запуска преобразователя в ре-гистре 2 сдвига устанавливается .прядействием тактовых импульсов с выэлемент ИЛИ 21 поступает сигнал логической единицы прямого выхода триггера 14 или пропускает без изменения прямой код разности остатков, когда триггер 14 находится в нулевом состоянии.

Следовательно, на выходе формирователя 9 дополнительного кода во время вторых П тактов -формируется прямой код абсолютной величины разности остатков, который через элемент И 18 поступает, начиная с младшего разряда, на последовательный вход блока 8 умножения. На последнем формируется последовательный двоичньй код произведения Р -о( I начиная с г.и(адшего разряда.

Сумматор 7 устанавливается в режим суммирования, если триггер 14 устанавливается в единичное состояние (знак разности остатков отрицателен), либо в релсим вычитателя, когда триггер 14 находится в нулевом состоянии (знак разности остатков положителен). В зависимости от режима работы сумматор 7 формируе последовательный двоичный код вели- , чины 1 сС i Р:,.-/о

Последовательный двоичный код остат1са йС во время вторых и тактов сдвигается, начиная с fflaдшeгo разряда, под действием тактовых импульсов с выхода 37 блока 1 управления с выхода регистра 3 сдвига и поступает через элемент И 19 и элемент

22задержки на такт на вход сумматора 7. Элемент 22 задержки обеспечивает сдвиг на один разряд последовательного двоичного кода остатка о6 по отношению к последовательному двоичному коду произведения, т.е. реализует операцию умножения двоичного кода остатка на два.

Коммутатор 12 подключает выход регистра 4 к входу сумматора 6-, если триггер 13 находится в единичном состоянии (разность нечетная) , либо подключает вход сумматора 6 к выходу элемента 23 задержки на такт, когда триггер 13 находится в нулевом состоянии (разность остат ков четная). Элемент И 20 блокирует вход элемента 23 задержки, если триггер 14 находится в единичном состоянии, (знак разности остатков отрицателен), либо подключает выход регистра 4 сдвига к входу элемента

23задержки, когда триггер 14 находится в нулевом состоянии (знак раз ности остатков положителен).

Спустя п тактов после запуска преобразователя двоичный код величины Р Р сдвигается под действием тактовых импульсов третьего выхода блока 1 управления из регистра 4 сдвига, и начиная с младшего разряда, поступает через коммутатор 12 на вход сумматора 6, когда разность остатков нечетная.

В этом случае на выходе сумматора 6 формируется последовательный двоичньй код вели.чины Р Pfj -t 2oL t Р Ц .-i)

который равен удвоенному значению преобразованного числа. Когда разность остатков четная и знак разности остатков положителен, то двоичHbDi код Р Р(2 сдвигается из регист-

ра 4 сдвига через элемент И 20,

элемент 23 задержки на такт и коммутатор 12 на вход сумматора 6. Элемент 23 задержки на такт обеспечивает сдвиг на один разряд последовательного двоичного кода величины Р по отношению к последовательному двоичному коду, формируемому на выходе сумматора 7, т.е. реализует операцию умножения на два. В этом

случае на выходе сумматора 6 формируется последовательный двоичный код величины 1 1.cl iL-dJi который равен удвоенному значению преобразованного числа.

В том случае, если разность остатков четная и знак разности остатков отрицателен, то элемент И 20 закрыт сигналом с инверсного выхода триггера 14,и на выходе коммутатора

12 действует нулевой двоичный код. На выходе сумматора 6 формируется в этом случае двоичньй код величины 2d. р,, который равен удвоенному значению преобразованного

числа.

Последовательный двоичный код преобразованного числа с выхода сумматора 6 записывается, начиная с младшего разряда, в регистр 4

сдвига под действием тдктовых импульсов с третьего 38 выхода блока 1 управления. Спустя 3 п тактов после запуска преобразователя чисел на импульсном выходе третьего разряда

распределителя 26 импульсов формируется импульс, сбрасывающий триггер 29 блока 1 управления в нулевое состояние, в котором элемент И 30 блокируется. Одновременно этот импульс поступает на седьмой 42 выход блока 1 управления и сбрасывает триггеры 13 и 14 в 1гулевое состояние. Цикл преобразования чисел заканчивается, а в регистре 4 сдвига фиксируется двоичный код преобразованного числа. Разрядность регистра 4 сдвига выбрана так, чтобы младший разряд двоичного кода преобразованного числа (второй разряд удвоенного значения преобразованного числа) в конце цикл преобразова,ния находился в первом разряде регистра 4 сдвига.

X

ff

.-3LJp f .,/g

rw

уД I 1

Таким образом, при одинаковых диапазонах предста зления чисел предложенный преобразователь примерно в 3 раза превосходит по быстродействию прототипа,а при мальве величинах диапазона представления с увеличение диапазона представления выигрыш в быстродействии предложенного устройства над прототипом растет. Кроме того, время преобразования в предпоженном постоянно и не зависит от выбора оснований сиетеьы остаточных классов и преобразуемых чисел.

MfNf

36 37

39 l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в двоичный код | 1976 |

|

SU574714A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU924695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-30—Публикация

1983-05-17—Подача