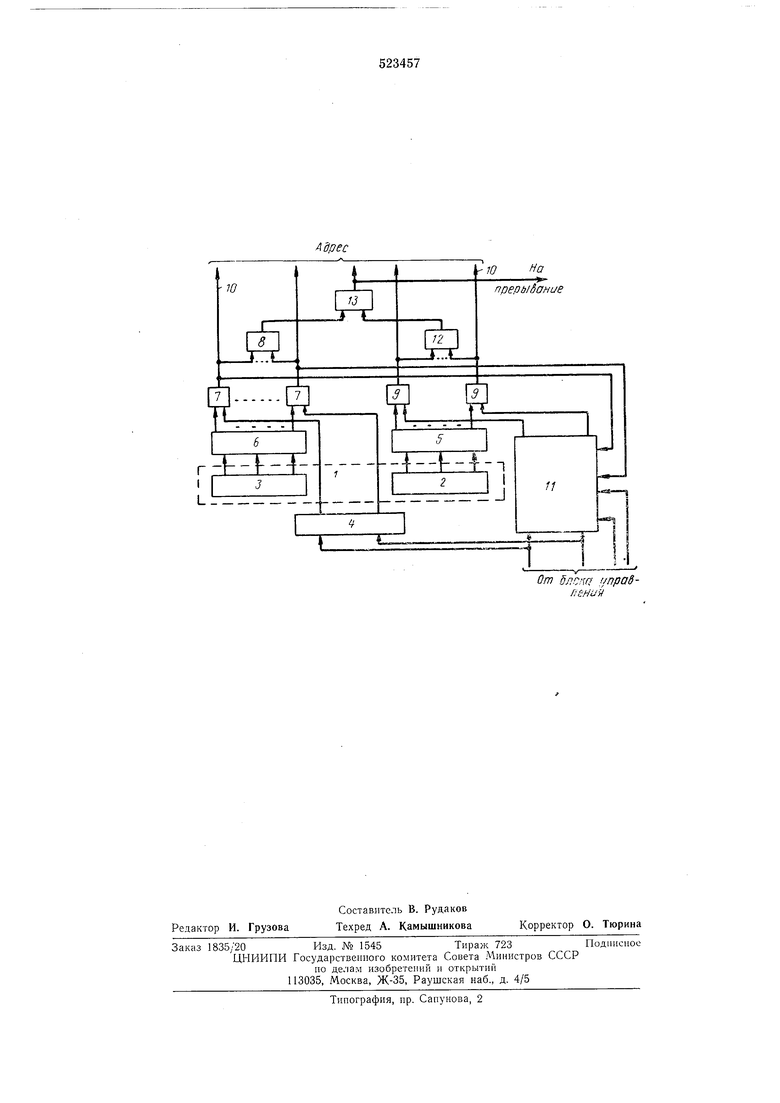

но числу страниц, основной элемент «ИЛИ 8, элементы «И 9 второй группы, число которых равно количеству строк в странице, а выхолы подключены к адресным шинам Ю

Кроме того, в устройство введены запоминающий блок 11 для хранения масок строк и дополнительные элементы «ИЛИ 12 и «И 13. Адресные входы блока 11 подсоединены к выходам элементов «И 7, а выходы - к одним входам элементов «И 9, другие входы которых через дешифратор 5 строк подключены к выходам регистра 2 адреса строк, а выходы- к одному входу элемента «И 13, другой вход которого соединен с выходом элемента «ИЛИ 8.

Работает устройство следуюш,им образом.

Перед началом работы в регистр 4 вводится код маски страниц, используемых в заданной программе, а в блок 11-коды всех строк, используемых в заданной программе.

Далее после формирования адреса в регистре 1 происходит сравнепие на элементах «И 7 информации, .поступающей из дешифратора 6 страниц и из регистра 4 маски страниц. Ири совпадении информации «а входах одного из элементов «И 7 формируется адрес страницы памяти, по которому происходит выбор также кода маски всех строк для этой страницы из блока 11. Этот код маски строк сравнивается с информацией, поступающей из дешифратора 5 строк. В случае совпадения информации на входах одного из элементов «И 9 формируется адрес строки. При наличии адреса строки и адреса страниц на выходе элемента «И 13 образуется сигнал разрешения обращения к памяти. Когда нет адреса строки или адреса страницы, на выходе элемента «И 13 появляется сигнал, запрещающий обращения к памяти, вырабатывающий сигнал на прерывание выполнения программы. При этом (как и после выполнения полностью заданной программы) регистр 2 адреса строк, регистр 3 адреса страниц, регистр 4 маски страниц и блок И устанавливаются в нулевое состояние (цепи установки на чертеже не показаны).

Предложенное устройство может быть использовано для адресации с защитой большого объема памяти. При этом необходимо в него дополнительно ввести регистр адреса блока,, дешифратор блока, регистр маски -блока, элементы «И и «ИЛИ со связями, аналогичными описанным (но без подключения к блоку И).

Введение в устройство для защиты памяти

блока 11, элементов «И 13 и «ИЛИ 12 позволяет записывать выполняемые программы (имеющие разную длину) в произвольные участки памяти. Это приводит к экономичному использованию дорогостоящей памяти ЦВМ. Так,

например, для реализации двадцати программ в предложенном устройстве необходимо формировать в 1,5 раза меньше адресов (строк) и соответственно иметь в 1,5 раза меньше объем .памяти ЦВМ по сравнению с известным

устройством 3.

Формула изобретения

Устройство для защиты памяти, содержащее регистр адреса страниц, подключенный к дещифратору страниц, рагистр маски страниц, выходы которого соединены с одними входами элементов «И первой группы, другие входы которых 1под1ключвны К выходам дешифратора страниц, а выходы-к входам «оновного элеманта «ИЛИ, элементы «И второй группы, дешифратор строк и регистр адреса строк, отличающееся тем, что, с целью

повышения надежности устройства-, оно содержит дополнительные элементы «И и «ИЛИ и запоминающий блок, адреоныевходыкоторого подключены к выходам элементов «И первой группы, а выходы - к одним входам элементов «И второй группы, другие входы которых через дешифратор строк подключены к выходам регистра адреса строк, а выходы через дополнительный элемент к одному входу дополнительного элемента «И,

другой вход которого соединен с выходом основного элемента «ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1.Патент США №3264615, кл. 340-172. 5, 1966.

2.Авт. св. № 230519, М., кл. G 06 F 11/00, 1967.

3. Дроздов Е. А. и др. Многопрограммные ЦВМ, Воен. издат., М., 1974, стр. 324-326.

10 На

От 1/прабпения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1305681A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для защиты памяти | 1980 |

|

SU918974A1 |

| Устройство для фиксации трассы выполнения программы | 1983 |

|

SU1136170A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство для динамического преобразования адреса | 1985 |

|

SU1265771A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1785039A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

Авторы

Даты

1976-07-30—Публикация

1975-05-26—Подача