соответствии с их весами, при этом старшим является Ар.

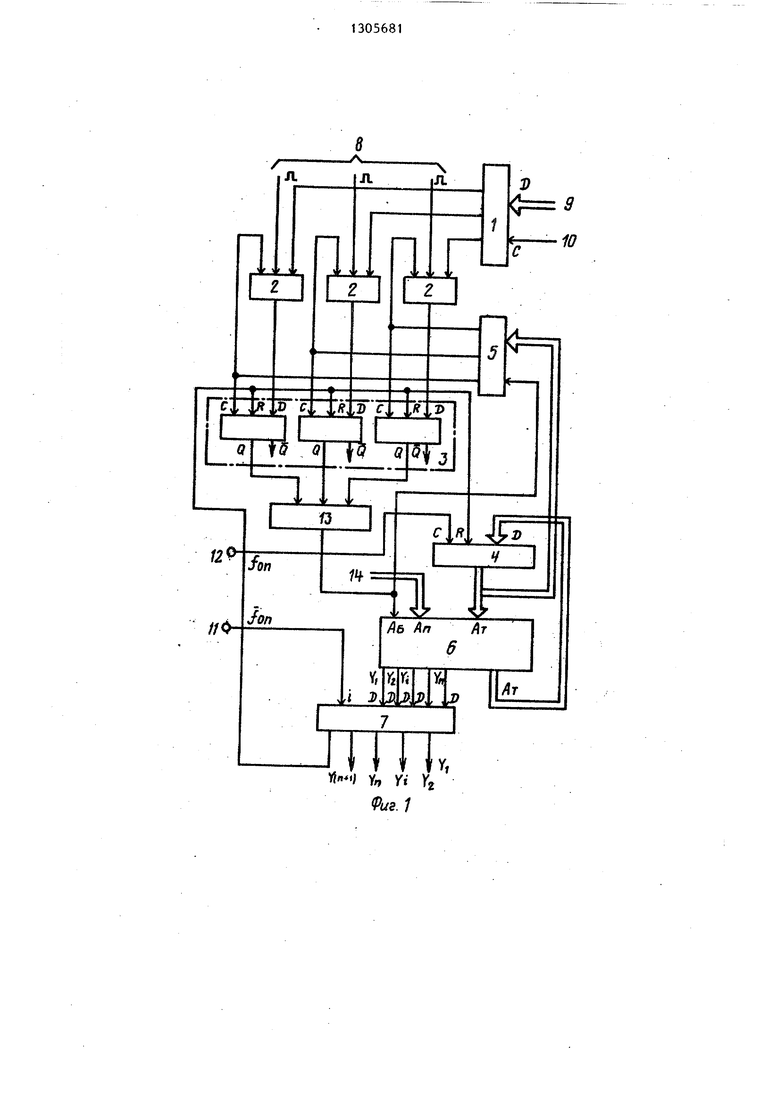

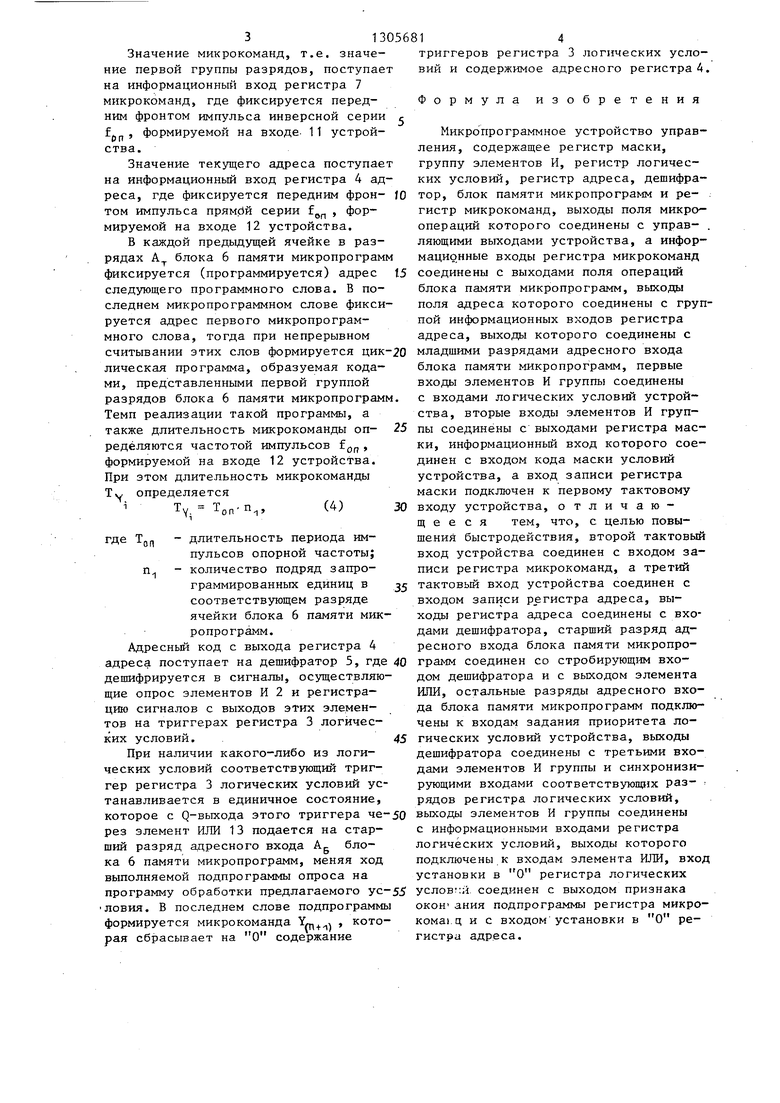

Базовый адресный код Л (фиг. 3)

тельной технике и может быть использовано в цифровых вычислительных машинах.

Цель изобретения - повьшение быст- г представляет собой однобитовый сиг- родействия.

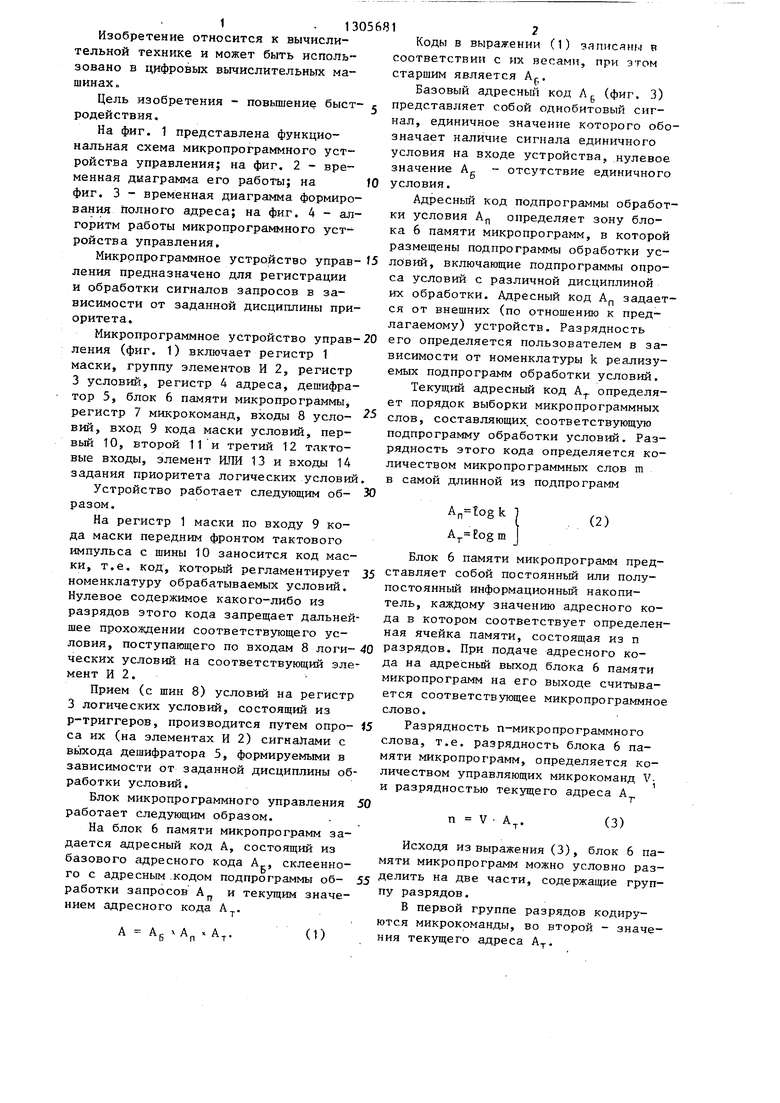

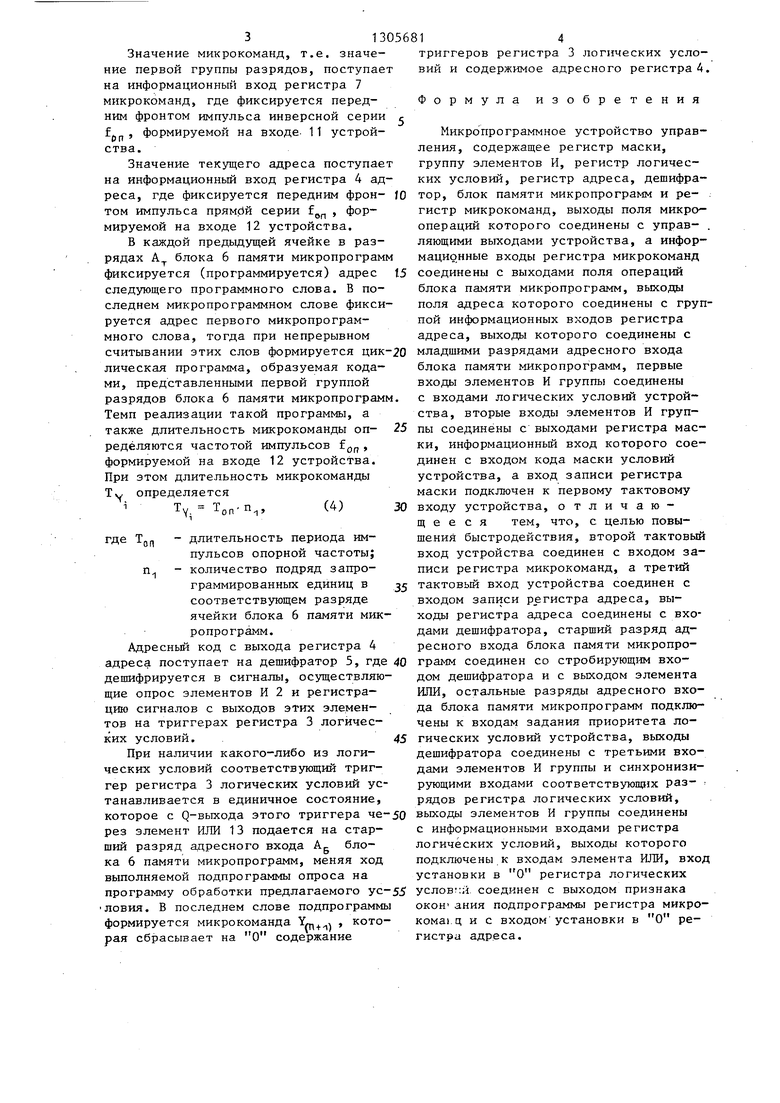

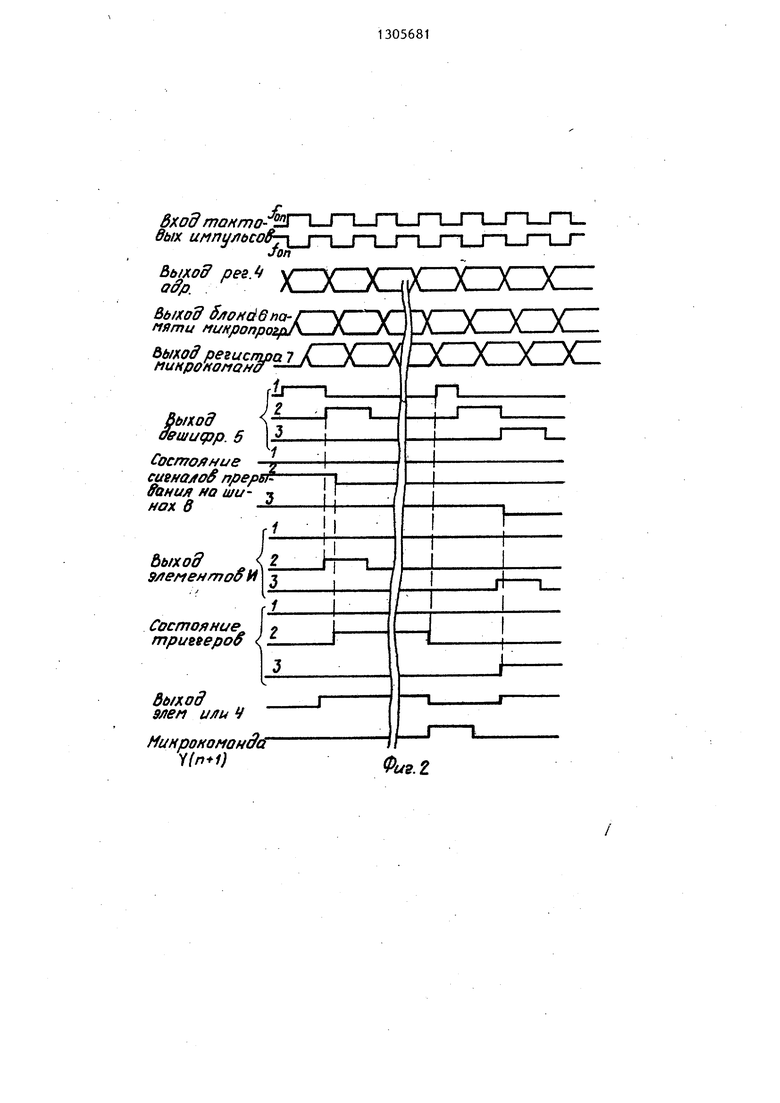

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 - временная диаграмма его работы; на 10 фиг. 3 - временная диаграмма формирования полного адреса; на фиг. 4 - алгоритм работы микропрограммного устройства управления.

Микропрограммное устройство управ- 5 ловий, включающие подпрограммы опро- ления предназначено для регистрации са условий с различной дисциплиной и обработки сигналов запросов в за- их обработки. Адресный код А, задает- висимостй от заданной дисциплины при- ся от внешних (по отношению к пред- оритета.лагаемому) устройств. Разрядность

Микропрограммное устройство управ-20 его определяется пользователем в занал, единичное значение которого обозначает наличие сигнала единичного условия на входе устройства, нулевое значение Ag - отсутствие единичного условия.

Адресный код подпрограммы обработки условия Ар определяет зону блока 6 памяти микропрограмм, в которой размещены подпрограммы обработки усления (фиг. 1) включает регистр 1 маски, группу элементов И 2, регистр

Текущий адресный код А определяет порядок выборки микропрограммных

рядность этого кода определяется количеством микропрограммных слов m в самой длинной из подпрограмм

(2)

3 условий, регистр 4 адреса, дешифратор 5, блок 6 памяти микропрограммы,

регистр 7 микрокоманд, входы 8 уело- - слов, составляющих, соответствующую ВИЙ, вход 9 кода маски условий, пер- подпрограмму обработки условий. Раз- вьй 10, второй 11 и третий 12 тактовые входы, элемент ИЛИ 13 и входы 14 задания приоритета логических условий.

Устройство работает следующим об- 30 разом.

На регистр 1 маски по входу 9 кода маски передним фронтом тактового импульса с шины 10 заносится код маски, т.е. код, который регламентирует 35 ставляет собой постоянный или полуноменклатуру обрабатываемых условий. постоянный информационный накопи- Нулевое содержимое какого-либо из разрядов этого кода запрещает дальнейшее прохождении соответствующего условия, поступающего по входам 8 логи- 40 разрядов. При подаче адресного ко- ческих условий на соответствующий эле- Д адресный выход блока 6 памяти мент И 2.

Прием (с шин 8) условий на регистр 3 логических условий, состоящий из р-триггеров, производится путем опро- 45

1 J Блок 6 памяти микропрограмм предтель, каждому значению адресного кода в котором соответствует определенная ячейка памяти, состоящая из п

микропрограмм на его выходе считывается соответствующее микропрограммное слово.

Разрядность п-микропрограммного

са их (на элементах И 2) сигналами с выхода дешифратора 5, формируемыми в зависимости от заданной дисциплины обработки условий.

Блок микропрограммного управления 50 работает следующим образом.

На блок 6 памяти микропрограмм задается адресный код А, состоящий из

склееннослова, т.е. разрядность блока 6 памяти микропрограмм, определяется количеством управляющих микрокоманд V- и разрядностью текущего адреса А

V А

т

(3)

Исходя из выражения (3), блок 6 памяти микропрограмм можно условно разбазового адресного кода А.,

го с адресным .кодом подпрограммы об- 55 Делить на две части, содержащие групработки запросов А и текущим значением адресного кода А

т

АБ А,

А

т

(1)

соответствии с их весами, при этом старшим является Ар.

Базовый адресный код Л (фиг. 3)

представляет собой однобитовый сиг-

представляет собой однобитовый сиг-

нал, единичное значение которого обозначает наличие сигнала единичного условия на входе устройства, нулевое значение Ag - отсутствие единичного условия.

Адресный код подпрограммы обработки условия Ар определяет зону блока 6 памяти микропрограмм, в которой размещены подпрограммы обработки усвисимости от номенклатуры k реализуемых подпрограмм обработки условий.

Текущий адресный код А определяет порядок выборки микропрограммных

рядность этого кода определяется количеством микропрограммных слов m в самой длинной из подпрограмм

слов, составляющих, соответствующую подпрограмму обработки условий. Раз-

(2)

вляет собой постоянный или полутоянный информационный накопи- рядов. При подаче адресного ко- адресный выход блока 6 памяти

1 J Блок 6 памяти микропрограмм представляет собой постоянный или полупостоянный информационный накопи- разрядов. При подаче адресного ко- Д адресный выход блока 6 памяти

тель, каждому значению адресного кода в котором соответствует определенная ячейка памяти, состоящая из п

ставляет собой постоянный или полупостоянный информационный накопи- разрядов. При подаче адресного ко- Д адресный выход блока 6 памяти

микропрограмм на его выходе считывается соответствующее микропрограммное слово.

Разрядность п-микропрограммного

слова, т.е. разрядность блока 6 памяти микропрограмм, определяется количеством управляющих микрокоманд V- и разрядностью текущего адреса А

V А

т

(3)

Исходя из выражения (3), блок 6 памяти микропрограмм можно условно разпу разрядов.

В первой группе разрядов кодируются микрокоманды, во второй - значения текущего адреса А.

Значение микрокоманд, т.е. значение первой группы разрядов, поступает на информационный вход регистра 7 микрокоманд, где фиксируется передним фронтом импульса инверсной серии fpj, , формируемой на входе- 11 устройства.

Значение текущего адреса поступает на информационный вход регистра 4 адреса, где фиксируется передним фрон- том импульса прямбй серии f , формируемой на входе 12 устройства.

В каждой предыдущей ячейке в разрядах А блока 6 памяти микропрограмм фиксируется (программируется) адрес следующего программного слова. В последнем микропрограммном слове фиксируется адрес первого микропрограммного слова, тогда при непрерывном считывании этих слов формируется циклическая программа, образуемая кодами, представленными первой группой разрядов блока 6 памяти микропрограмм Темп реализации такой программы, а также длительность микрокоманды оп- редёляются частотой импульсов f, формируемой на входе 12 устройства. При этом длительность микрокоманды

Ч. 1

определяется

Ту. Топ- п.

(4)

где Т,

оп

- длительность периода импульсов опорной частоты; п - количество подряд запрограммированных единиц в соответствующем разряде ячейки блока 6 памяти микропрограмм.

Адресньм код с выхода регистра 4 адреса поступает на дешифратор 5, где дешифрируется в сигналы, осуществляющие опрос элементов И 2 и регистрацию сигналов с выходов этих элементов на триггерах регистра 3 логических условий.

При наличии какого-либо из логических условий соответствующий триггер регистра 3 логических условий устанавливается в единичное состояние, которое с Q-выхода этого триггера через элемент ИЛИ 13 подается на старший разряд адресного входа А блока 6 памяти микропрограмм, меняя ход выполняемой подпрограммы опроса на программу обработки предлагаемого ус- ловия. В последнем слове подпрограммы формируется микрокоманда Y, , которая сбрасывает на О содержание

с

5 0 5

0

0 5

0 5

триггеров регистра 3 логических условий и содержимое адресного регистра 4.

Формула изобретения

Микропрограммное устройство управления, содержащее регистр маски, группу элементов И, регистр логических условий, регистр адреса, дешифратор, блок памяти микропрограмм и ре- . гистр микрокоманд, выходы поля микроопераций которого соединены с управ- . ляющими выходами устройства, а информационные входы регистра микрокоманд соединены с выходами поля операций блока памяти микропрограмм, выходы поля адреса которого соединены с группой информационных входов регистра адреса, выходы которого соединены с младшими разрядами адресного входа блока памяти микропрограмм, первые входы элементов И группь соединены с входами логических условий устройства, вторые входы элементов И группы соединены с выходами регистра маски, информационный вход которого соединен с входом кода маски условий устройства, а вход записи регистра маски подключен к первому тактовому входу устройства, отличающееся тем, что, с целью повышения быстродействия, второй тактовый вход устройства соединен с входом записи регистра микрокоманд, а третий тактовый вход устройства соединен с входом записи регистра адреса, выходы регистра адреса соединены с входами дешифратора, старший разряд адресного входа блока памяти микропрограмм соединен со стробирующим входом дешифратора и с выходом элемента ИЛИ, остальные разряды адресного входа блока памяти микропрограмм подключены к входам задания приоритета логических условий устройства, вькоды дешифратора соединены с третьими входами элементов И группы и синхронизирующими входами соответствующих раз- рядов регистра логических условий, выходы элементов И группы соединены с информационными входами регистра логических условий, выходы которого подключены к входам элемента ИЛИ, вход установки в О регистра логических услов;;й соединен с выходом признака ОКОН ания подпрограммы регистра микрокома ц и с входом установки в О регистра адреса.

л

1 f

UJ

Я,1

сГТ

2)

li Q Q

f3

f2

/ОЛ

I I I I Vt

у„ /f Уг

ws. /

Л

л

g t

3 -iff

LO

2) С

s

fj

;JE

ff

ia

Аб An Ar 6

V,

n/IT

BbiKoff рег. offp.

Выход $/toHd6hQ- Пит и fiUKponpo2f i

йынод регистра

nUHpO Of1QMff rii

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1277107A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Микропрограммное устройство для обработки прерываний | 1984 |

|

SU1188739A2 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении ЦВМ. Цель изобретения - повышение быстродействия. Устройство содержит регистр 1 маски, группу элементов И 2, регистр 3 условий, регистр 4 адреса, дешифратор 5, блок 6 памяти микропрограмм, регистр 7 микрокоманд, входы 8 условий, вход 9 кода маски условий, элемент ИЛИ 13. За счет уменьшения времени реакции устройства на логические условия достигнута цель изобретения. 4 ил. со ел Oi сх

Ул

Выход рег:ис/пра адреса

Выход В памйти михро- проер.

Выход -у мае и с т р. 15 Л

Значение affpBCQ Aff

Значениеи, .;.

адреса I/wWOT

Ллпмп SnnMaTit

SAOf a$nafiflTu HUHponpazp.

Фиъ.Ъ

| Устройство для обработки прерываний | 1979 |

|

SU855665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-20—Подача