(54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Генератор ортогональных сигналов | 1982 |

|

SU1073766A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| Устройство для контроля блоков памяти | 1979 |

|

SU771733A1 |

Изобретен1.е относится к вычислительной технике и может использоваться в цифровых вычислительных устройствах, обладаюших улучшенными потсазателями надежности и быстродействия.

Известны быстродействующие устройства для сложения чисел, в которых для повышения надежности используется дублирование переносов и двойная логика 1 . Недостатком известного устройства явля- ется отсутствие контроля исходной информации.

Наиболее близким но технической сущности к данному изобретению является устройство для сложения, содержащее регистр первого числа, триггер четности, сумматор, первая группа входов которого подключена к выходам регистра первого числа, триггер переполнения, регистр второго числа, выходы которого подключены ко второй группе входов сумматора, выходы которого подключены ко входам регистра первого числа 2 Недостатком такого устройства является низкая степень надежности, обусловленная невозможностью полного контроля сборудования в течение всего времени работы устройства.

Цель изобретения - повышение надежности работы устройства.

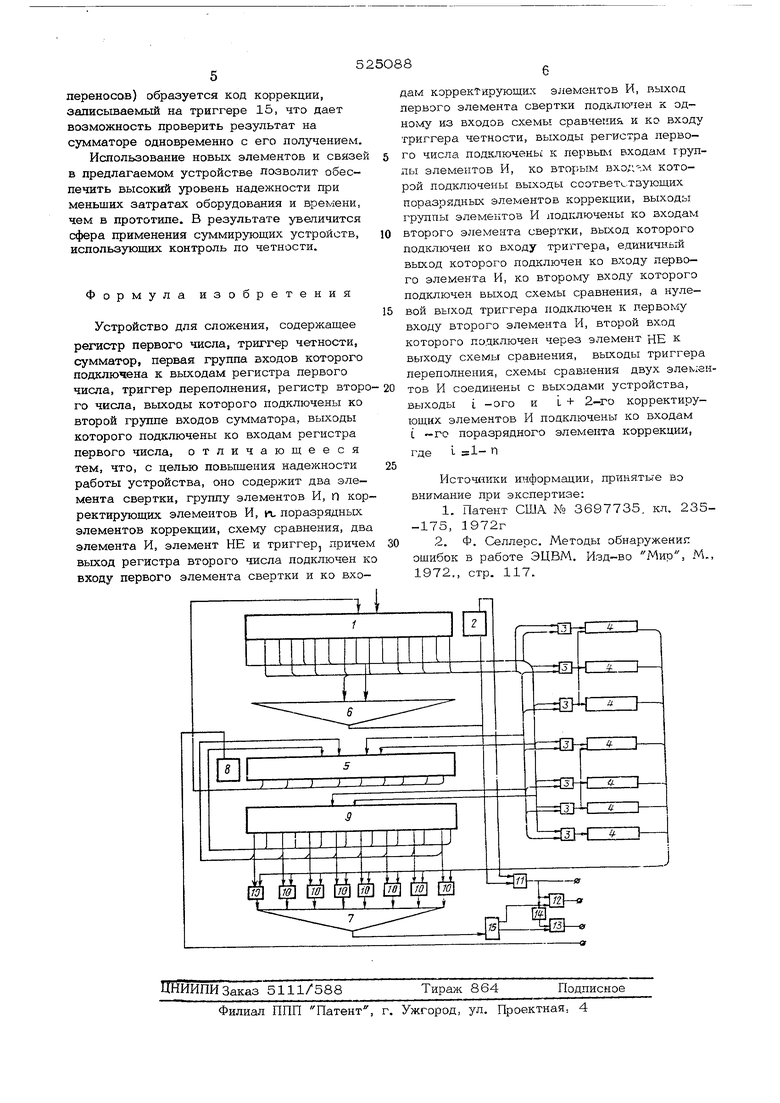

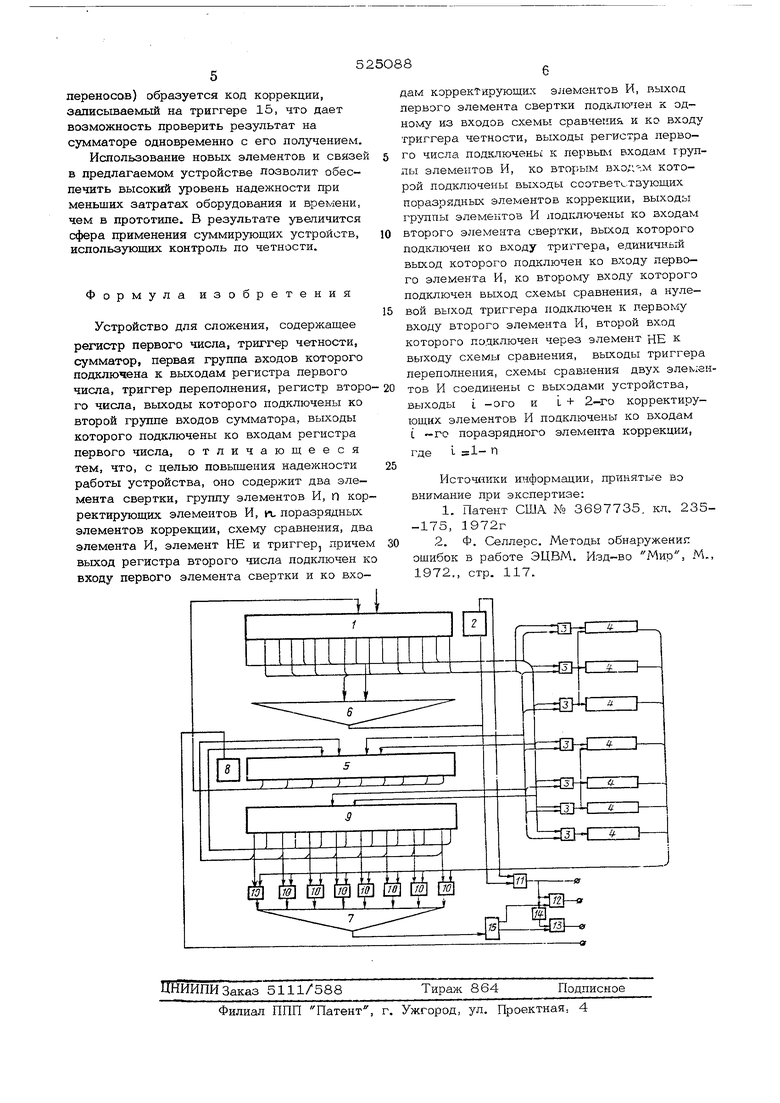

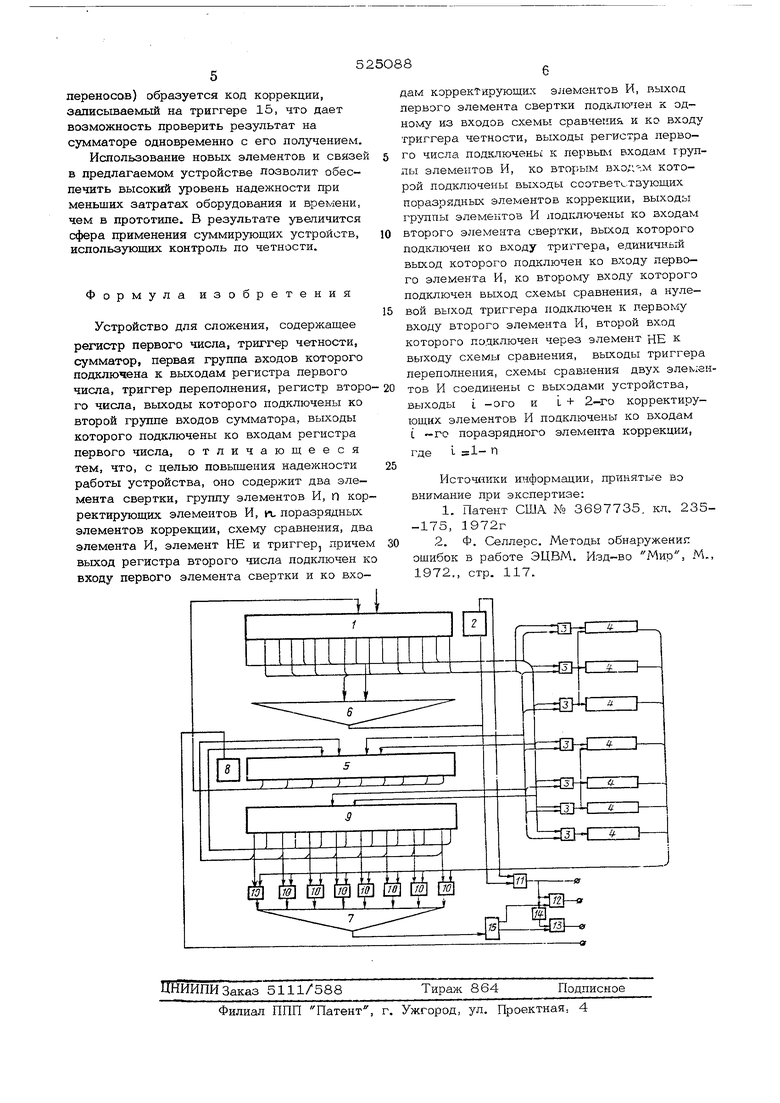

Это достигается тем, что оно содержит два элемента свертки, группу элементов И, П корректирующих элементов И, П поразрядных элементов коррекции, схему сравнения, два элемента И, элемент НЕ и триггер, причем выход регистра второго числа подключен ко входу первого элемента свертки и ко входам корректирующих элементов И, выход первого элемента сверки подключен к одному из входов схемы сравнения и ко входу триггера четности, вькоды регистра первого числа подключены к первым входам группы элементов И, ко вторым входам которой подключены выходы соответствующих поразрядных элементов коррекции, выходы группы элементов И подключены ко входам второго элемента свертки, выход которого подключен ко входу триггера, единичный выход которого подключен ко входу первого элемента И, ко второму входу которого подключен вы- ход схемы сравнения, а нулевой выход триггера подключен а первому входу втор го элемента И, второй вход которого чере элемент НЕ подключен к выходу схегЛЫ сравнения, выходы триггера переполнения, схемы сравнения, двух элементов И соединены с выходами устройства, выходы I -го и i +2-ГО корректирующих элемен тов И подключены ко входам i -го поразрядного элемента коррекции, где i lНа чертеже показана функциональная схема предлагаемого устройства для сложе ния. Устройство содержит регистр втдрого числа 1, триггер четности 2, корректирую щие элементы И 3, поразрядные элементы коррекции 4, сумматор 5, элементы сверт 6. 7 , триггер переполнения 8, регистр 9 первого числа, группу элементов И 1О, схему сравнения 11, элементы И 12, 13, элемент НЕ 14, триггер 15. Устройство работает следующим образом На первом полутакте производится запись первого числа А на регистр 1 вместе с разрядом четности. На втором лолутакте производится перепись числа А в регист 9 первого числа. Одновременно элемент свертки б образует от числа А контрольный код, который сравнивается с кодом, пр нятым на триггер четности 2. Результат, образованный схемой сравнения 11 выдает ся на выход. Аналогично принимается и контролируется второе число В. Результат контроля также формируется на схеме срав нения 11. После того, как приняты оба числа А и В, производится процесс суммирования и з пись результата на регистр 1 вместо числ В. Вначале на сумматоре 5 образуется сумма по модулю два АиВ:С А + В. Затем образуются переносы по правилу: Р-С.Ь, ..,, С; - значение суммы ло модулю два а hi - цифры чисел А, В р. - перенос в i -и разряд. После этого производится образование окончательного результата и запись в ре гистр 1, Контроль операции суммирования состоит в том, что по коду, записанному на регистре 1 к по коду первого числа, записанному на регистре 9 производится с помощью элементов порязрядной коррекции 4 и элемента свертки 7 коррекция результирующего признака четности триггера 2. Результат коррекции фиксируется на триггере 15 От результата суммирования S элементом свертки 6 образуется контрольный код, который на схеме 11 сравнивается с контрольным кодом, оставшимся от второго числа на триггере 2. Результат сравнения в прямом виде подается на вход одного из элементов И 12., а инверсия его - на вход второго элемента И 13, Если коррекция отсутствует (триггер 15 находится в нуле), то схема сравнения не срабатывает и на ее выходе присутствует низкий потенциал, что приводит к срабатыванию первого элемента И 12. Если коррекция есть, то триггер 15 находится в единице, инвертированный выход схемы сравнения имеет 1, вследствие чего срабатывает второй элемент Таким образом, при правильном суммировании на выходах элементов 12 и 13 должны быть комбинации сигналов О1 либо Ю. Наличие сигнала 1 на триггере переполнения 8 также является признаком ощибки. Процесс коррекции реализуется следующим образом. Если к 8-разрядному коду числа В с признаком четности Г прибавить число 2, , , то признак четности не меняется только при следующих комбинациях кодов, представляющих В. 1 0) (2,3y5e7S, j. l, |j 25V23ijFv2,by56T, j.a,Vj siJVS 56 , i 5, }, (4 56V56Tg , j,6, где цифры означают номера разрядов. Каждый i -и элемент поразрящной коррекции реализует одно из приведенных выражений, причем общие члены могут использоваться сразу в нескольких схемах коррекции. При срабатывании элементов коррекции на их выходах появляется низкий потенциал, соответствующий 1, Четность числа коррекций подсчитывается только для тех схем коррекции, которым соответствует единица на соответствующей позиции в записи числа на регистре 9 первого числа. Для этого выход i. -ого элемента поразрядной коррекции подается на вход I -ого элемента И Ю, а вьосоды группы элементов И Ю подаются на вход элемента свертки 7. Таким образом, за время вьшолнения операции сложения (суммирование по модулю двух операндов А и В, образование

Авторы

Даты

1976-08-15—Публикация

1974-07-29—Подача