(54) ВРЕМЕННОЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| ВРЕМЕННОЙ ДИСКРИМИНАТОР | 1971 |

|

SU297002A1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Умножающий широтно-импульсный модулятор | 1989 |

|

SU1780090A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Ш-ТЕХШНЕЗКАЯВЧВЛИОТЕКЛ | 1971 |

|

SU310377A1 |

| АВТОРУЛЕВОЙ, РЕАЛИЗУЮЩИЙ ПРОПОРЦИОНАЛЬНО- ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ ЗАКОН УПРАВЛЕНИЯ | 1968 |

|

SU213943A1 |

| Коммутационный фазометр | 1977 |

|

SU732761A1 |

| Цифровой временной дискриминатор | 1986 |

|

SU1394400A2 |

| Устройство шумовой автоматической регулировки усиления | 1990 |

|

SU1753584A1 |

| КОДИРУЮЩИЙ ОПТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ УГЛОВЫХ ПЕРЕМЕЩЕНИЙ СКАНИРУЮЩЕГО ЛУЧА В СИСТЕМЕ ТЕЛЕОРИЕНТИРОВАНИЯ УПРАВЛЯЕМОГО ОБЪЕКТА | 1997 |

|

RU2117901C1 |

1

Изобретение относится к электронной автоматике и может быть использовано для определения временного положения импульсного сигнала.

Известен дискриминатор, содержащий

два каскада, каждый из которых содержит последовательно соединенные интегратор и вычитающее устройство. Импульсный сигнал подается на входы обоих каналов. Выходы первого и второго кашала подключены ко входам вычитающего устройства. На вычитающее устройство подаются селектирующие полустробы.

Коммутация полезного сигнала в процессе его интегрирования существенно снижает точность определения временного положения условной точности в особенности при малой длительности интегрируемого сигнала. Кроме того, наличие двух каналов обработки сигнала приводит к усложнению устройства.

В предложенное устройство введены элемент задержки и масщтабный элемент, причем выход интегратора подключен ко входам элемента задержки и масштабного эле-

мента, выходы которых, подключены ко входу вь-читающего устройства. Это позволяет повысить точтэсть устройства.

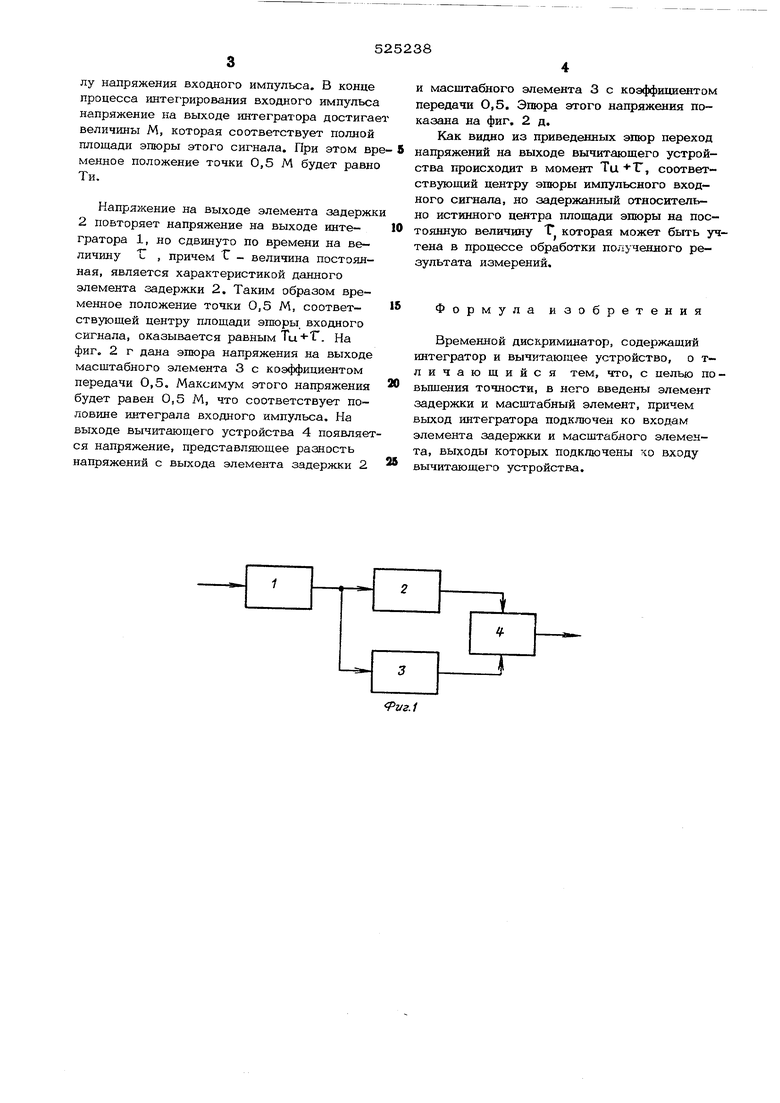

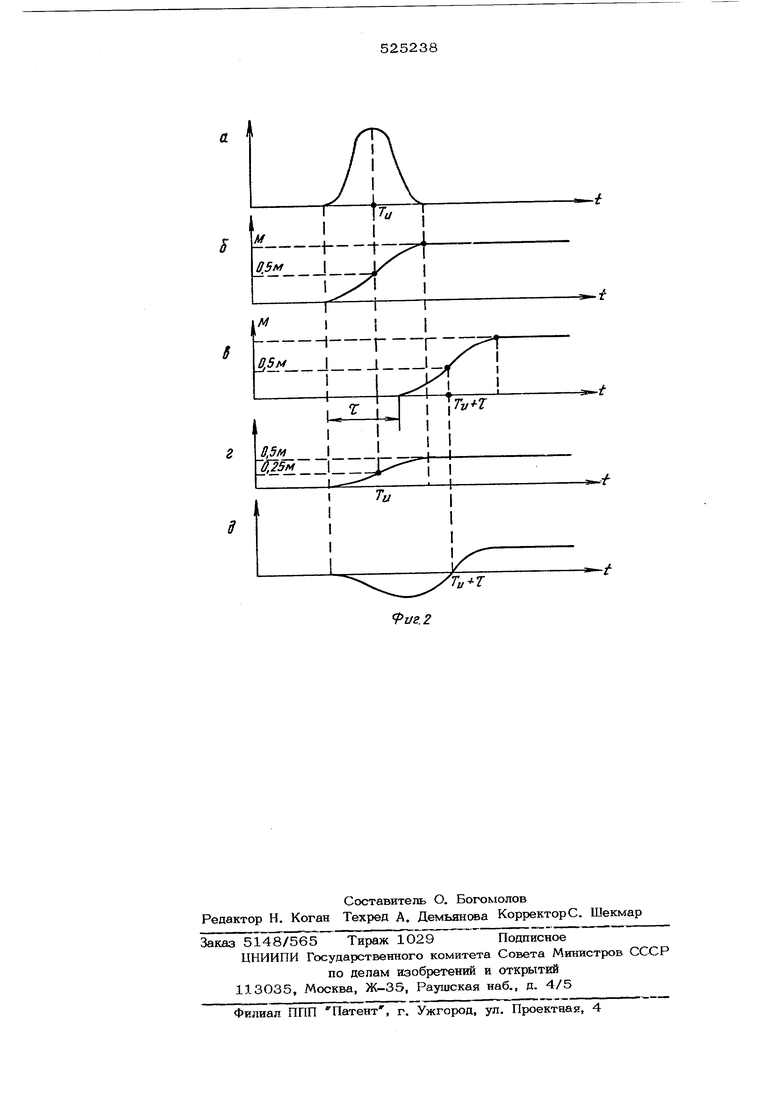

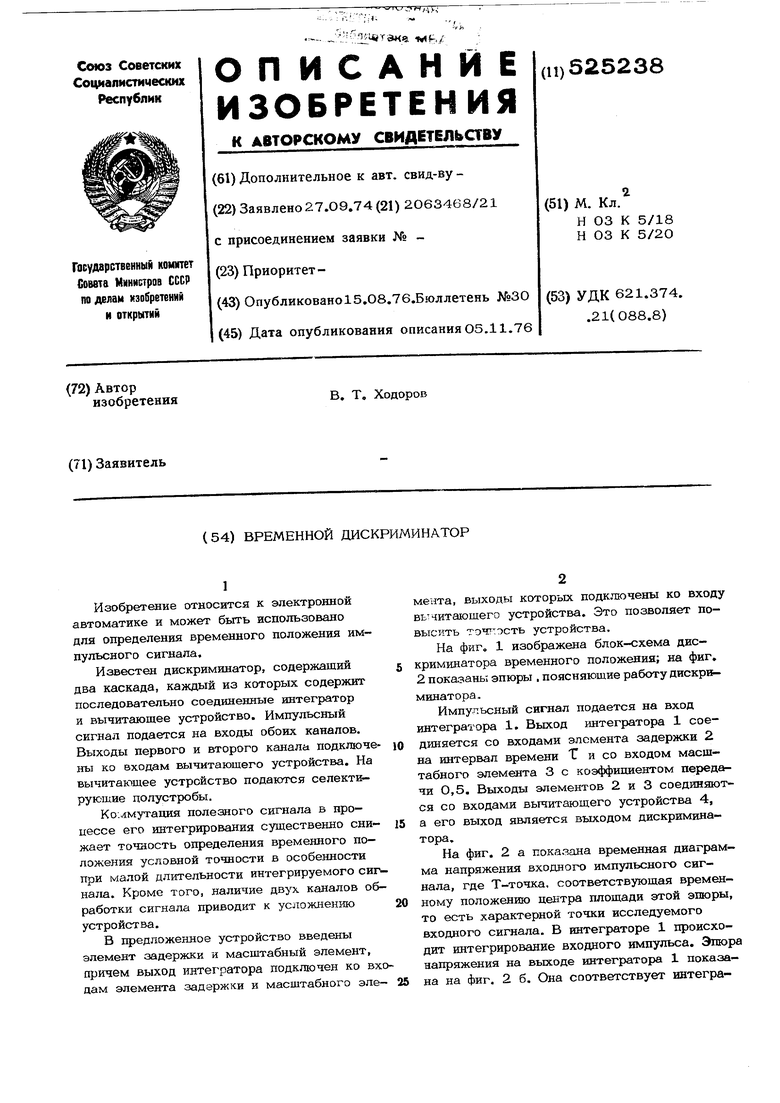

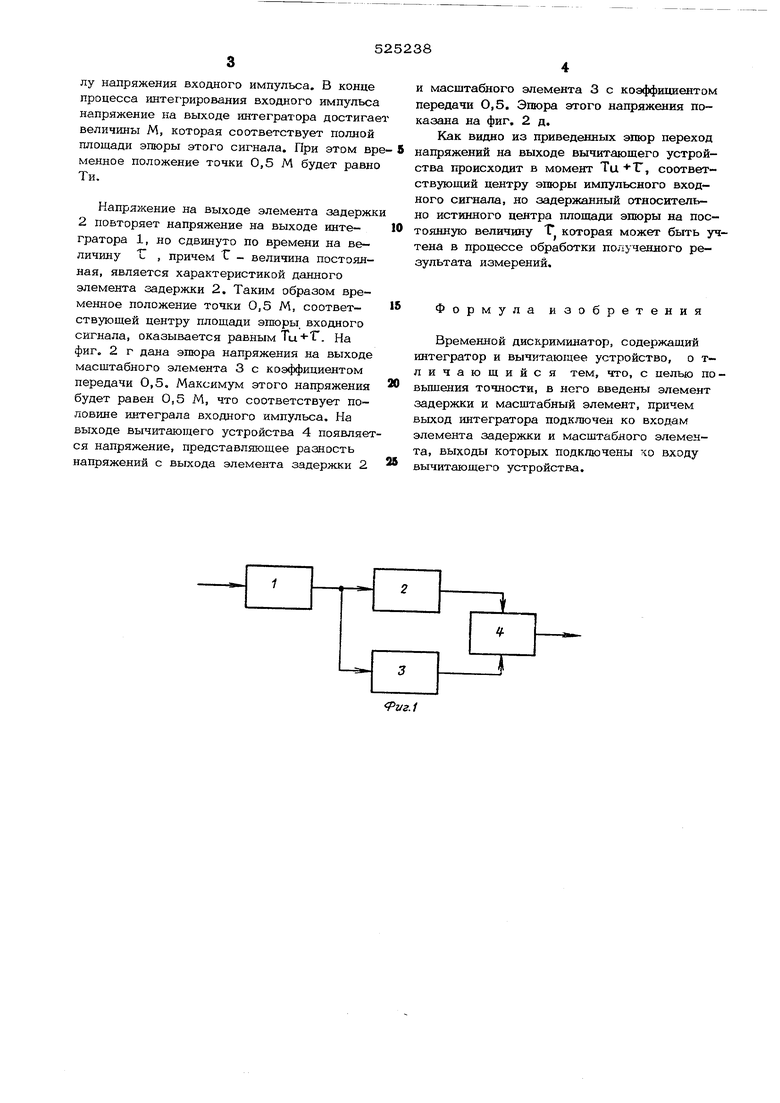

На фиг. 1 изображена блок-схема дискриминатора временного положения; на фиг. 2 показаны эпюры , поясняющие работу дискриминатора.

Импульсный сигнал подается на вход интегратора 1. Выход интегратора 1 соединяется со входами элемента задержки 2 на интервал времени Т и со входом масштабного элемента 3 с коэффипиентом передачи 0,5. Выходы элементов 2 и 3 соединяются со входами вычитающего устройства 4, а его выход является выходом дискриминатора.

На фиг. 2 а показана временная диаграмма напряжения входного импульсного сигнала, где Т-точка, соответствующая временному положению центра площади этой эпюры, то есть характерной точки исследуемого входного сигнала. В интеграторе 1 происходит интегрирование входного импульса. Эпюр напряжения на выходе интегратора 1 показана на фиг. 2 б. Она соответствует интегралу напряжения входного импульса. В конце процесса интегрирования входного импульса напряжение на выходе интегратора достигае величины М, которая соответствует полной площади эпюры этого сигнала. При этом вре менное положение точки 0,5 М будет равно Ти.

Напряжение на выходе элемента задержки 2 повторяет напряжение на выходе инте- гратора 1, но сдвинуто по времени на величину Т , причем Г величина постоянная, является характеристикой данного элемента задержки 2, Таким образом временное положение точки 0,5 М, соответствующей центру площади эшоры, входного сигнала, оказывается равным . На фиг. 2 г дана эпюра напряжения на выходе масштабного элемента 3 с коэффициентом передачи 0,5. Максимум этого напряжения будет равен 0,5 М, что соответствует половине интеграла входного импульса. На выходе вычитающего устройства 4 появляется напряжение, представляющее разность напряжений с выхода элемента задержки 2

и масщтабного элемента 3 с коэффициентом передачи 0,5. Эпюра этого напряжения показана на фиг. 2 д.

Как видно из приведенных эпюр переход напряжений на выходе вычитающего устройства происходит в момент Та ТГ, соответствующий центру эпюры импульсного входного сигнала, но задержанный относительно истинного центра площади эпюры на постоянную величину Т которая может быть учтена в процессе обработки полученного результата измерений.

Формула изобретения

Временной дискриминатор, содержащий интегратор и вычитающее устройство, о тличающийся тем, что, с целью повьшхения точности, в него введены элемент задержки и масщтабный элемент, причем выход интегратора подключен ко входам элемента задержки и масщтабного элемента, выходы которых подключены ко входу вычитающего устройства.

S М

l

f

Авторы

Даты

1976-08-15—Публикация

1974-09-27—Подача