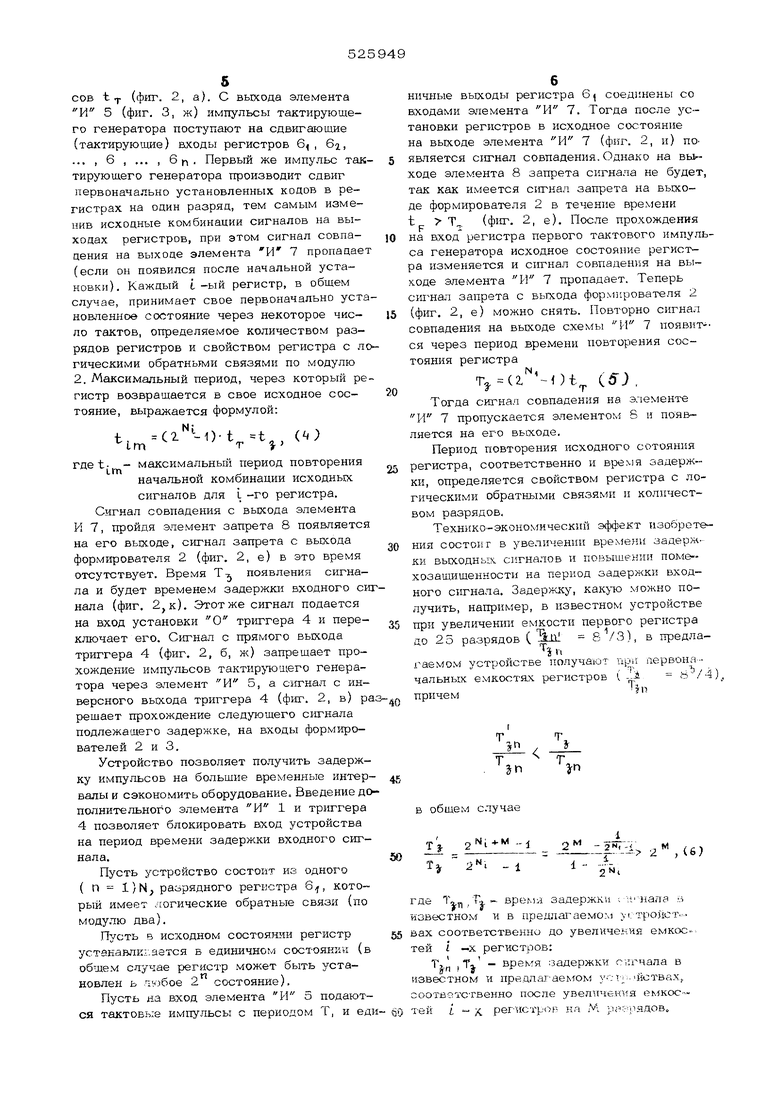

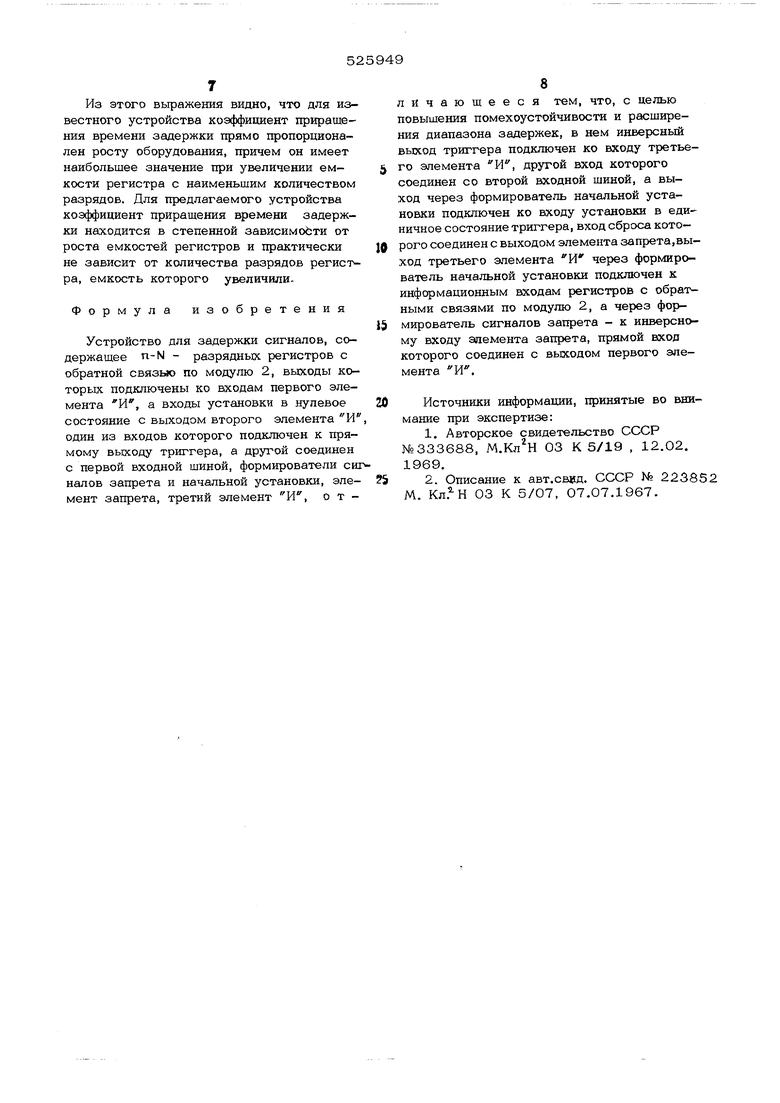

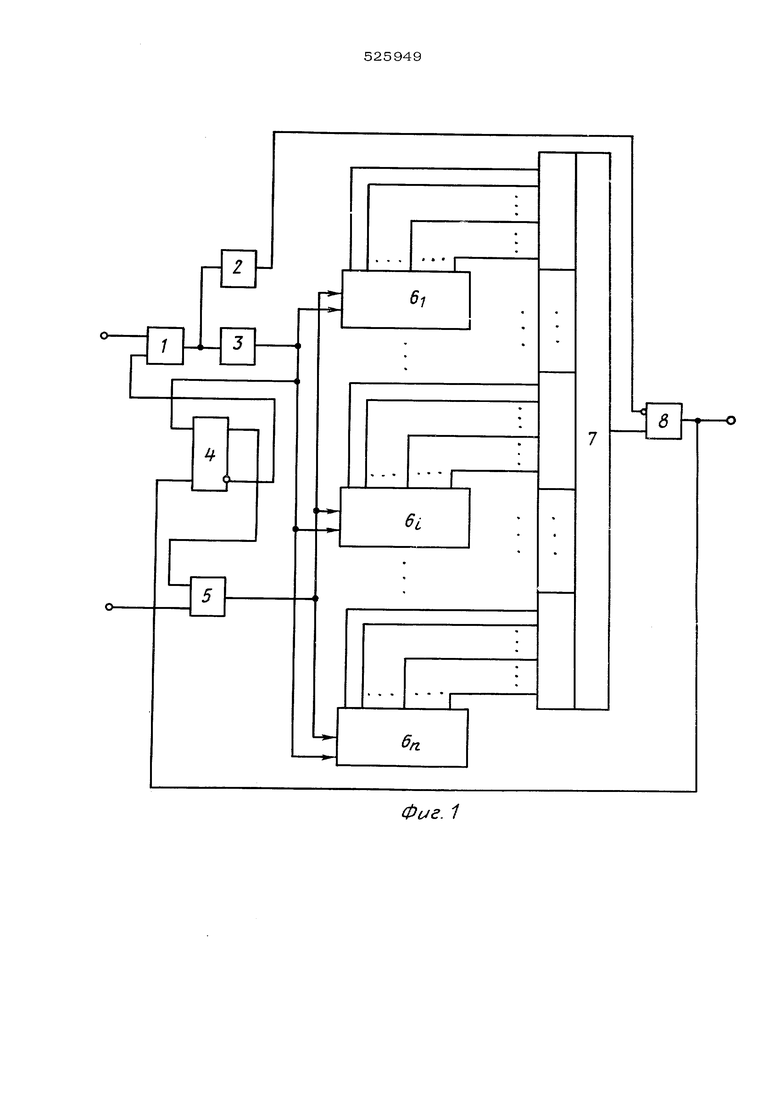

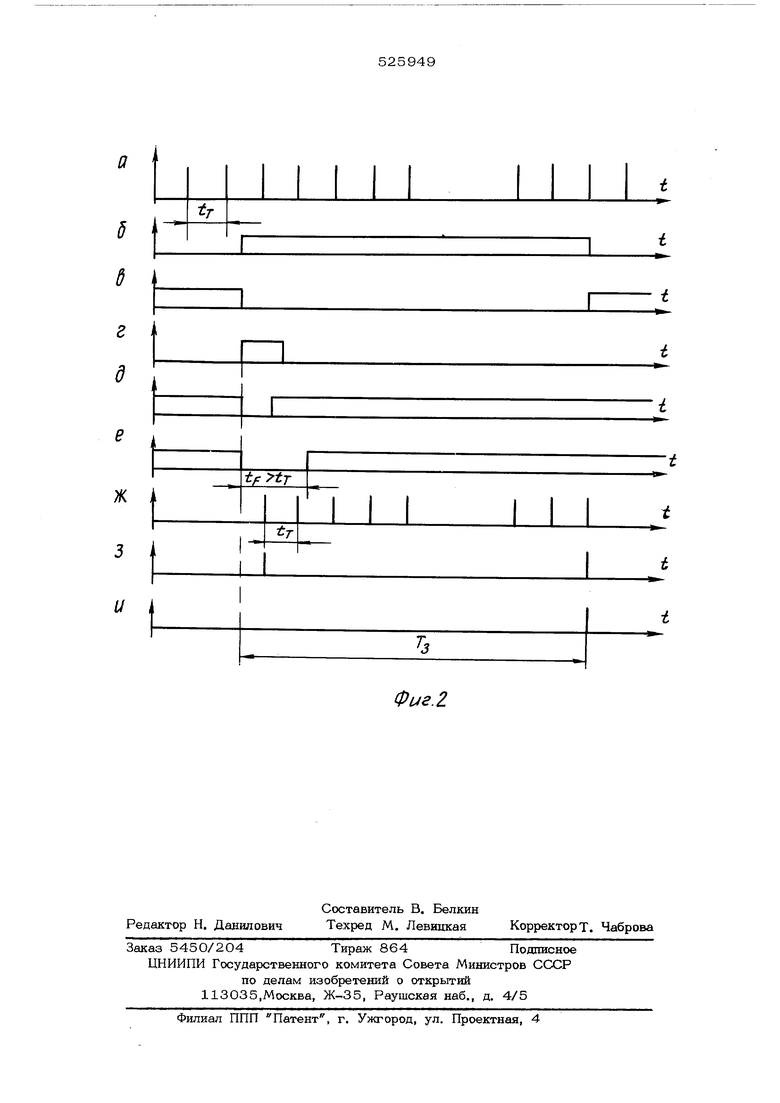

(54) УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ - длительность периода еледо Т ваниятектирующего сигнала - количество разрядов L -го регистра. Поскольку емкости (количество разрядов) регистров вьфажены взаимно простыми числами, только через время Т, равноеT,...N(2) в первые разряды всех регистров вновь за писываются 1. Это время является временем задержки в данном устройстве. Данное устройство не имеет защиты (б кировки) от сигналов помех на входе устройства на период (интервал) времени з держки; для расширения диапазона задержки импульсов требуется большое количество оборудования. Целью изобретения является повышение помехоустойчивости и расширение диапазон задержки устройства. Это достигается тем, что в предлагаемом устройстве инверсный выход триггер подключен ко входу третьего элемента И другой вход которого соединен с второй входной шиной, а вькод через формирователь начальной установки подключен ко вх ду установки в единичное состояние триггера, вход сброса которого соединен с выходом элемента запрета, выход третьего элемента И через формирователь начальной установки подключен к информационны входам регистров с обратными связями по модулю 2, а через формировачель сигнало запрета - к инверсному входу элемента запрета, прямой вход которого соединен с ВЕяходом первого элемента И. Это позволило в общем случае получить временной интервал задержки, равный произведению длительностей максимальных пе риодов генерируемых последовательностей всех регистров на длительность периода следования импульсов тактирующего генератора, выходным сигналом управлять входом устройства задержки. Время задержки в этом случае определяется выражением: т t С ).. .(2.... ... , С5) где t - период следования тактовых импульсов;N - количество разрядов в i. -ом регистре, хфичем /N.-N./ . На фиг. 1 дана функциональная схема предлагаемого устройства: на фиг. 2 - временная диаграмма работы устройства. Предлагаемое устройство содержит элемент , формирователь 2 сигнала запрета и формирователь 3 начальной установки, триггер 4, элемент И 5, регистры 6 62....6...6 сдвига с логическими обратными связями по модулю 2, элемент И 7, элемент запрета 8. Устройство работает следующим образом. Входной импульсный сигнал, который необходимо задержать, подается на вход элемента И 1, на второй вход которого подается разрешающий потенциал с инверсного триггера 4. С выхода элемента И 1, сигнал поступает на входы формирователей 2 и 3. С выхода формирователя 2 на инверсный вход элемента 8 запрета подается сигнал запрета, который запрещает пояааение ложных сигналов задержки на выходе элемента 8 запрета непосредственно после установки в исходное состояние регистров. Сигнал запрета имеет длительность, определяемую условием: где t,p - период следования импульсов Taiiтовой частоты; t р - длительность импульСа, сформированного формирователем 2; Т - время задержки сигнала в устройстве (фиг. 2, к). С выхода формирователя 3 на входы регистров 6, б2, 6f поступает импульс, устанавливающий все регистры в исходное состояние, например в единичное. После этого на вьгходах всех регистров 6f, 62, ... , 6п появляются начальные комбинации сигналов, при которых возможно появление сигнала на выходе ачемента И 7, однако на выходе элемента 8 запрета сигнала не будет, так как на его инверсный вход подан запрещающий сигнал с выхода формирователя 2 (фис. 2, е, и, к). Одновременно сигнал с выхода формирователя 3 (фиг. 2, д) подается на вход установки 1 триггера 4, переключая его. При этом с инверсного выхода триггера 4 подается запрещающий потенциал (фиг. 2,в) на второй вход элемента И 1 и происхождение других сих налов (помех) на вход формирователей 2 и 3 на период времени задержки первого сигнала запрещается и достигается защита устройства от помек по входу. Разрешающий потенциал с прямого выхода триггера 4 (см. фиг, 2, б) подается на вход элемента И 5. на второй вход которого подаются импульсы тактирующего генератора с периодом следоваш я импульсов t т (фиг. 2, а). С выхода элемента И 5 (фиг. 3, ж) импульсы тактирующего генератора поступают на сдвигающие (тактирующие) входы регистров 6, , 6а, -. , 6 , ... , бп- Первый же импульс так тирующего генератора производит сдвиг первоначально установленных кодов в регистрах на один разряд, тем самым изменив исходные комбинации сигналов на выходах регистров, при этом сигнал совпадения на выходе элемента И 7 пропадае (если он появился после начальной установки). Каждый t-ый регистр, в общем случае, принимает свое первоначально уст новленное состояние через некоторое число тактов, определяемое количеством разрядов регистров и свойством регистра с л гическими обратными связями по модулю 2. Максимальный период, через который ре гистр возвращается в свое исходное соетояние, выражается формулой: - максимальный период повторения начальной комбинации исходных сигналов для 1 -го регистра. Сигнал совпадения с вькода элемента И 7, пройдя элемент запрета 8 появляется на его выходе, сигнал запрета с выхода формирователя 2 (фиг. 2, е) в это время отсутствует. Время Т появления сигнала и будет временем задержки входного си нала (фиг. 2jK). Этот же сигнал подается на вход установки О триггера 4 и переключает его. Сигнал с прямого выхода триггера 4 (фиг. 2, б, ж) запрещает прохождение импульсов тактир тощего генератора через элемент И о, а сигнал с инверсного выхода триггера 4 (фиг. 2, в) p рещает прохождение следующего сигнала подлежащего задержке, на входы формирователей 2 и 3, Устройство позволяет получить задержку импульсов на большие временные интер валы и сэкономить оборудование. Введение до полнительного элемента И 1 и триггера 4 позволяет блокировать вход устройства на период времени задержки входного сигнала. Пусть устройство состоит из одного ( п 1)N, разрядного регистра 6/,, который имеет логические обратные связи (по модулю два). Пусть в исходном состоянии регистр устакавли.иается в единичном состоянии (в общем случае регистр может быть установлен ь либое 2 состояние). Пусть ла вход элемента И 5 подаются тактовые импульсы с периодом Т, и ед ничные выходы регистра 6) соединены со входами апемента И 7. Тогда после установки регистров в исходное состояние на выходе элемента И 7 (фиг. 2, и) появляется сигнал совпадения. Однако на выходе элемента 8 запрета сигнала не будет, так как имеется запрета на выходе формирователя 2 в течение времени t Т. (фиг. 2, е). После прохождения на вход регистра первого тактового импульса генератора исходное состояние регистра изменяется и сигнал совпадения на выкоде элемента И 7 пропадает. Теперь запрета с выхода формирователя 2 (ф1сг. 2, е) можно снять. Повторно сигнал совпадения на выходе схемы 1-1 7 появит ся через период времени повторения состояния регистра (5). Тогда совпадения на алементе И 7 пропускается элементом 8 и появляется на его выходе. Период повторения исходного сотояния регистра, соответственно и время задержки, определяется свойством регистра с логическими обратными связями и количеством разрядов. Технико-экономический эффект изобретения состоит в увеличении времени задерх ки выходньц сигналов и повышен;-п1 поме хозащищенности на период задержки входного сигнала. Задержку, какую можно получить, например, в известном устройстве при увеличении емкости первого регистра цо 25 разрядов (Зш ), в предлагаемом устройстве получают первоначальных емкостях регистров { --,i ), li,, причем в общем случае jy. ,,-j 2 -1р::1- 2Г(6) Т 2 i де ,,- время задержки ; нала .; звестном и в предлагаемом |;тронст.ах соответственно до увел1{че.кия емксх; ей / -X регистров: Т-. ,Та - время задержки сигнала в звестном и предлагаеьтом уг;т м. lijcTBax,. оответственно после увеличения емкосей i - X. регистров на 1 рй-Грядов. Из этого вьфажения видно, что для известного устройства коэффициент приращения времени задержки прямо пропорционален росту оборудования, причем он имеет наибольшее значение при увеличении емкости регистра с наименьшим количеством разрядов. Для предлагаемого устройства коэффициент приращения времени задержки находится в степенной зависимости от роста емкостей регистров и практически не зависит от количества разрядов регистра, емкость которого увеличилиФормула изобретения Устройство для задержки сигналов, содержащее n-N - разрядных регистров с обратной связыо по модулю 2, вьзходы которых подключены ко входам первого элемента И, а входы установки в нулевое состояние с выходом второго элемента И один из входов которого подключен к прямому выходу триггера, а другой соединен с первой входной шиной, формирователи си налов запрета и начальной установки, элемент запрета, третий элемент И, о т личающееся тем, что, с целью повышения помехоустойчивости и расширения диапазона задержек, в нем инверсный выход триггера подключен ко входу третьего элемента И, другой вход которого соединен со второй входной шиной, а выход через формирователь начальной установки подключен ко входу установки в еди яичное состояние триггера, вход сброса которого соединен с выходом элемента запрета,выход третьего элемента И через формирователь начальной установки подключен к информационным входам регистров с обратными связями по модулю 2, а через формирователь сигналов запрета - к инверсному входу элемента запрета, прямой вход которого соединен с выходом первого элемента И, Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР №333688, М. 03 К 5/19 , 12.02, 1969. 2.Описание к авт.сввд. СССР № 223852 М. 03 К 5/07, 07.07.1967.

6l

/ --

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1979 |

|

SU853787A1 |

| Устройство формирования временных интервалов | 1986 |

|

SU1401585A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU907887A1 |

| Устройство для приема сигналов начальной синхронизации | 1986 |

|

SU1427585A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Программируемое устройство формирования задержки и длительности импульсов | 1977 |

|

SU639381A1 |

| Цифровой фазометр-частотомер | 1987 |

|

SU1471148A1 |

| Устройство для счета предметов,перемещаемых конвейером | 1983 |

|

SU1095209A1 |

| Пересчетное устройство | 1980 |

|

SU921093A1 |

| Делитель частоты | 1979 |

|

SU843249A1 |

Фиг. 1

Фиг. 2

Авторы

Даты

1976-08-25—Публикация

1974-04-18—Подача