1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах.

Известно устройство, содержащее суммирующий блок и группы элементов И, исполь- 5 зуемое для сравнения двух двоичных чисел fl.

Однако известное устройство не позволяет выполнять арифметические и логические операции.

Известно также арифметическое устройство, содержащее регистры, суммирующий блок, группы элементов И, группу элементов НЕ, элементы И, ИЛИ, группу элементов ИЛИ, выходы которых соединены с входами перво- 15 го регистра, выходы которого соединены с входами второго регистра, прямые выходы которого соединены с первыми входами суммирующего блока, а инверсные выходы соединены с первыми входами первой группы 20 элементов И, вторые входы которой соединены с инверсным выходом знакового разряда второго регистра, а третьи входы соединены с первой тактовой шиной и с входами группы элементов НЕ,выходы которых соединены 25

с первыми входами второй группы элементов И вторые входы которых соединены с выходами суммирующего блока, выходы элементов первой и второй групп элементов И соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, вторые входы суммирующего блока подключены к выходам третьей группы элементов И первые входы которых соединены с инверсными выходами третьего регистра, а вторые входы соедине10ны с второй тактовой щиной и первым входом элемента ИЛИ 2.

Однако это известное устройство сложное

Целью изобретения является тарощение устройства.

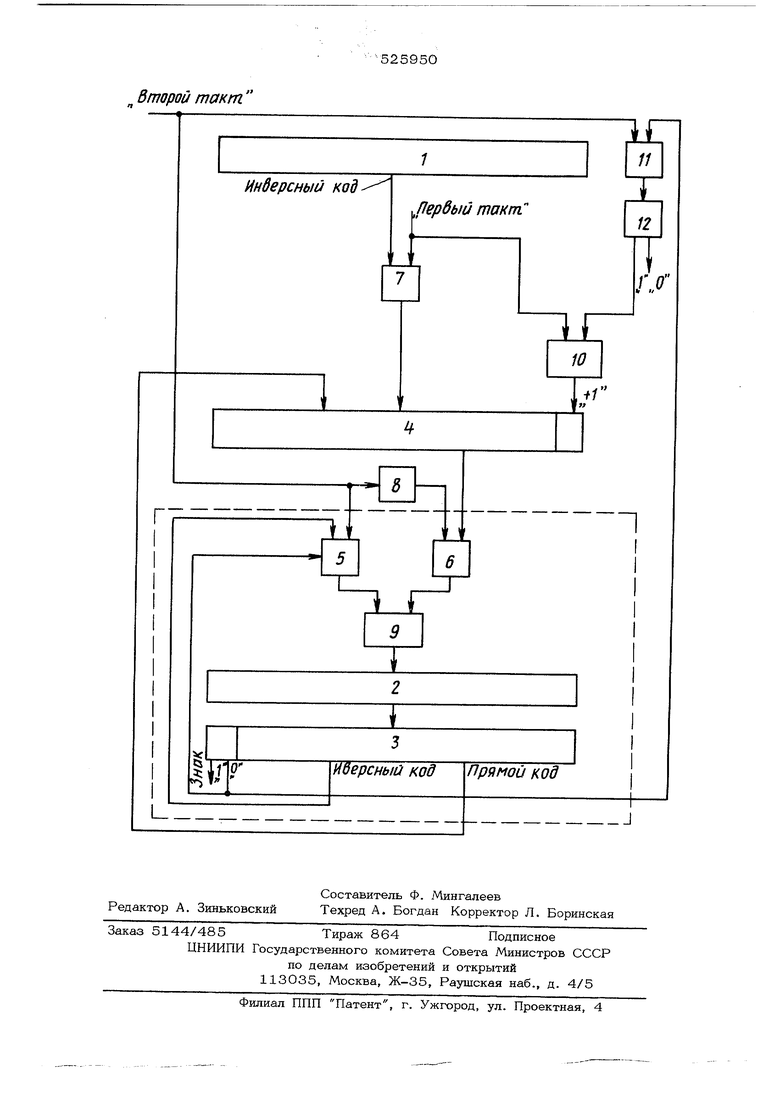

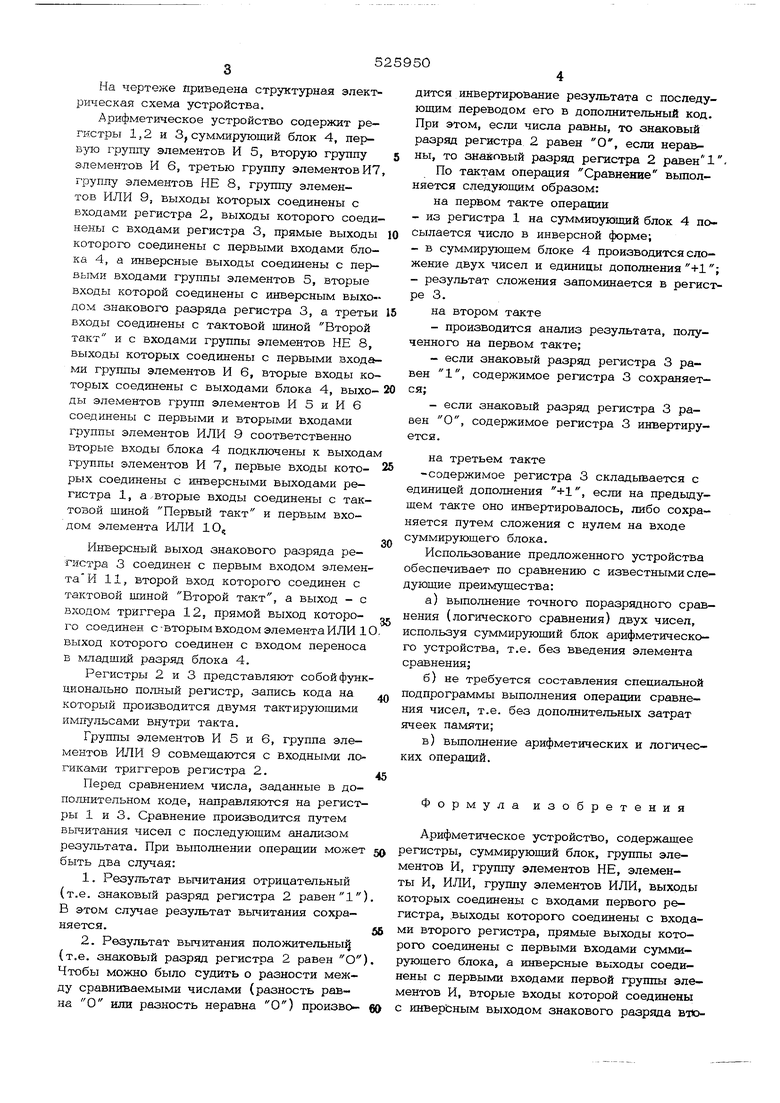

Для этого в устройство введен триггер, при этом инверюный выход знакового разряда второго регистра соединен с первым входом элемента И, второй вход которого соединен с первой тактовой шиной, а выход с входом триггера, прямой выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен со входом переноса в младщий разрад суммирующего блока. На чертеже приведена структурная электрическая схема устройства. Арифметическое устройство содержит регистры 1,2 и 3, суммирующий блок 4, первую группу элементов И 5, вторую группу элементов И 6, третью группу элементов И7 группу злементов НЕ 8, группу элементов ИЛИ 9, выходы Которых соединены с входами регистра 2, выходы которого соеди нены с входами регистра 3, прямые выходы которого соединены с первыми входами блока 4, а инверсные выходы соединены с первыми входами группы элементов 5, вторые входы которой соединены с инверсным выходом знакового разр51да регистра 3, а третьи входы соединены с тактовой шиной Второй такт и с входами группы элементов НЕ 8, выходы которых соединены с первыми входа ми группы элементов И 6, вторые входы ко торых соединены с выходами блока 4, выходы элементов групп элементов И 5 и И 6 соединены с первыми и вторыми входами группы элементов ИЛИ 9 соответственно Вторые входы блока 4 подключены к выхода группы элементов И 7, первые входы которых соединены с инверсными выходами регистра 1, а,Вторые входы соединены с тактовой шиной Первый такт и первым входом элемента ИЛИ 1О, Инверсный выход знакового разряда регистра 3 соединен с первым входом элемента И 11, второй вход которого соединен с тактовой шиной Второй такт, а выход - с входом триггера 12, прямой выход которого соединен с-вторым входом элемента И ЛИ 10 выход которого соединен с входом переноса в младший разряд блока 4. Регистры 2 и 3 представляют собой функ ционально полный регистр, запись кода на который производится двумя тактирующими импульсами внутри такта. Группы элементов И 5 и 6, группа элементов ИЛИ 9 совмещаются с входными логиками триггеров регистра 2. Перед сравнением числа, заданные в дополнительном коде, направляются на регистры 1 и 3. Сравнение производится путем вычитания чисел с последующим анализом результата. При выполнении операции может быть два случая: 1.Результат вычитания отрицательный (т.е. знаковый разряд регистра 2 равен) В этом случае результат вьгаитания сохраняется. 2.Результат вычитания положительны (т.е. знаковый разряд регистра 2 равен О Чтобы можно было судить о разности между сравниваемыми числами (разность равна О или разность неравна О) производится инвертирование результата с последующим переводом его в дополнительный код. При этом, если числа равны, то знаковый разряд регистра 2 равен 0°, если неравны, то знаковый разряд регистра 2 равен. По тактам операция Сравнение вьшолняется следующим образом: на первом такте операции -из регистра 1 на суммиоуюший блок 4 посылается число в инверсной форме; -в суммирующем блоке 4 производится сложение двух чисел и единицы дополнения -результат сложения запоминается в регистре 3. на втором такте -производится анализ результата, полученного на первом такте; - если знаковый разряд регистра 3 равен 1, содержимое регастра 3 сохраняется;-если знаковый разряд регистра 3 равен О, содержимое регистра 3 инвертируется. на третьем такте -содержимое регистра 3 складывается с единицей дополнения +1, если на предьщущем такте оно инвертировалось, либо сохраняется путем сложения с нулем на входе суммирующег-о блока. Использование предложенного устройства обеспечивает по сравнению с известными следующие преимущества: а)выполнение точного поразрядного сравнения (логического сравнения) двух чисел, используя суммирующий блок арифметического устройства, т.е. без введения элемента сравнения; б)не требуется составления специальной подпрограммы выполнения операции сравнения чисел, т.е. без дополнительных затрат ячеек памяти; в)выполнение арифметических и логических операций. Формула изобретения Арифметическое устройство, содержащее регистры, суммирующий блок, группы элементов И, группу элементов НЕ, элементы И, ИЛИ, группу элементов ИЛИ, выходы которых соединены с входами первого регистра, .выходы которого соединены с входами второго регистра, прямые выходы которого соединены с первыми входами суммирующего блока, а инверсные выходы соединены с первыми входами первой группы элементов И, вторые входы которой соединены с инверЬным выходом знакового разрада вт рого регистра, а третьи входы соединены е первой тактовой шиной и с входами грухшы элементов НЕ, выходы которых соединены с первыми входами второй группы элементов И, вторые входы которвж соединены с выходами суммирующего блока, выходы элементов первой и второй групп элементов И соединены соответственно с первыми и втооыми входами грухшы элементов ИЛИ, вторые входы суммирующего блока подключены к выходам третьей группы элементов И, первые входы которых соединены с инверсными выходами третьего регистра, и вторые входы соединены с второй тактовой шиной и первым входом элемента ИЛИ, о т л и ю щ е е с я тем, что, с целью упрог

о

JH-

.ер-

JM

единен ыход коса в млад.S,

во внИ1нятые

ельство СССР j6 F 7/02 1973. .. и др. Арифметичес /одействуюших ЭВиМ, М J, с. 249, (прототип).

Второй такт

Инверсный код

LCI

/ервыи таит. -L T

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1980 |

|

SU943706A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1980 |

|

SU940167A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Параллельно-последовательное множительное устройство | 1982 |

|

SU1156065A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Арифметическое устройство | 1976 |

|

SU703804A1 |

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

F 1

Иверсныа код

I

прямой код

Авторы

Даты

1976-08-25—Публикация

1973-08-10—Подача