сумматоров группы соединены соответственно с входами элементов памяти первой группы и с информационными входами первого блока буферных регистров, выходы переносов сумматоров группы соединены соответственно с входами элементов памяти второй группы и с информационными входами второго блока буферных регистров, выходы элементов памяти первой группы соединены соответственно с третьими входами сумматоров группы, кроме первых двух, третьи входы которых соединены с шиной логического О устройства, выходы элементов И группы соединены соответственно с оустановочными входами третьего и четвертого блоков буферных регистров, управляющие входы которых соединены соответственно с выходами первых разрядов регистров сомножителейу а входы разрешения записи первого, второго, третьего и четвертого блоков буферных регистров, элемента памяти, К -входа DK-триггера и тактовые входы первого и второго триггеров соединены с выходом :элемента ИЛИ блока управления, выходы третьего и четвертого блоков буферных регистров соединены соответственно с информационными входами четвертого и пятого(м-к) канальных селекторов, выходы которых соединены с второй группой входов сумматора,второй выход сумматора соединен с входом элемента памяти, выход которого соединен с третьей группой входов сумматора, выходы первого и второго элементов И и элемента И-ИЛИ соединены с четвертой группой входов суммаг тора, выходы первых разрядов первого и второго регистров сомножителей соединены соответственно с входами установки в 1 первого и второго триггеров, прямой выход первого триггера соединен с первьм входом первого элемента И и с первым прямым-и вторым инверсным входами элемента И-ИЛИ, прямой выход второго триггера соединен с вторым входом первого элемента И и первым инверсным и четвертым прямым входами элемента.И-ИЛИ, первьй выход синхронизации блока управления соединен с первым входом второго элемента И, третьим входом первого элемента И и вторым и третьим прямыми входами элемента И-ИЛИ, выходы дешифратора блока управления соединены соответственно с управляющими входами первого, второго, т.ретьего, четвертого и пятого (м-к)-катнальных селекторов и с входами блокировки третьего и четвертого блоков буферных регистров, а выход первого (м-к)-канального селектора соединен с вторым входом второго элемен- .. та И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый и второй регистры сомножителей, группу элементов И, группу сумматоров, первую и вторую группу элементов памяти, первый и второй блоки буферных регистров, первый, второй -и третий (м-к)-канальные селекторы, сумматор, элемент памяти, первый и второй триггеры, первый и второй элементы И, элемент ЗИ-ИЛИ и блок управления, содержащий генератор тактовых импульсов, регистр,элег мент ИЛИ, дешифратор, (м-к)-канальный селектор и DX-триггер, причем выход генератора тактовых импульсов соединен с тактовыми входами регистра и ЭК-триггера и является тактовым выходом блока управления, входы (м- к)-канального селектора блока управления соединены соответственно с выходами разрядов с (м-1)-го по (к-1)-й регистров, первый вход элемента ИЛИ соединен с входом внешней синхронизации блока управления, вход запуска блока управления соединен с входом установки в О ЗК - триггера, инверсный выход которого соединен с входом-установки егистра и является первым выходом синхроннаацин блока управления, вход сброса DK-триггера соединен с установочным входом блока управления, входы дешифратора являются входами кода разрядности блока управления, выходы дешифратора соединены с управлягадими входами (м-к)-канального селектора, выход (м-к)-канального селектора соединен с вторым входом элемента ИЛИ и является вторым выходом синхронизации блока управления, причем выходы первого и второго регистров сомножителей соединены соответственно с первыми и вторьп и входами элементов И группы, выходы которых соединены соответственно с первыми входами сумматоров группы, сл выходы элементов памяти первой группы соединены соответственно с информационными входами первого (м-к)канального селектора, выходы элементов памяти второй группы соединены соответственно с вторыми входами сумматоров группы, выходы первого и . ся второго блоков буферных регистров а соединены соответственно с информао ционными входами второго и третьего О5 (м-к)-канальньгх селекторов, выходы ел которых соединены с первой группой входов сумматора, выход которого является выходом устройства, отличающееся тем, что, с целью увеличения быстродействия,каждый разряд регистров сомножителей выполнен в виде параллельного ц; разрядного регистра, сумматоры группы выполнены в виде сумматоров нескольких чисел, в устройство введены третий и четвертьй блоки буферных регистров, четвертьй и пятьв (м-к)-канальные селекторы, причем выходы суммы

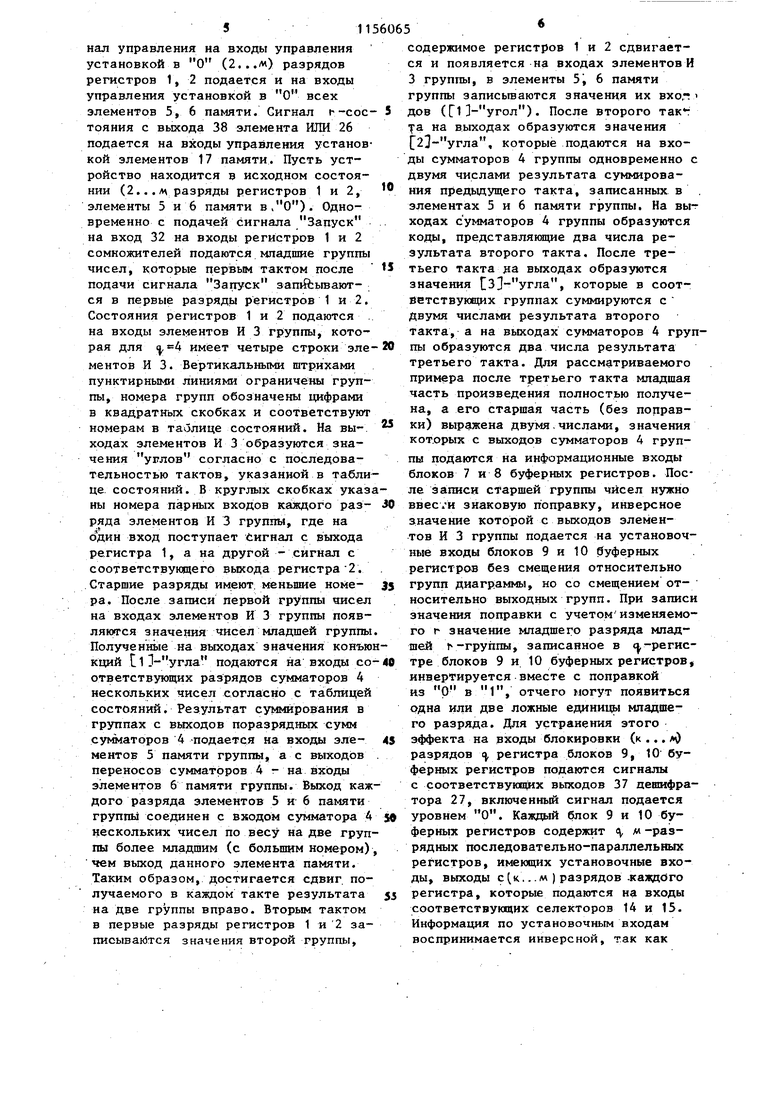

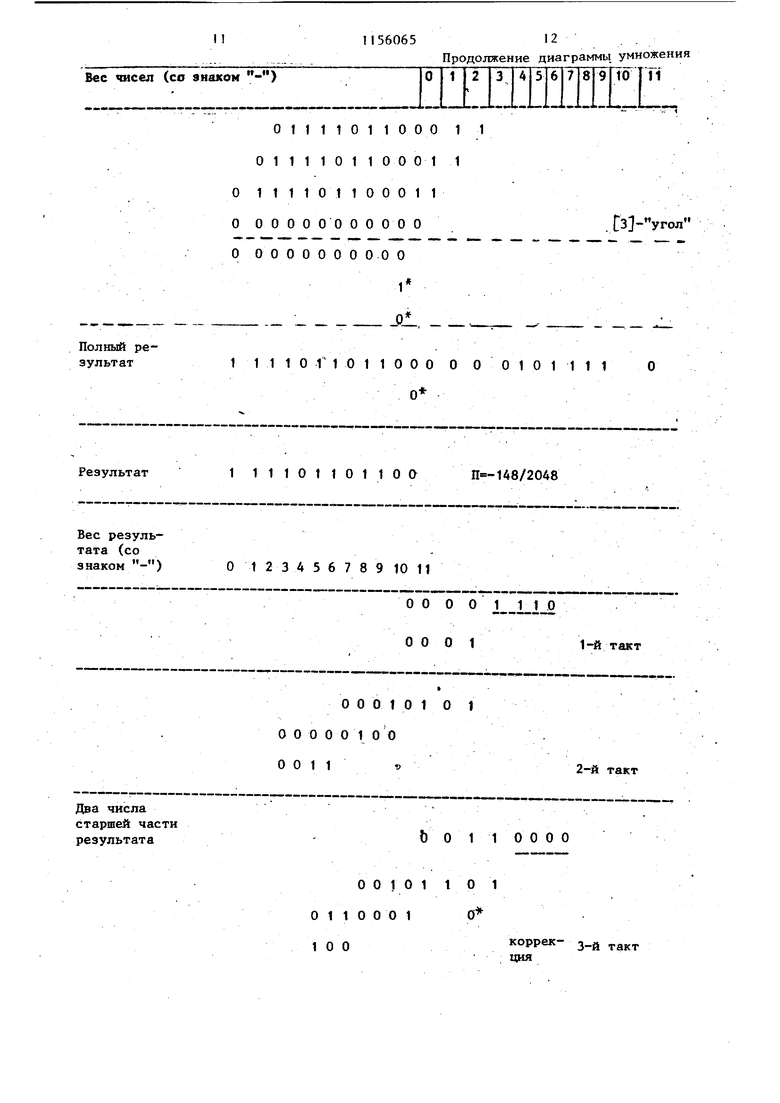

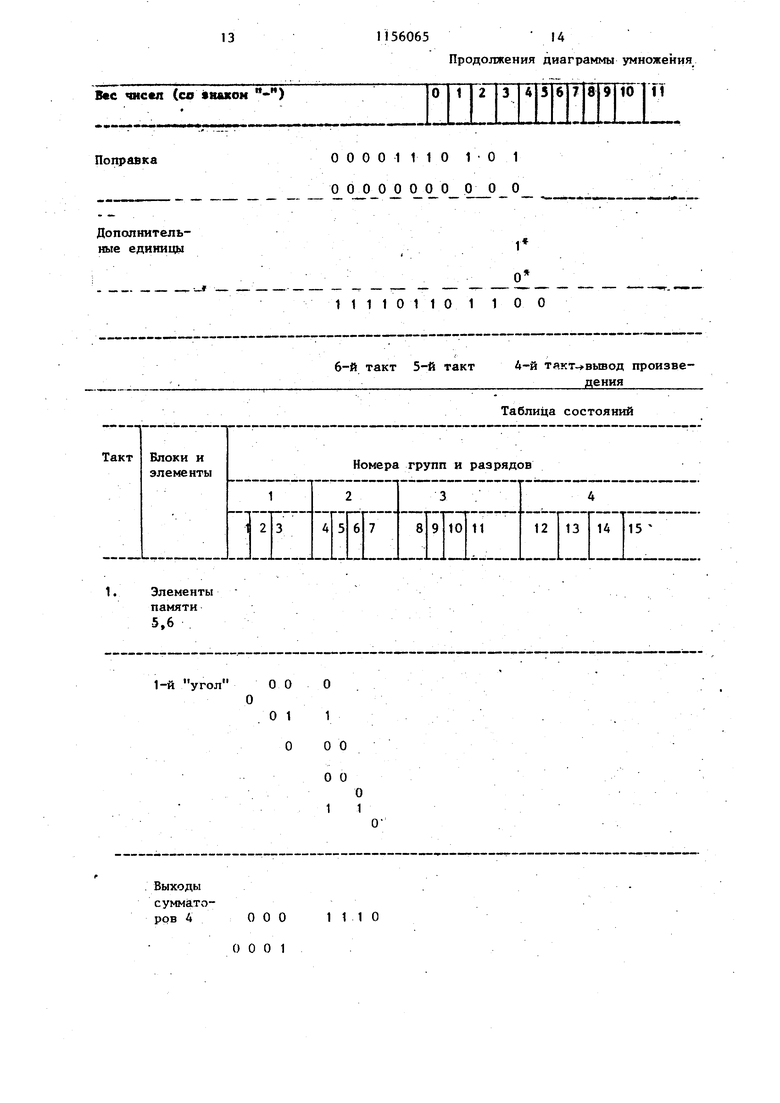

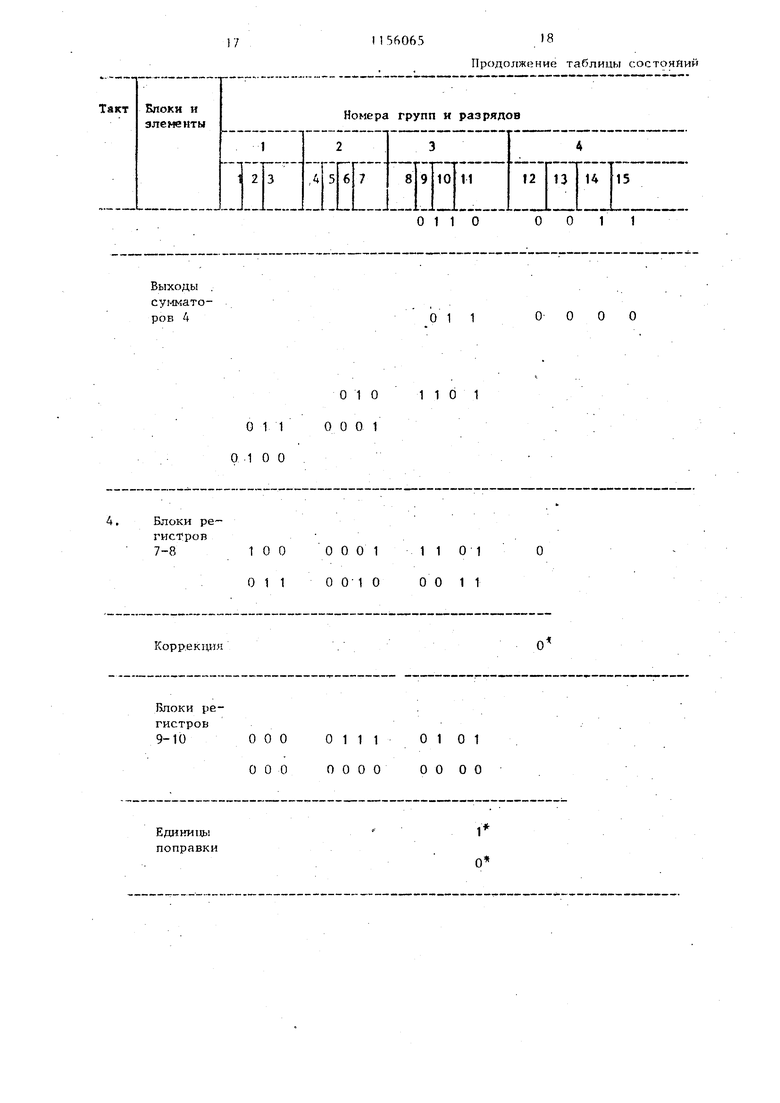

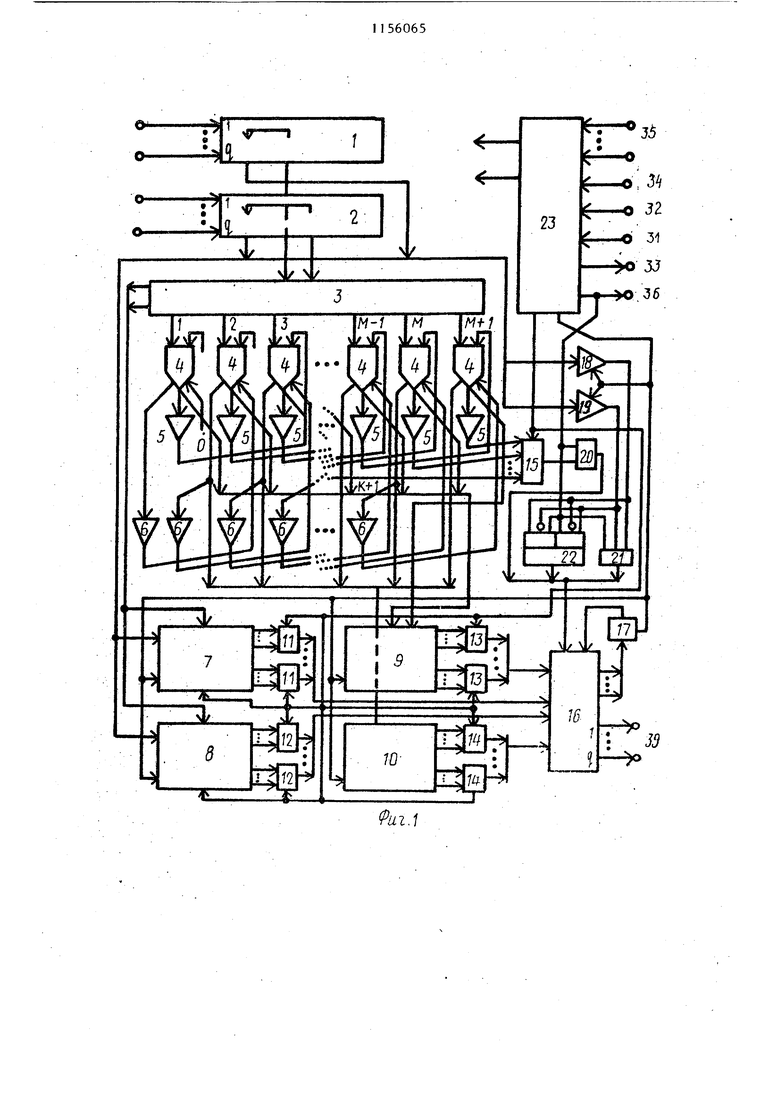

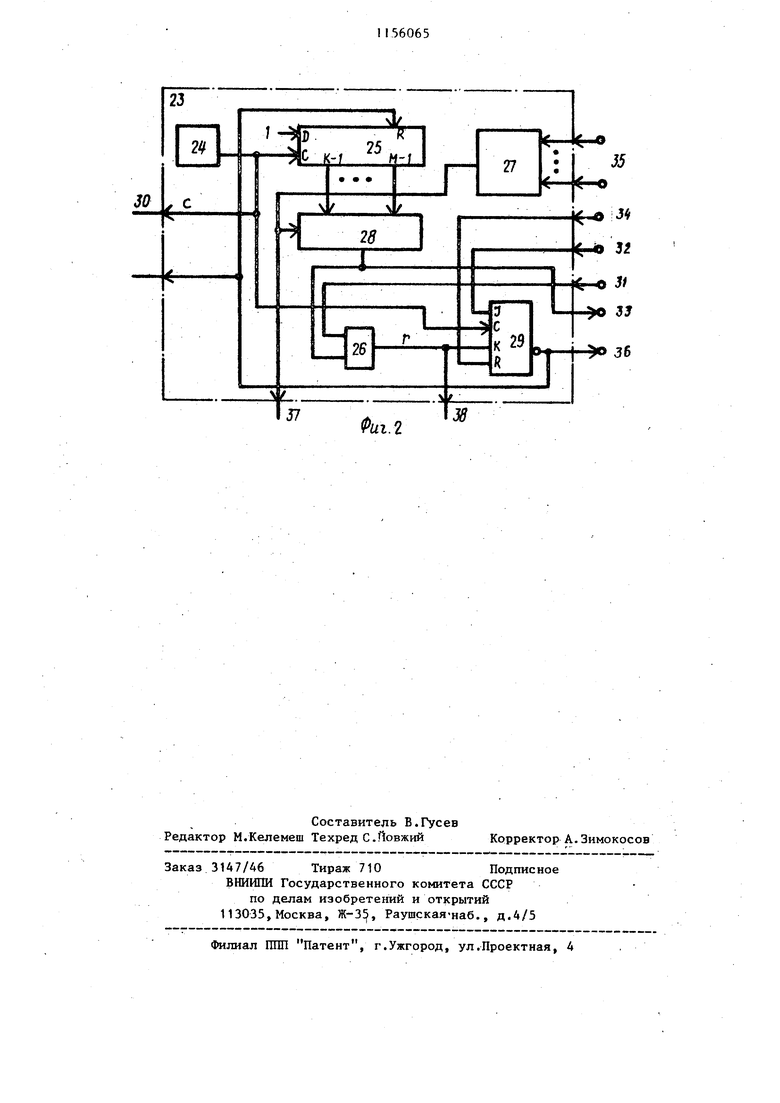

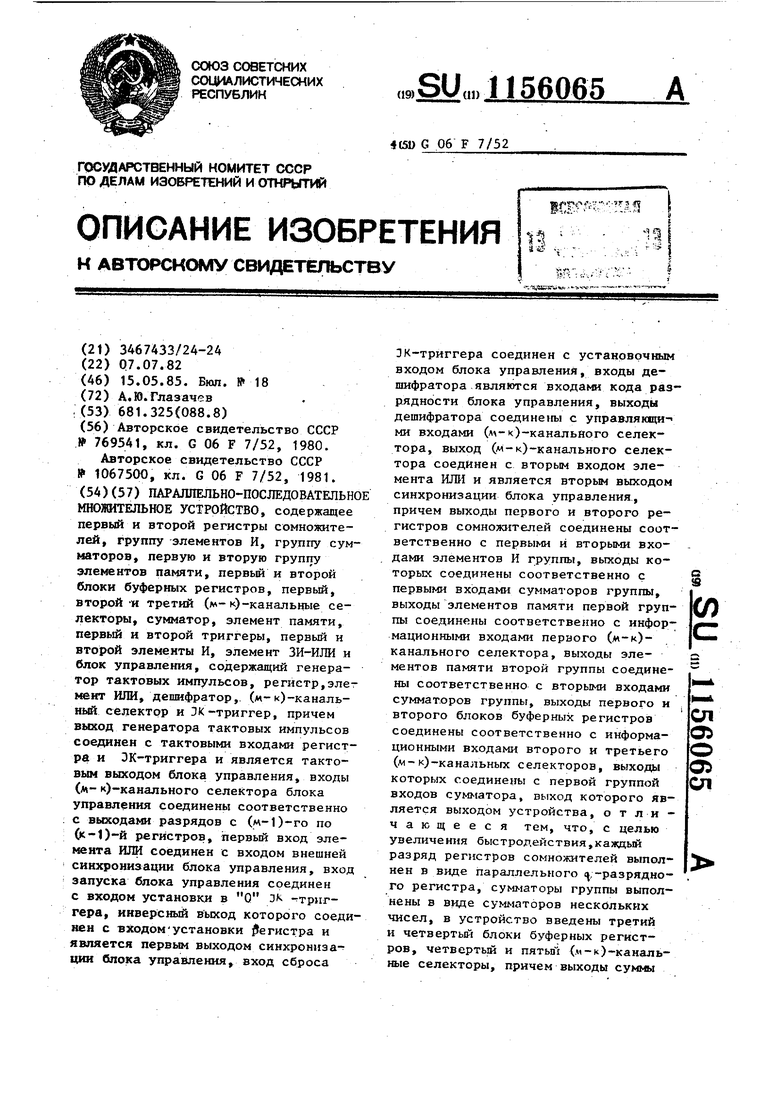

Изобретение относится к вычислительной технике и может быть использовано при построении вычислителей для умножения чисел, поступающих синхронно в дополнительном коде младшими разрядами вперед. Цель изобретения - повьш1ение бьютродействия устройства. На фиг.1 представлена функциональная схема параллельно-последова тельного множительного устройства , на фиг.2 - то же, блока управления. Параллельно-последовательное мно жительное устройство содержит первьй и второй регистры 1, 2 сомножлтёлей,группу элементов И 3,группу сумматоров 4 нескольких чисел,первую гру пу 5 элементов памяти,вторую группу 6 элементов памяти, первый 7-, второй 8, третий 9 и четвертьй 10 блоки буферных регистров, первый 11, второй 12, третий 13, четвертый 14 и пятый 15 (,)-канальные селекторы, сумматор 16, элемент 17 памяти, первый и второй триггеры 18 и 19, первый и второй -элементы И 20, 21, элемент ЗИ-ИЛИ 22, блок 23 управления. Блок 23 управления содержит гене-; ратор 24 тактовых импульсов, регистр 25, элемент ИЛИ 26, дешифратор 27, (м-к)-канальный селектор 28, JK -триггер 29. Блок 23 управления имеет тактовьй выход 30, вход 31 внешней синхронизации, вход 32 запуска, первый выход 33 синхронизации, установсчньп вход 34, входы 35 кода разрядкести, второй выход 36 синхронизации, вьтходы 37 дешифратора, выхо 38 элемента ИЛИ., Устройство имеет вы ходы 39. Рассмотрим работу устройства. Устройство перемножает п-разрядные числа, синхронно поступающие в дополнителвных кодах последовательными группами по разрядов в группе, мпадшими группами вперед. Количество групп г n/q, является целым изменяемым числом и находится в пределах от к до лл, где к - целое минимальное количество групп-, м - максимальное количество групп. В качестве примера рассмотрим умножение двух чисел разрядности , вьфаженных правильными дробями в дополнительных кодах К -157/2048, 3 1930/2048. Разрядность чисел разби та на три группы по с 4. раз ряда. Процесс умножения иллюстрирует диаграмма умножения, разрядная сетка которой разбита на группы по четыре разряда. В первом такте присутствует четыре разряда младшей первой группы чисел. Образование одноразрядных конъюнкций от умножения первой группы чисел , в разрядности четыре дает фигуру, обозначенную на диаграм ме умножения как . Этафигура состоит из нескольких простых углов с двумя ветвями, значения конъюнкций которых расположены в раз рядности двух младших групп разрядно сетки диаграммы умножения. Найдем сумму конъюнкций в каддой группе диаграммы умножения, в младшей получается окончательный результат, а в бо лее старшей группе - два числа (поразрядная сумма данной группы переносы из младшей). После записи следу ющих четырех разрядов чисел разрядной сетке диаграммьг умножения образуется фигура, обозначенная как . В калдой группе диаграммы умножения найдем сумму конъюнкций вместе с двумя числами предьиущей суммы конъюнкций После суммирования образуется следу. ющая группа разрядов результата, а в каждой старшей группе - два числа в виде поразрядных сумм и переносов соответствующих групп. Рассмотренный процесс продолжается до записи разря дов старшей группы, после чего ипад065 . .4 шая часть произведения будет полностью получена, а счаршая часть произведения (без учета знаковой поправки) - вьфажена двумя числами в виде поразрядных сумм и переносов соответствующих групп. Старший разряд груп- пы диаграммы умножения, в которой г-тактом получен окончательный результат, является мггадшим разрядом старшей части произведения, поэтому при образовании окончательного произведения к этому разряду нужно добавить значение предыдущего разряда, являющегося старшим разрядом младшей части произведения. Как видно из диаграммы умножения, при последовательном получении результата по группам значения групп при выдаче на вькодной сумматор нужно.брать со смещением на один вправо относительно сетки групп диаграмм умножения. Значения знаковой поправки, дополнительных единиц поправки и коррекции добавляются при выводе результата и суммируются в соответствукщих группах с полученными двумя числами старшей части произведения. Результат получают на выходах 39 последовательными группами (младшими группаьти, вперед) в дополнительном коде. Для проведения одного цикла умножения тре- буется (г + Птакт. В одном такте одновременно определяются cj, разрядов произведения. Максимальное количество суммируемых в каждой группе одного такта чисел равно( где 2 -1 определяет ветви углов, а 2 - два числа предыдущего такта. Для рас-сматриваемого примера при cj,4 в группе нужно суммировать 1Q чисел. На выходном сумматоре суммируются 6 чисел. Более подробно опишем работу устройства с помощью таблицы состояний. Группы перемножаеьых чисел синхронно подаются на входы регистров 1, 2 сомножителей. Знаковый разряд олжен быть записан в старшем разряе последней группы. Разряды (2...м) всех регистров 1,2 имеют входы управения установкой в О по информационным входам разрядов. Элементы 6, 5 и 17 памяти имеют входы управления установкой в О по информационным ходам элементов. Установка произвоится тактовым сигналом при наличии игнала управления установкой. Сиг- 511 нал управления на входы управления установкой в О (2...м) разрядов регистров 1, 2 подается и на входы управления установкой в О всех элементов 5, 6 памяти. Сигнал с-соетояния с выхода 38 элемента ИЛИ 26 подается на входы управления установкой элементов 17 памяти. Пусть устройство находится в исходном состоянии (2... м разряды регистров 1 и 2, элементы 5 и 6 памяти в,0)- Одновременно с подачей сигнала Запуск на вход 32 на входы регистров 1 и 2 сомножителей подаются младшие группы чисел, которые первым тактом после подачи сигнала Запуск запАьгоаются в первые разряды регистров 1 и 2. Состояния регистров 1 и 2 подаются на входы элементов И 3 группы, которая для 4 имеет четыре строки элементов И 3. Вертикальными штрихами пунктирными линиями ограничены группы, номера групп обозначены цифрами в квадратных скобках и соответствуют номерам в таблице состояний. На выходах элементов И 3 образуются значения углов согласно с последовательностью тактов, указанной в табли це состояний. В круглых скобках указ ны Номера парных входов каждого разряда элементов И 3 группы, где на один вход поступает Сигнал с выхода регистра 1, а на другой - сигнал с соответствующего выхода регистра2. Старшие разряды имеют, меньшие номера. После записи первой группы чисел на входах элементов И 3 группы появляются значения чисел младшей группы Полученною на выходах значения конъю кций подаются на входы со ответствуюдих разрядов сумматоров 4 нескольких чисел согласно с таблицей состояний. Результат суммирования в группах с выходов поразрядных сумм суьо аторов 4 подается на входы элементов 5 памяти группы, а с выходов переносов сумматоров 4 - на входы элементов 6 памяти группы. Выход каж дого разряда элементов 5 и 6 памяти группы соединен с входом сумматора 4 нескольких чисел по весу на две груп пы более младшим (с большим номером) чем выход данного элемента памяти. Таким образом, достигается сдвиг получаемого в каждом такте результата на две группы вправо. Вторым тактом в первые разряды регистров 1 и 2 записывакЗтся значения второй группы. содержимое регистров 1 и 2 сдвигается и появляется на входах элементов И 3 группы, в элементы 5 6 памяти группы записьгааются значения их вхог дов (). После второго такг fa на выходах образуются значения , которые подаются на входы сумматоров 4 группы одновременно с двумя числами результата суммирования предыдущего такта, записанных в элементах 5 и 6 памяти группы. На вы-г ходах сумматоров 4 группы образуются коды, представлянщие два числа результата второго такта. После третьего такта Д1а выходах образуются значения , которые в соответствующих группах суммируются с Двумя числами результата второго такта, а на выходах сумматоров 4 группы образуются два числа результата третьего такта. Для рассматриваемого примера после третьего такта младшая часть произведения полностью получена, а его старшая часть (без поправки) выражена двумя.числами, значения которых с выходов сумматоров 4 группы подаются на информационные входы блоков 7 и 8 буферных регистров. После записи старшей группы чисел нужно знаковую поправку, инверсное з,начение которой с выходов элементов И 3 группы подается на установочные входы блоков 9 и 10 буферных регистров без смещения относительно групп Диаграммы, но со смещением от- носительно выходных групп. При записи значения поправки с учетомизменяемого г значение младшего разряда младшей V-группы, записанное в с -регистре блоков 9 и 10 буферных регистров, инвертируется вместе с поправкой Р в 1, отчего иогут появиться из одна иди две ложные единиць младшего разряда. Для устранения этого эффекта на входы блокировки (к ... л) разрядов ц, регистра блоков 9, 10 буферных регистров подаются сигналы с соответствующих выходов 37 дешифратора 27, включенный сигнал подается уровнем О. Каждый блок 9 и 10 буферных регистров содержит «, м-разрядных последовательно-параллельных регистров, имеющих установочные входы, выходы с(к. ..м ) разрядов-каяздбго регистра, которые подаются на входы соответствующих селекторов 14 и 15. Информация по установочным входам воспринимается инверсной, так как поправка данного числа при отрицательном знаке другого числа подается инверсной. Управление переключением режимов осуществляется сигналами входов. При наличии О на входе разрешения записи включен режим сдвига, при наличии 1 на входе и 1 на управляющем входе происходит запись по установочным входам, а при наличии 1 на входе и О на управляющем входе во все разряды регистров записьшаются нули. На входы в -м подаются значения знаковых разрядов с выходов старших разрядов регистров 1 и 2, а на входы разрешения записи - значение г-состояния с выхода 38 элемента ИЛИ 26. По (г+ ь1)-му такту в регистры блоков 9 и 10 запишется значение поправки. Для рассматриваемого примера после третьего такта числа записань в регистрах 1 и 2, а на выходах сумматоров 4 группы получе11ь1 два числа неполной старшей части результата третьего такта, которые подаются На информационные входы блоков 7 и 8 буферных регистров. Значения поправки с выходов подаются на установочные входы блоков 9 и 10 буферных регистров. Сигналы с вькодов 37 де1р1фратора 27 подаются на управляющие входы селекторов 11-15 и нулевым уровнем управляют подключением ( к.„ м) разрядов регистров блоков 7-|0 к соответствующим группам входов сумматора 16, разрядность которого равна разрядност группы ( . На выходах селекторов 12-15 в каждом такте образуются в совокупности четыре числа разрядностью . После г-го такта на входы установки триггеров 18 и 19 подают; ся значения знаковых разрядов чисел, которые записываются в них по (г+1)му такту. На каждый вход селектора 11с выходов соответствуюпщх элементов 5 памяти группь подается значение ВТОРОГО по старшинству разряда поразрядной суммы каждой из ( ,..., ) групп диаграммы умножения. На выходе элемента И21 после () -го такта при любой разрядности чисел образуется значение старшего разряда младшей части произведения (коррекция На выходах элементов И 20, 21 и 22 в ()-) такте в совокупности образуется число, представляющее собой сумму разряда коррекции и дополнительных единиц поправки. Рассмотренные значения подаются на четвертую группу входов сум-1атора 16 после (г+1)-го такта при появлении единичного сигнала на первом выходе 33 синхронизации, при переходе в О ЗК-триггера 29. С выхода 38 элемента ИЛИ 26 f-состояние подается на входы разрешения записи блоков 7, 8 и блоков 9 и 10 на вход управления установкой элемента 17 записи памяти, на тактовые входы триггеров 18 и 19. По (г+1) -му такту (для приведенногопримера по четвертому) на входы сумматора 16 подаются мпадшие группы рассмотренных чисел, элементы 17 памяти устанавливаются в О, на выходах 39 сумматора 16 образуется первая группа разрядов произведения. Следующим тактом на вькодах 39 появляются значения разрядов с второй группы произведения, а в регистры 1 и 2 запишутся разряды первых групп следующей пары чисел. Одновременно с выдачей произведения предощущай пары чисел производится ввод следующей пары чисел. Работа блока 23 управления. В зависимости от значения кода разрядности входов 35 дешифратор 27 вырабатывает на одном из выходов 37 сигнал, который нулевым уровнем под- клюЧает соответствующие ключи в селекторах 11-15 и 28. Тактовый сигнал генератора 24 с выхода 30 подается.на тактовые входы всех регистров 1,2-, 7-10, элементов 5, 6 и 17-памяти, регистра 25 и триггеров 18, 19 и 29. В исходном состоянии Jk-триггер 29 находится в О, первым тактом после подачи сигнала Запуск на вход 32 триггер 29 устанавливается в 1, вторым тактом в первый разряд регистра 25 записывается единица. С каждым тактом (м-1)-разрядный регистр 25 заполняется единицами. После достижения в г-м такте разряда, подключенного к выходу селектора 28, единица проходит на выход селектора 28, откуда подается на второй, выход 36 синхронизации, .элемент ИЛИ 26, а с его выхода - на К-вход триггера 29 и выход 38. Па ( 1)-му такту триггер 29 устанавливается , ре-, гистр 25 обнуляется, с инверсного выхода Гк -триггера 29 на выход 33 подается сигнал установки. Шина 31 внешней синхронизации нужна при синхронной параллельной работе несколЬких умножителей в одной разрядности для их синхронизации от устройства управления только одного из работаищик умножителей. При автономной работе одного умножителя выход 36 синхронизации и вход 31 внешней синхронизации не используются. При синхронной параллельной работе нескольких умнояштелей в одной разрядности сигнал h -состояния с вьпсода 36 одного из умножителей подается на входы 31 внешней синхронизации всех остальных умножителей, чем производится синхронизация возможного их рассогласования в результате сбоя, где синхронизирующим являе1;9я один из умножителей. Возможна подача синхронизирукяцего сигнала -cocтoяния с выходов 36 нескольких умножителей через элемент ИЛИ 26 на вход 31 внешней синхронизации каждого умножителя, где для .каждого умножителя может использоваться свой элемент ШШ В зтом случае синхронизация производится от первого пришедшего г-соетояния любого из умножителей. Быстродействие. Цикл умножения со держит (г +1)такт, который имеет постоянную длительность, определяемую максимальным временем распространения емых

X -157/2048 У 1930/2048

1000000000000 11110-100011С2}- угол

11 1 1 0110001 1 О 1 1 1 10001010

10 ОО 000000.0 О О

01111 О 1 1 0. О О 1 1

1000000 000000

01111 о1 1 00011

1000000000000 1000000000000

1 о о о о о о о о о о о о сигнала через элементы устройства во время одного такта. А во входной части после записи очередной группы разрядов чисел в регистры 1 и 2 сигнал распространяется через один элемент И 3 группы и через один сумматор 4 нескольких чисел группы. В выходной части после очередного сдвига в регистрах блоков 7-10 максимальная цепь распространения сигнала проходит через элемент селектора 11, элемент И 21 и сумматор 16, суммирующий четыре числа. В каждом такте к-л.пичество суммируемых на сумматоре 4 группы чисел равно , а при q, 4 равно 10. Таким образом, время распространения сигнала за один такт во входной части и в целом в устройстве определяет сумматор 4 группы. При построении cyi iMaTopa 4 группы в виде многослойного сигнал распространяется примерно через 6-7 одноразрядных сумматоров на три входа и два выхода (при условии 4). В последовательно соединенных цепях логических элементов достаточно большой длительности (3) происходит сокращение времени распространения, сигнала на один элемент относительно измеряуровней в 1,5-2 раза. Диаграмма умножеяия

11

Bee чисел (со знаком -) 0 о 0 ,. Полный результат1Результат 1 Вес результата (со знаком -) О Два числа старшей части результата 0110001О

100

Продолжение цяаграммы умножения

10 |1 12 13 и|5|6|7|8|9ГТО Tl 1

Ш.11Ш.

00101 10 1

коррек- 3-й такт ция 0111101100011 0111101100011 111101100011 00000000000 3 - угол 0000000000 , - .1 - . . .. 1 1 1 О 1 1 О 1 1 О О О О О О 1 О 1 1 1 1о 1 1 1 О 1 1 О 1 1 О Q П«-148/2048 1 2 3 4 5 6 7 8 9 10 11 . . 0001010100000 1 00 001152-й такт 01, ,. -. 0000 1 1 0 00011-й такт . Ь О 1 1 О О О О

13

00001110 1-01

Попрабка 00000000 00 О

Дополнительные единицы

111101101 1 00

6-й такт 5-й такт 4-й такт- вьшод произвеЭлементы

памяти

О

О

1 о о

О 1

О

0о

11

1110

000 0001

115606514

Продолжения диаграммы умножения дения

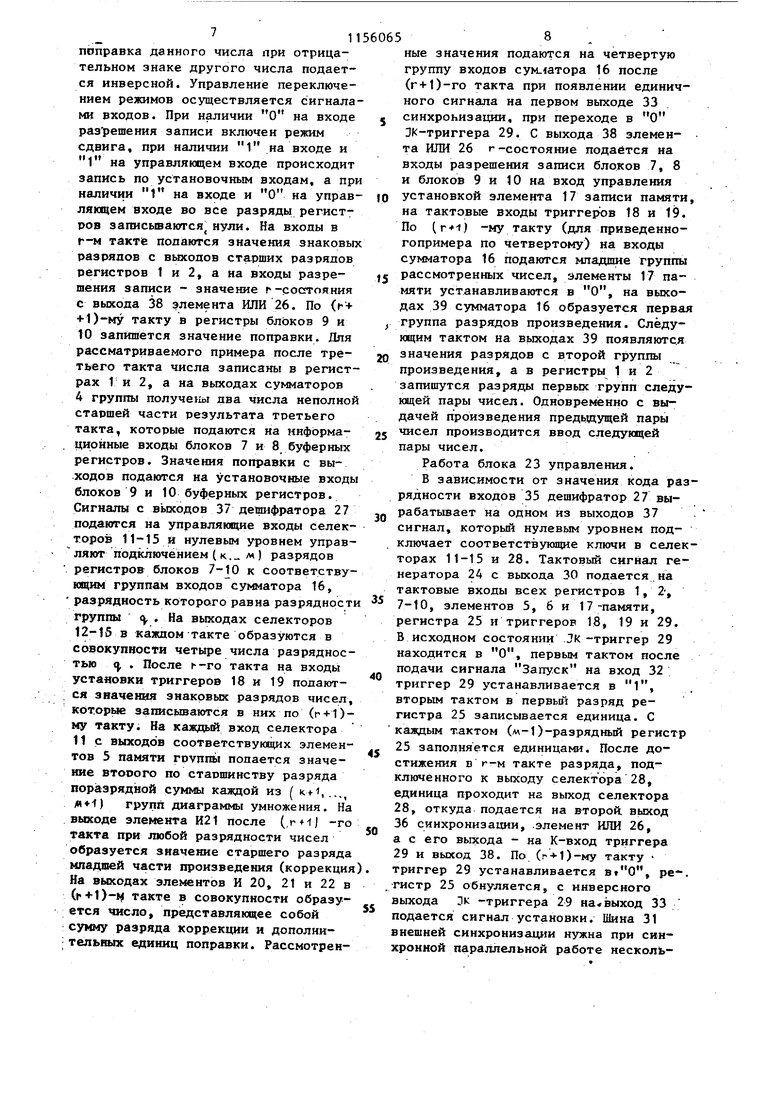

Таблица состояний

Элементы

угол

0О

0000

11 0001 0000 01

О О О О

Выходы сумматоров 4

ч:0 О О

1 11 000 1

О 1

1 О 1 О

о о о о о о

000

1 1

01 01

г/

010 0001

О 1 1 01 00

Блоки регистров

0001

1 О О 7-8 О 0-1 О О 1 1

Коррекгщя

000

0111 0000 000

ЕДИНИЩ)

поправки

Продолжение таблицы состояний

1 101

1 1 01 00 11

0101 00 00

1

О -

| Устройство для умножения последовательных п-разрядных двоичных кодов | 1978 |

|

SU769541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1982-07-07—Подача