Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки массивов данных.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности алгебраического сложения массива двоичных чисел.

На фиг.1 представлена функциональная схема заявляемого устройства; на фиг.2 - схема устройства с прошивкой постоянного запоминающего блока и ассоциативного запоминающего блока для случая четырех слагаемых.

Устройство содержит постоянный запоминающий блок 1, ассоциативный запоминающий блок 2, группы элементов И 3 - 6, элементы И 4. 11 и 19, группы элементов 7 и 8 задержки, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9, элемент ИЛИ 10, регистры 12 - 14. элемент НЕ 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, элементы И-НЕ 17 и 18, элемент 20 задержки.

На фиг.1 также указаны информационные входы 22 слагаемых устройства, соответствующие входы 21 знаков слагаемых,

вход 23 признака операции устройства, шины 25 и 26 синхронизации, шина 24 управления, последовательный выход 28 промежуточного результата, выходы 27 положительного результата, выходы 29 отри-, цательного результата, выход 30 знака результата алгебраического сложения устройства.

Устройство имеет два режима работы: алгебраическое сложение и суммирование положительных чисел.

В режиме алгебраического сложения на вход 23 устройства подается сигнал логического нуля, а на входы 21 - знаковые разряды слагаемых: 0 (для положительных чисел) и ли 1 (для отрицательных чисел),

В исходном состоянии тракты устройства обнулены. В первом такте на входы 22 слагаемых подается сигнал логического нуля. На шину 24 управления также подается сигнал логического нуля, который определяет для регистра 12 режим параллельной записи, запрещает работу элементов 7 задержки и запрещает прохождение тактовых импульсов шины 25 синхронизации через элемент И 19.

00

о

2

1 о

Ь течение тактового импульса, подаваемого по шине 26, знаковые разряды слагаемых, присутствующие на входах 21, определяют адрес слова, считываемого из блока 1. Считанное из блока 1 слово являющееся двоичным представлением количества отрицательных слагаемых (количества единиц на знаковых входах 21), по срезу этого же тактового импульса записывается в регистр 12. Начиная со второго такта, на шину 24 управления подается сигнал логической единицы, который определяет для регистра 12 сдвиговый режим работы. Сдвиг содержимого регистра 12 происходит по срезам тактовых импульсов шины 26 младшими разрядами к сдвиговому выходу. На входы 22 подаются одноименные разряды (начиная с младших) слагаемых, представленных в прямом коде, причем если знаковый разряд нулевой, то соответствующее слагаемое проходит через соответствующий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9 без изменения (в прямом коде), если же знаковый разряд равен единице, то слагаемое инвертируется соответствующим элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 9. Эти разряд: ные срезы слагаемых, поступающие на первые входы группы элементов И 3, вместе с выходным разрядом регистра 12, поступающим на первый вход элемента И 11, в течение тактового импульса, подаваемого по шине 26, определяют адрес слова, считыва- -емого из блока 1 и являющегося частью признака, подаваемого на признаковые входы блока 2, причем все разряды, кроме младшего, задерживаются на один такт элементами 7 -задержки, работа которых разрешена единичным сигналом на шине 24 управления, который также разрешает прохождение тактовых импульсов, подаваемых на-шину 25 синхронизации. Остальной частью признака являются все, кроме первого, разряды, считываемые из блока 2 и задержанные на один такт.

Сформированный признак дополнительно синхронизируется на элементах И 4-6 путем подачи сигнала по шине 25, передний фронт которого начинается позже, а задний - раньше тактового импульса, подаваемого по шине 26.

В том же такте, в котором подан, разрядный срез слагаемых, на первом выходе блока 2 появляется одноименный выходной инверсный разряд. На выходе 28 получается результат суммирования в прямом коде, если результат суммирования положительный, и в дополнительном коде, если результат суммирования отрицательный, причем последним выходным разрядом будет знаковый. Общее количество тактов, за

которое производится алгебраическое сложение, равно:

log2k + 2,

где т- количество затрачиваемых тактов; п - разрядность слагаемых: k - количество слагаемых; а -ближайшее целое число, не меньше

числа а.

После подачи необходимого количества тактов на шину 24 управления подается сигнал логического нуля, который останавливает работу регистров 13 и 14 сдвиг

содержимого которых производился по срезам тактовых импульсов шины 25. Если знаковый разряд результата присутствующий на выходе 30 нулевой, то результат сложения в прямом коде имеется на выходах 27

устройства. Если же знаковый разряд результата на выходе 30 равен единице (отрицательный результат), то результат алгебраического.сложения находится в разрядах, кроме старшего, регистра 14 и имеется на выходах 29 устройства. Перевод результата сложения из дополнительного кода, в прямой осуществляется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 16, элементами И 17 и 18 и элементом 20 задержки путем прибав

ления к инверсному коду, поступающему на

вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, единицы, задержанной на один такт элементом 20 задержки после снятия с шины 24 управления сигнала логического нуля. При этом

элемент И 17 формирует перенос в старший разряд суммы,получаемой на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16.

Таким образом, на выходах устройства получается результат алгебраического сложения в прямом и дополнительном кодах.

В режиме суммирования положительных чисел (знаковые разряды всех К слагае- мых нулевые) имеется возможность суммирования еще одного слагаемого, разряды которого подаются на вход 23 устройства. В этом режиме на шину 24 управления подана логическая единица, регистр 12 обнулен. Выходной результат получается на последовательном выходе 28 устройства

или на параллельных выходах 27 и выходе 30, причем на выходе 30 - старший разряд суммы.

Количество тактов, за которое вычисляется сумма, равно:

)

г n + log2k +1,

где т - количество затрачиваемых тактов; п -- разрядность слагаемых;

k количество слагаемых в режиме алгебраического сложения;

а - ближайшее целое число, не меньше числа а.

Работа остальных элементов устройства в этом режиме аналогична их работе в режиме алгебраического сложения.

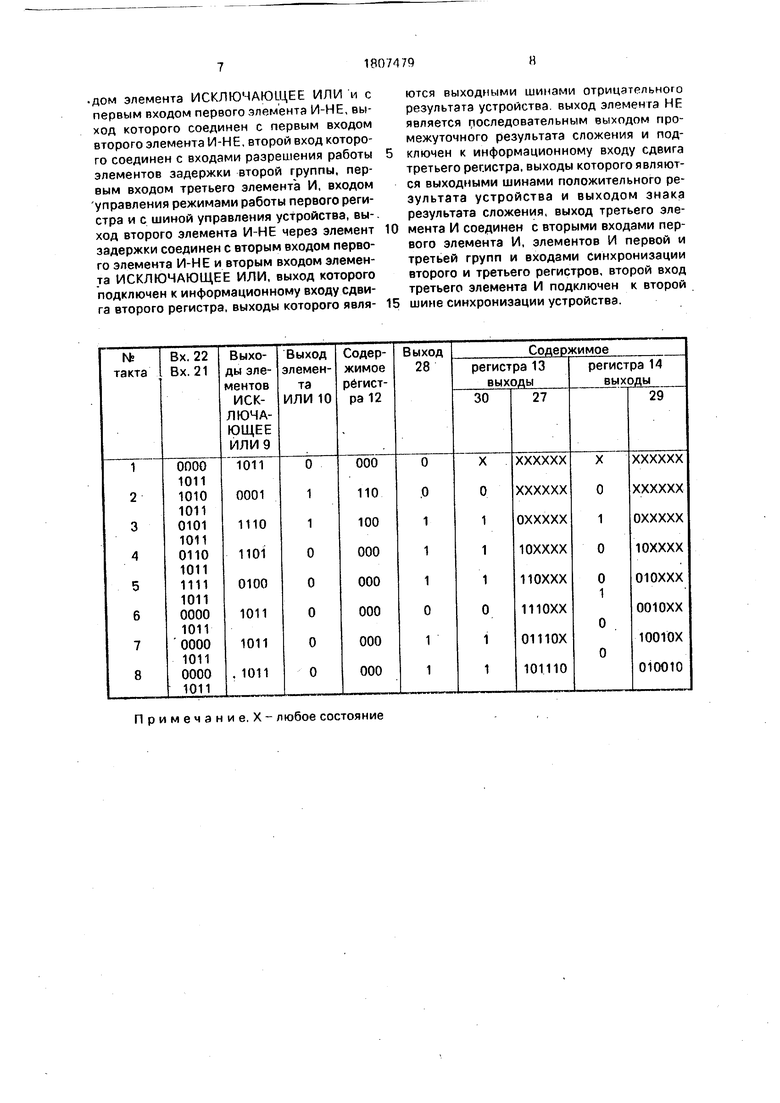

Рассмотрим пример алгебраического сложения четырех операндов, используя .прошивку блоков 1 и 2, приведенную на фиг.2.

Пусть необходимо сложить следующие числа:-1001;+1110;-1101;-1010. Знаковый срез для этих слагаемых соответственно равен 1011, т.е. имеет три отрицательных числа и одно положительное.

Состояния основных элементов устройства при вычислении алгебраической суммы этих четырех операндов приведены в табл.1, Из таблицы видно, что первый такт работы устройства используется для определения количества отрицательных слагаемых (результат записывается « регистр 12 по срезу тактового импульса на шине 26). Начиная со второго такта, производится суммирование слагаемых с попутным переводом отрицательных слагаемых в дополни- тельный код путем суммирования содержимого регистра 12 со всеми слагаемыми. Так же, начиная с второго такта, на выходе 28 получается результат в дополнительном коде, так как знаковый разряд, получаемый в восьмом такте, единичный. Этот же результат можно считать по выходам 27 и 20 регистра 13 после восьмого такта работы устройства. В прямом коде результат сложения имеем на выходах 29 устройства, причем знаковый разряд зафиксирован на выходе 30.

Итак, результат сложения равен 010010.

Техническое преимущество изобретения состоит в расширении функциональных возможностей суммирующего устройства за счет выполнения операции алгебраического сложения.

Положительный эффект изобретения заключается в совмещении в одном устройстве операций суммирования и алгебраического, сложения над массивами данных, представленных в прямом коде, что исключает необходимость машинной операции преобразования отрицательных чисел. Положительным также является возможность получения результата сложения как в прямом, так и в дополнительном кодах.

Формул а, изобретения

Суммирующее устройство,содержащее постоянный запоминающий блок, ассоциативный запоминающий блок, первый элемент И. первую, вторую и третью группы элементов И, первую и вторую группы элементов задержки, причем, кроме первого, остальные разрядные выходы ассоциатив- 5 ного запоминающего бпока через соответствующие элементы задержки первой группы соединены с первыми входами соответствующих элементов И первой группы, выходы которых подключены к входам опро0 са первой группы ассоциативного запоминающего блока, выходы элементов И второй группы соединены с адресными входами первой группы постоянного запоминающего блока, первый разрядный выход которого

5 соединен с первым входом первого элемента И, выход которого соединен с входом опроса второй группы ассоциативного запоминающего блока, остальные разрядные выходы постоянного запоминающего блока

0 через соответствующие элементы задержки второй группы соединены с первыми входами элементов И третьей группы, выходы которых соединены с соответствующими входами опроса третьей группы ассоциатив5 ного запоминающего блока, первая шина синхронизации устройства соединена с первыми входами элементов И второй группы, отличающееся тем, что, с целью расширения функциональных возможно0 стей путем выполнения операции алгебраического сложения над массивами данных, в него введены группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, второй и третий элементы И. первый, второй и третий реги5 стры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы И-НЕ, элемент задержки и элемент НЕ, причем вторые входы элементов И второй группы соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ

0. ИЛИ группы, первые входы которых соединены с входами слагаемых устройства, а вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с входами знаков слагаемых устройства, выход второго эле5 мента И соединен с адресным входом вто-. рой группы постоянного запоминающего блока, первый вход второго элемента И соединен с выходом элемента ИЛИ, первый вход которого соединен с входом признака

0 операции устройства, а второй вход элемента ИЛИ соединен с выходом сдвига первого регистра, информационные входы параллельной загрузки которого подключены к выходам постоянного запоминающего бло5 ка, вход синхронизации первого регистра соединен с вторым входом второго элемента И и первой шиной синхронизации устрой- ства, первый разрядный выход ассоциативного запоминающего блока сое- . динен с входом элемента НЕ, первым вхо-

дом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с входами разрешения работы элементов задержки второй группы, первым входом третьего элемента И, входом управления режимами работы первого регистра и с шиной управления устройства, вы-. ход второго элемента И-НЕ через элемент задержки соединен с вторым входом первого элемента И-НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к информационному входу сдвига второго регистра, выходы которого являются выходными шинами отрицательного результата устройства, выход элемента НЕ является последовательным выходом промежуточного результата сложения и подключей к информационному входу сдвига третьего регистра, выходы которого являются выходными шинами положительного результата устройства и выходом знака результата сложения, выход третьего элемента И соединен с вторыми входами первого элемента И, элементов И первой и третьей групп и входами синхронизации второго и третьего регистров, второй вход третьего элемента И подключен к второй

шине синхронизации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Ассоциативное суммирующее устройство | 1983 |

|

SU1174920A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

Суммирующее устройство может быть использовано в устройствах цифровой обработки массивов данных. Устройство алгебраического сложения содержит постоянный запоминающий блок, ассоциативный запоминающий блок, первый элемент И, первую, вторую и третью группы элементов И, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента И, три регистра, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И-НЕ, элемент задержки и элемент НЕ 2 ил. 1 табл.

Примечание. Х- любое состояние

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-04-07—Публикация

1991-02-07—Подача