таны блоки адресации, управления памятью для организации передачи данных между ОП и буферной памятью - блоки анализа запросов, формирования циклов, сдвигате- лей, определения сдвига, формирования маски.

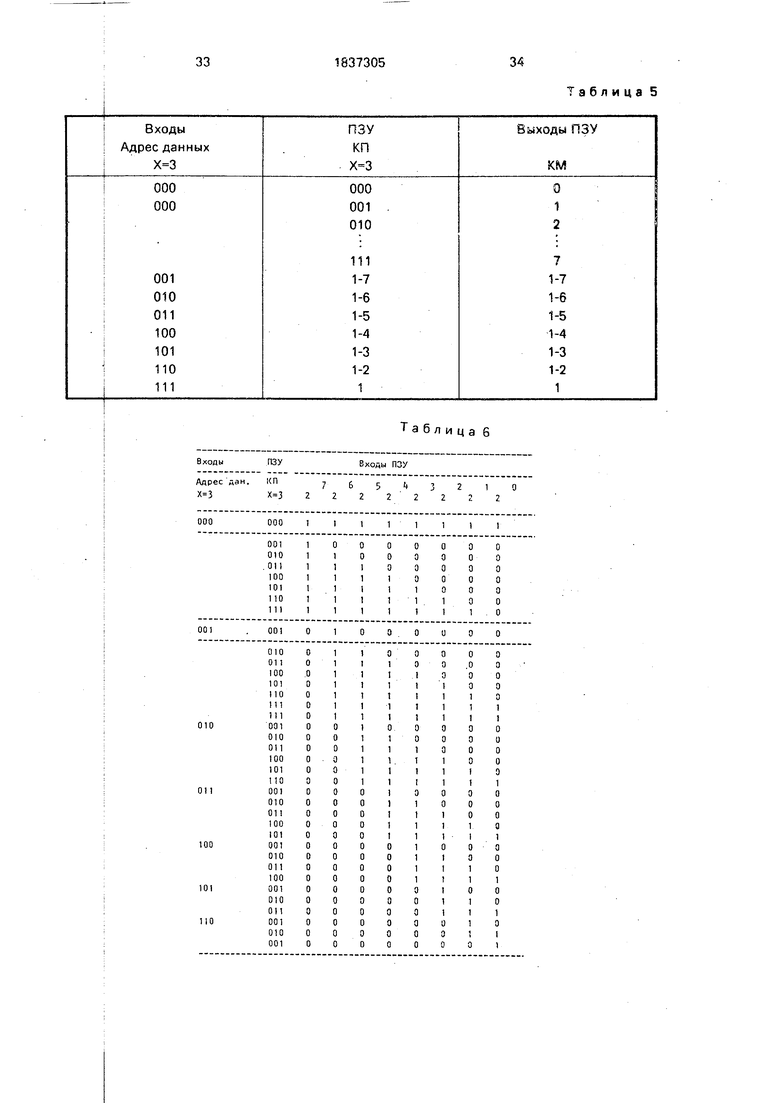

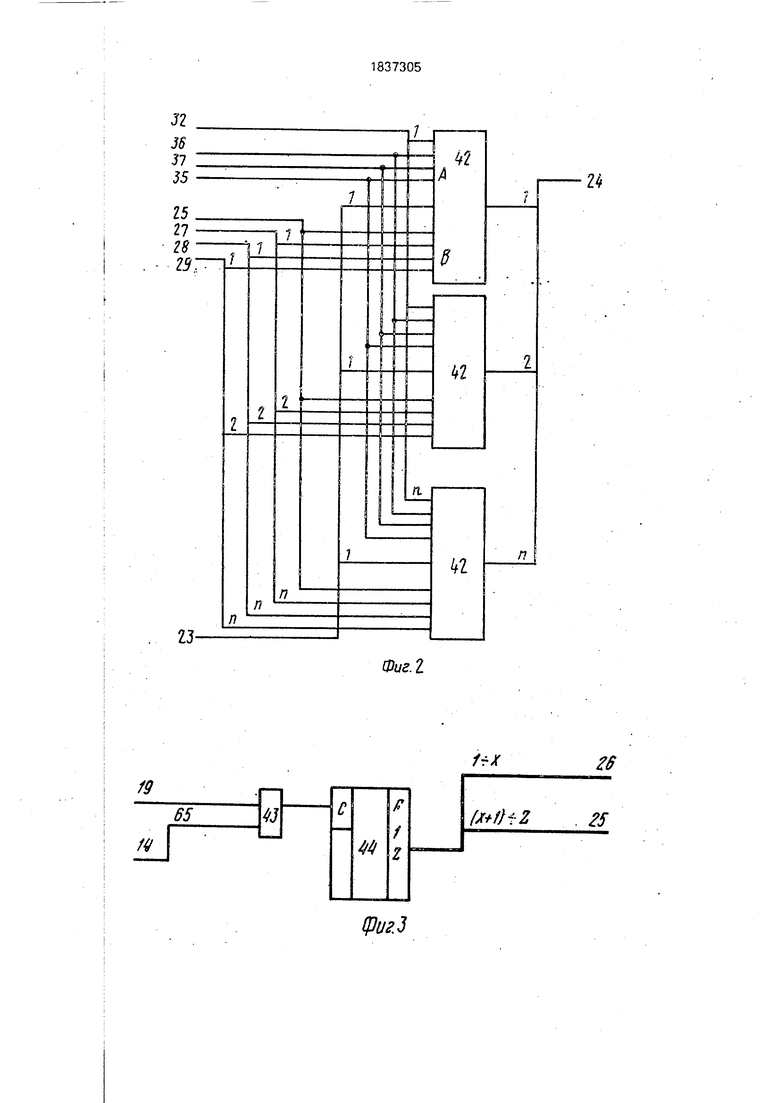

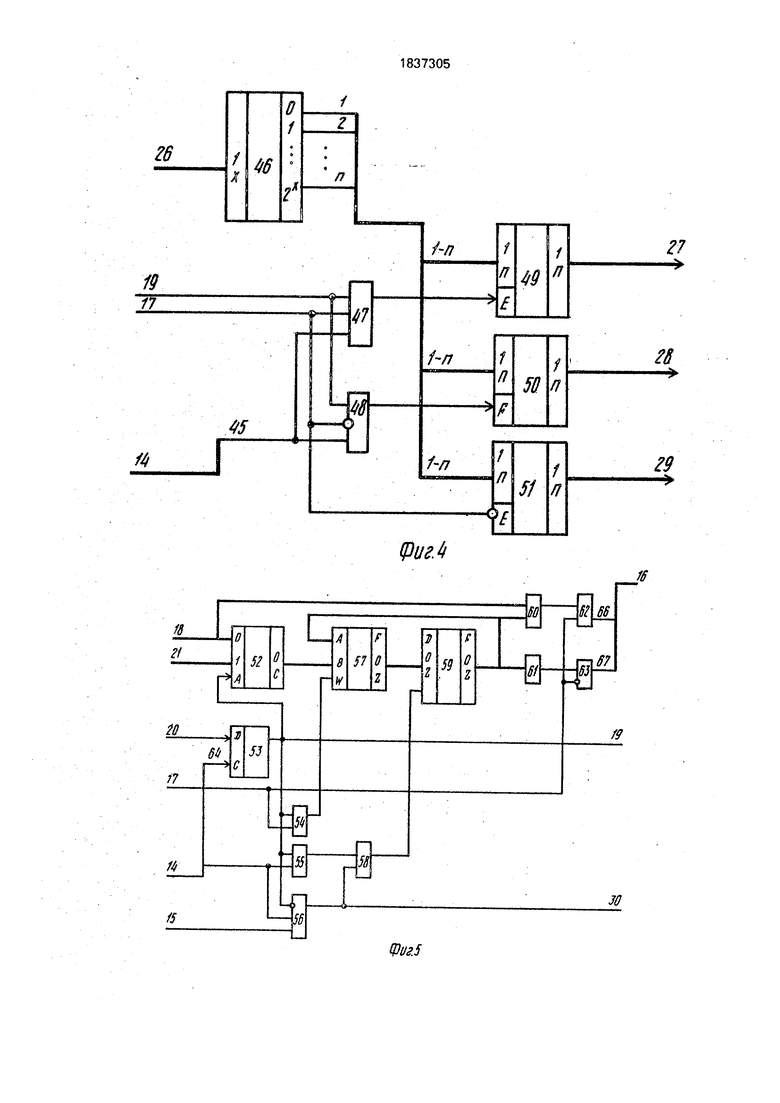

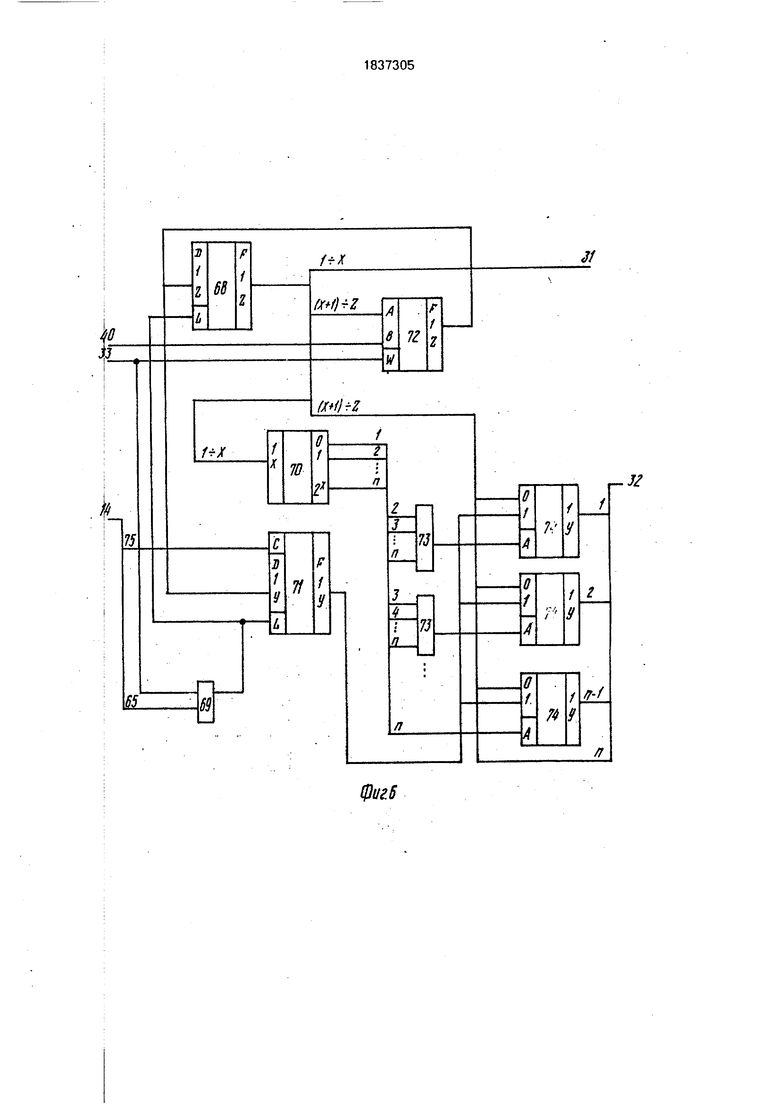

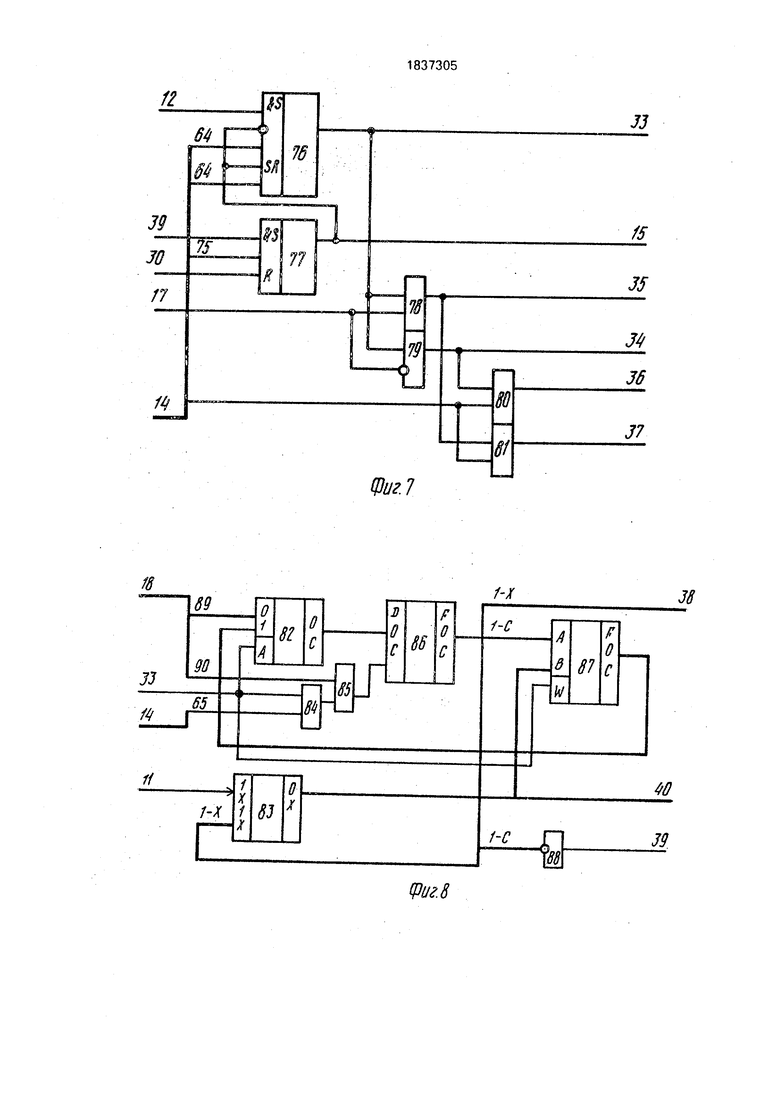

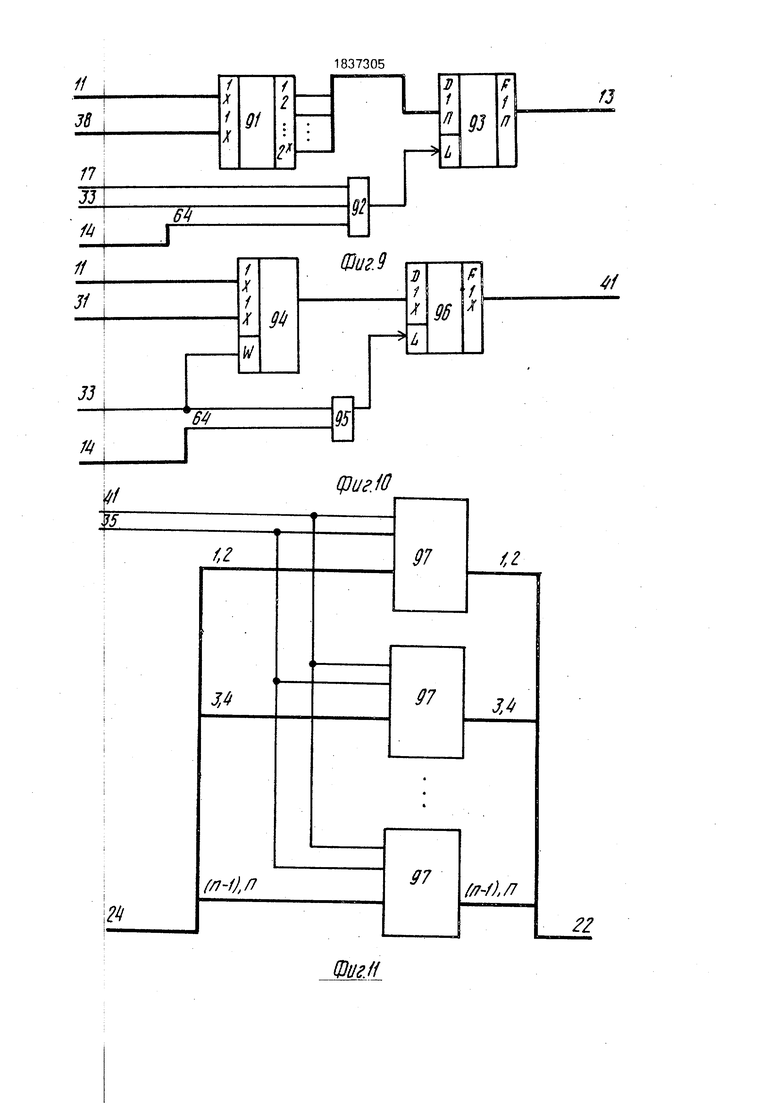

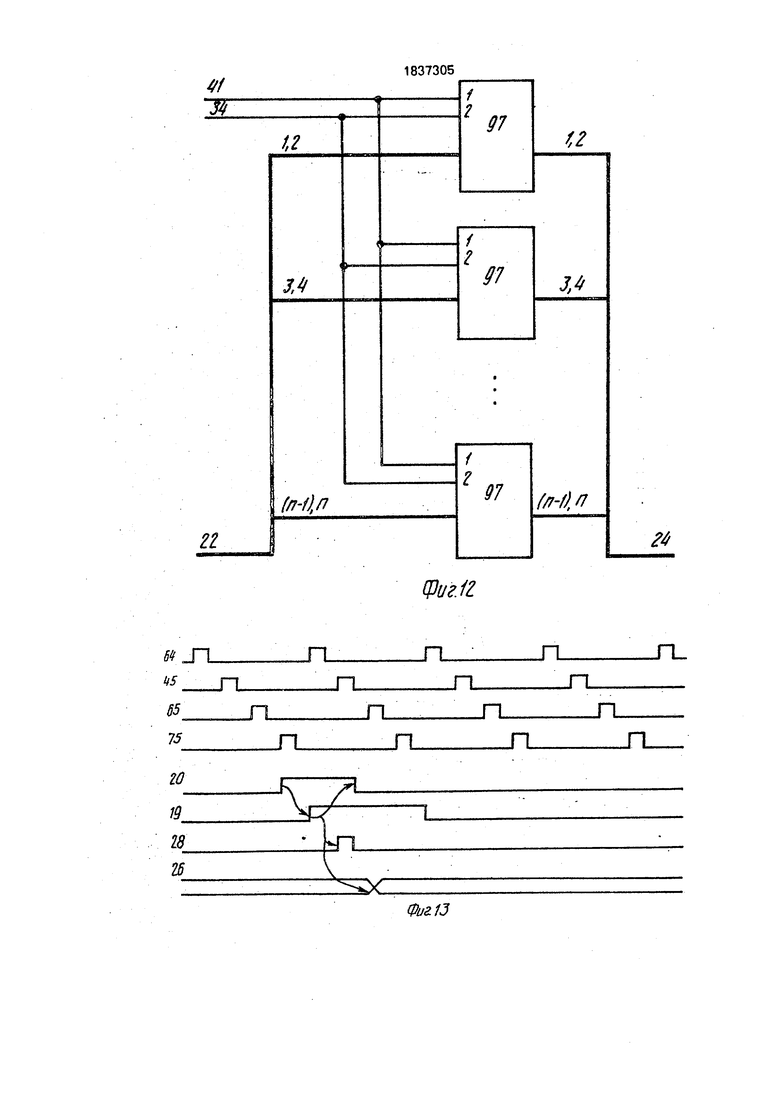

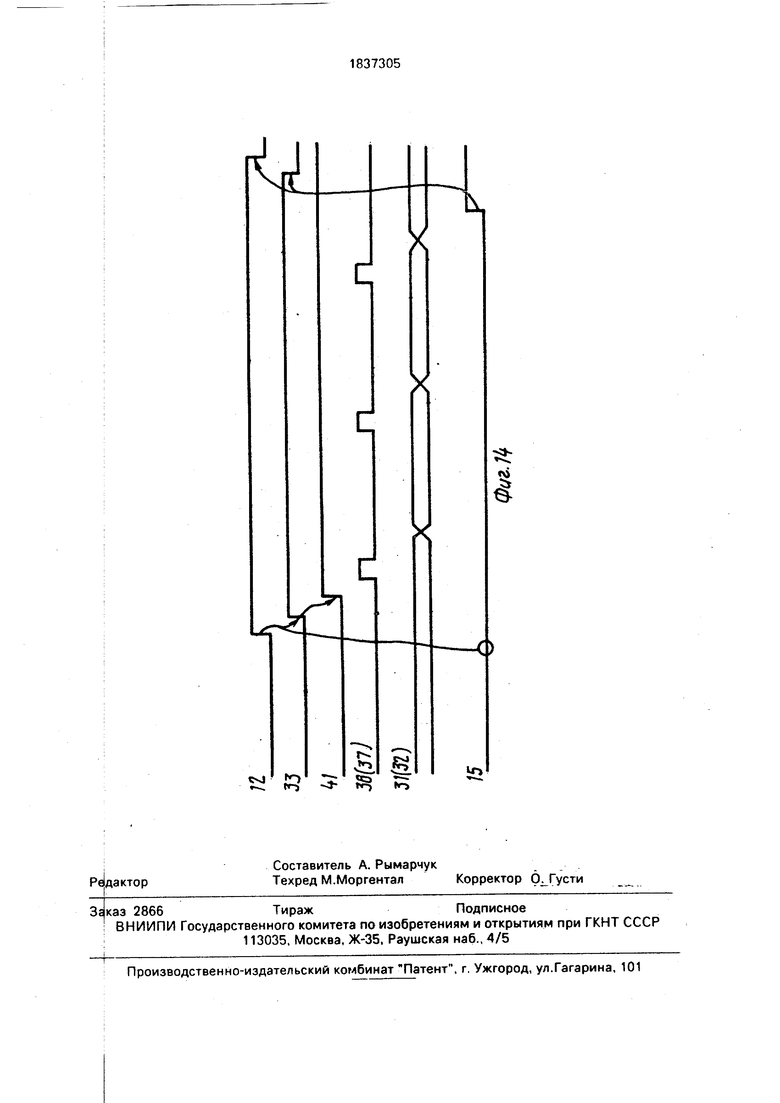

На фиг.1 представлена блок-схема устройства для обмена данными между оперативной памятью и периферийными устройствами; на фиг.2 - блок памяти; на фиг.З - первый блок адресации; на фиг.4 первый блок управления памятью; на фиг.5 - блок анализа запросов; на фиг.6 - второй блок адресации; на фиг.7 - второй блок управления памятью; на фиг.8 - блок форми- рования циклов; на фиг.9 - блок формирования маски; на фиг.10 - блок определения сдвига; на фиг.11 - первый сдви- гатель; на фиг. 12 - второй сдвигатель; на фиг.13 - временная диаграмма обмена дан- ными между блоком памяти и периферийными устройствами; на фиг. 14 - временная диаграмма обмена данными между блоком памяти и оперативной памятью.

Устройство для обмена данными содер- жит блок 1 памяти, первый блок 2 адресации, первый блок 3 управления памятью, блок 4 анализа запросов, второй блок 5 адресации, второй блок б управления памятью, блок 7 формирования циклов, два сдвигателя 8, блок 9 формирования маски, блок 10 определения сдвига, группу адресных входов 11 устройства, вход 12 разрешения обмена устройства, выход 13 маски устройства, вход 14 синхронизации устрой- ства, выход 15 конца обмена устройства, выход 16 запроса на обмен устройства, вход 17 задания направления обмена, вход 18 константы передачи устройства, вход 17 за- дани направлени обмена, вход 18 констан- ты передачи устройства, выход 19 ответа устройства, вход 20 запроса на обмен устройства, вход 21 задания кода единицы устройства, первую 22 шину данных устройства для соединения с оперативной памятью, вторую 23 шину данных устройства дл соединени с периферийными устройствами, первую 24 группу информационных входов-выходов блока памяти, первый адресный вход 25 блока памяти, вход 26 номе- ра байта первого блока управления памятью, первую группу управляющих входов 27, 28, 29 блока памяти, вход 30 сброса второго блока управления памятью, вход 31 номера байта блока определения сдвига, второй адресный вход 32 блока памяти, второй выход 33 второго блока управления памятью, управляющий вход 34 второго сдвигателя, вторую группу управляющих входов 35, 36, 37 блока памяти, третий управляющий вход 38 блока формирования маски, вход 39 конца цикла второго блока управления памятью, вход 40 константы модификации второго блока адресации, выход 41 блока определени сдвига.

Группа 11 адресных входов устройства соединена с адресными входами блока 7 формирования циклов, блока 9 формирования маски и блока 10 определения сдвига. Вход 12 разрешения обмена устройства соединен с одноименным входом второго блока 6 управления памятью. Выход 13 маски устройства является выходом блока 9 формирования маски. Вход 14 синхронизации устройства соединен с первым входом блока 4 анализа запросов, с синхровходами блока 9 формирования масок, блока 10 определения сдвига, первого 3 и второго 6 блоков управления памятью, блока 7 формирования циклов, первого 2 и второго 5 блоков адресации.

Третий выход второго блока 6 управления памятью соединен с четвертым управляющим входом блока 4 анализа запросов и является выходом 15 конца обмена устройства. Первый выход блока 4 анализа запросов является выходом 16 запроса на обмен устройства.

Вход 17 задания направления обмена соединен с первыми управляющими входами блока 9 формирования маски, первого 3 и второго 6 блоков управления памятью и блока 4 анализа запросов.

Вход 18 константы передачи устройства соединен с вторыми управляющими входами блока 7 формирования циклов и блока 4 анализа запросов. Второй выход блока 4 анализа запросов соединен с входами разрешения первого блока 2 адресации и первого блока 3 управления памятью и является выходом 19 ответа устройства.

Второй вход блока 4 анализа запросов является входом 20 запроса на обмен устройства, а третий управляющий вход соединен с входом 21 задания кода единицы устройства.

Первая 22 шина данных устройства для соединения с оперативной памятью соединена с выходом первого сдвигателя и с информационным входом второго сдвигателя и является системной магистралью.

Вторая 23 шина данных устройства для соединения с периферийными устройствами соединена с второй группой информационных входов-выходов блока 1 памяти и является канальной магистралью.

Первая группа 24 информационных входов-выходов блока 1 памяти соединена с информационным входом первого сдвигате- ля и с выходом второго сдвигателя и образут двунаправленные шины буферной маги- :трали.

Первый 25 и второй 32 адресные входы элокэ 1 памяти соединены соответственно ; первыми выходами первого 2 и второго 5 элоков адресации и являются соответст- teHHO шинами адреса строки порта В и пор- аА.

Первая группа выходов 27,28,29 перво- о блока 3 управления памятью соединена оответственно с первой группой управля- щих входов блока 1 памяти и являются оответственно шинами записи, чтения и разрешения выходов порта В.

. Вход 30 сброса второго блока 6 управ- |ления памятью соединен с третьим выходом блока 4 анализа запросов.

Вход 31 номера байта блока определения сдвига и вход 26 номера байта первого блока управления памятью соединены соответственно с вторыми выходами второго 5 и первого 2 блоков адресации и являются соответственно шинами номера байта в строке порта А и порта В.

Второй выход 33 второго блока 6 управления памятью соединен с управляющими входами второго блока 5 адресации и блока 10 определения сдвига, вторым управляющим входом блока 9 формирования масок и первым управляющим входом блока 7 формирования циклов и является выходом триггера связи с оперативной памятью.

Первый выход 34 второго блока 6 управ- |ления памятью соединен с управляющим входом второго сдвигателя 8 и является выходом разрешения сдвига.

Группа выходов 35,36,37 второго блока 6 управления памятью соединена соответственно с второй группой управляющих входов блока 1 памяти, а выход 35 разрешения выдачи группы выходов соединен также с управляющим входом первого сдвигателя 8 и является сигналом разрешения выходов порта А, выходы 36, 37 являются соответственно стробами записи и чтения порта А.

Третий выход 38 блока 7 формирования циклов соединен с третьим управляющим входом блока 9 формирования маски и является группой выходов X младших разрядов регистра константы передачи.

Вход 39 конца цикла второго блока 6 управления памятью соединен с вторым выходом блока 7 формирования циклов, который является выходом равенства нулю константы передачи.

Вход 40 константы модификации второго блока 5 адресации соединен с первым выходом блока 7 формирования циклов. Выход 41 блока 10 определения сдвига соединен с входами величины сдвига первого и второго сдвигателей 8 и является группой выходов регистра сдвига.

Блок 1 памяти (фиг.2) предназначен для

временного хранения байтов данных, поступающих в него по двунаправленным шинам канальной 23 и буферной 24 магистралям. Он содержит п узлов 42 двухвходовой двухадресной памяти с портами А и В, которая

0 реализована на микросхеме К1800РП6 (зарубежный аналог НС1Р806).

Двунаправленные шикы 23 канальной магистрали соединены с входами-выходами портов В п узлов 42.

5 Двунаправленные шины 24 буферной магистрали соединены с входами-выходами портов А п узлов 42.

Первый 25 и второй 32 адресные входы, первая группа 27, 28, 29 управляющих вхо0 дов и вторая группа 36, 37, 35 управляющих входов блока соединены с соответствующими входами п узлов 42.

Первый блок 2 адресации (фиг.З) предназначен для адресации ячеек двухадресно5 го лока 1 памяти по порту В.

Он содержит элемент 43 И и счетчик 44 номера байта порта В. Выходы X младших разрядов и Y оставшихся разрядов счетчика 44 номера байта порта В соединены соот0 ветственно с шинами 26 номера байта в строке порта Вис шинами 25 адреса строки порта В. Вход счетчика 44 соединен с выходом элемента 43 И. Первый и второй входы элемента 43 И соединены соответственно с

5 входом разрешения 19 блока и с линией 65 синхровхода 14 блока.

Первый блок 3 управления памятью (фиг.4) предназначен для выработки управляющих сигналов записи и чтения байтов

0 данных для порта В блока 1 памяти. Он содержит дешифратор 46, первый 47 и второй 48 элементы И, первый 49, второй 50 и третий 51 селекторы. Выходы первого 49, второго 50 и третьего 51 селекторов соеди5 нены соответственно с шинами 27 записи порта В, с шинами 28 чтения порта Вис шинами 29 разрешения выходов порта В. Вход дешифратора 46 соединен с входом 26 номера байта блока, а выходы дешиф0 ратора 46 соединены с первыми входами первого 49, второго 50 и третьего 51 селекторов. Вход 19 разрешения блока соединен с первыми входами первого 47 и второго 48 элементов И, а выходы этих эле5 ментов И соединены соответственно с вторыми входами первого 49 и второго 50 селекторов.

Первый управляющий вход 17 блока соединен с вторым входом первого 47 элемента И и с вторыми инверсными входами

второго 48 элемента И и третьего 51 селектора. Линия 45 синхровхода 14 блока соединена с третьими входами первого 47 и второго 48 элементов И.

Блок 4 анализа запросов (фиг.5) предна- начен для выработки запросов на обмен данными с оперативной памятью, а также для выработки сигнала обслуживания периферийного устройства и конца обмена данными с оперативной памятью. Он содержит мультиплексор 52, триггер 53 обслуживания периферийного устройства, схему 54 сложения по модулю два, первый 55, второй 56, третий 62, четвертый 63 и пятый 61 элементы И, арифметико-логическое устройство 57, элемент 58 ИЛИ, регистр 59 счетчика байтов, схему сравнения 60, сигнал 66 запроса на выдачу данных в оперативную память и сигнал 67 запроса на прием данных от оперативной памяти.

Второй управляющий вход 18 блока соединен с первыми входами мультиплексора 52 и схемы сравнения 60, второй вход которой соединен с первым входом арифметико-логического устройства 57, с выхо- дом регистра 59 и с входами пятого 61 элемента И, Выходы схемы сравнения 60 и пятого 61 элемента И соответственно соединены с первыми входами третьего 62 и четвертого 63 элементов И, выходы кото- рых соединены соответственно с линиями 66, 67 первого 16 выхода блока. Третий управляющий 21, второй 20 и четвертый управляющий 15 входы блока соединены соответственно с вторым входом мультиплек- сора 52, первым входом триггера 53 и третьим входом второго 56 элемента И, выход которого соединен с третьим 30 выходом блока и с вторым входом элемента 58 ИЛИ, второй вход которого соединен с вы- ходом первого 55 элемента И. а выход соединен с вторым входом регистра 59, первый вход которого соединен с выходом арифметико-логического устройства 57, второй и третий выходы которого соединены соот- ветственно с выходом мультиплексора 52 и выходом схемы 54 сложения по модулю два, первый вход которой соединен с первым входом первого 55 элемента И, с первым инверсным входом второго 56 элемента И, с третьим входом мультиплексора 52, с вы- ходм триггера 53 и с вторым 19 выходом блока. Линия 64 первого 14 входа блока соединена с вторым входом триггера 53, а линия 65 первого 14 входа блока соединена с вторыми входами первого 55 и второго 56 элементов И.

Первый управляющий 17 вход блока соединен с вторыми входами схемы 54 сложения по модулю два и третьего 63 элемента

И и с вторым инверсным входом четвертого 63 элемента И.

Второй блок 5 адресации (фиг.6) предназначен для адресации mxn ячеек nopta A блока 1 памяти. Он содержит регистр 68 номера байта порта А, схему 69 И, дешифратор 70, счетчик 71 номера строки, арифметико-логическое устройство 72, п-2 элементов 73 ИЛИ и п-1 мультиплексоров 74.

Выходы п-1 мультиплексоров 74 соединены с первым 32 выходом .блока, синхров- ход 14 которого соединен с первым входом счетчика 71 и вторым входом элемента 69 И, выход которого соединен с третьим входом счетчика 71 и вторым входом регистра 68, выход которого соединен с первым 32 и вторым 31 выходами блока, с первыми входами п-1 мультиплексоров 74, с первым входом арифметико-логического блока 72 и с входом дешифратора 70, выходы которого соединены с третьим входом (п-1)-го мультиплексора 74 и с входами п-2 элементов 73 ИЛИ, выходы которых соединены соответственно с третьими входами п-2 мультиплексоров 74, вторые входы мультиплексоров 74 соединены с выходом счетчика 71, второй вход которого соединен с вторым входом регистра 68 и с выходом арифметико-логического устройства 72, второй вход которого соединен с входом 40 константы модификации блока, а управляющий вход 33 блока соединен с третьим входом арифметико-логического устройства 72 и с первым входом элемента 69 И.

Второй блок 6 управления памятью (фиг.7) предназначен для выработки управляющих сигналов записи, чтения, разрешения выходов для порта А блока 1 памяти на время цикла связи с ОП, а также для определения длительности связи с ОП.

Он содержит триггер 76 связи с ОП (ТСОП), триггер 77 равенства нулю константы передачи (ТКПДО), первый 78, второй 79, третий 80 и четвертый 81 элементы И. Выходы третьего 80 и четвертого 81 элементов И соединены соответственно с 36 и 37 выходами блока, а вторые входы элементов 80, 81 И соединены с линией 45 синхровхода 14 блока, линия 64 которого соединена с третьим и пятым входами триггера 76 ТСОП, а линия 75 соединена с вторым входом триггера 77 ТКПДО.о

Выход триггера 76 ТСОП соединен с первыми входами первого 78 и второго 79 элементов И и с вторым 33 выходом блока. Выход триггера 77 ТКПДО соединен с вторым инверсным и четвертым входами триггера 76 ТСОП и с третьим 15 выходом блока, вход 12 разрешения обмена устройства которого соединен с первым входом триггера 76 ТСОП.

Вход 39 конца цикла и вход 30 сброса блока соединены соответственно с первым и третьим входами триггера 77 ТКПДО, а первый управляющий вход 17 блока соединен с вторым входом первого 78 элемента И и с вторым инверсным входом второго 79 элемента И, выход которого соединен с первым входом третьего элемента И и с первым 34 выходом блока, выход 35 разрешения выдачи группы выходов которого соединен с выходом первого 78 элемента И и с первым входом четвертого 81 элемента И.

Блок 7 формирования циклов (фиг.8) предназначен для модификации константы передачи и выработки сигнала равенства нулю константы передачи, а также для формирования константы модификации.

Он содержит мультиплексор 82, постоянное запоминающее устройство ПЗУ 83, первый 84 элемент И, элемент ИЛИ 85, регистр 86 константы,передачи (РКПД) арифметико-логическое устройство (АЛУ) 87 и второй 88 элемент И.

Первый вход мультиплексора 82 соединен с линией 89 второго управляющего 18 входа блока, линия 90 которого соединена с первым входом элемента 85 ИЛИ, второй вход которого соединен с выходом первого 84 элемента И, второй вход которого соединен с линией 65 синхровхода 14 блока, а первый вход соединен с третьим входом АЛУ 87, первым управляющим входом 33 блока и с третьим входом мультиплексора 82. Второй вход мультиплексора 82 соединен с выходом АЛУ 87, а выход соединен с первым входом регистра 86, второй вход которого соединен с выходом элемента 85 ИЛИ. Выход регистра 86 соединен с третьим 38 выходом блока, с первым входом АЛУ 87, с вторым входом ПЗУ 83 и с инверсным входом второго 88 элемента И, выход которого соединен с вторым 39 выходом блока.

Адресный 11 вход блока соединен с первым входом ПЗУ 83, выход которого соединен с вторым входом АЛУ 87 и с первым 40 выходом блока.

Блок 9 формирования маски (фиг.9) предназначен для формирования маски обменного слова ОП.

Он содержит постоянное запоминающее устройство 91, элемент 92 И и регистр 93 маски.

Первый и второй входы ПЗУ 91 соединены соответственно с адресным 11 и третьим управляющим 38 входами блока. Выходы ПЗУ 91 соединены с первым входом регистра 93, выход которого соединен с выходом 13 блока, а второй вход соединен с выходом элемента 92 И, первый и второй входы которого соединены соответственно с первым

17 и вторым 33 управляющими входами блока, а третий вход элемента 92 И соединен с линией 64 синхровхода 14 блока.

Блок 10 определения сдвига (фиг. 10) предназначен для формирования величи0 ны сдвига для первого и второго сдвигате- лей.

Он содержит арифметико-логическое устройство 94, элемент 95 И и регистр 96 сдвига.

5Первый и второй входы АЛУ 94 соединены соответственно с адресным 11 и номера байта 31 входами блока. Управляющий 33 вход блока соединен с первым входом элемента 95 и с третьим входом АЛУ 94. выход

0 которого соединен с первым входом регистра 96, выход которого соединен с выходом 41 блока. Второй вход регистра 96 соединен с выходом элемента 95 И, второй вход которого соединен с линией 64 синхровхода 14

5 блока.

Первый сдвигатель 8 (фиг. 11) предназначен для правильного расположения байтов обменного слова, выдаваемого а ОП. Он содержит п/2 узлов 97 комбинационного

0 сдвигателя, который реализован на микросхеме К 1800 РВ8.

Информационные входы узлов 97 соединены с двунаправленными шинами 24 буферной магистрали, а информационные

5 выходы узлов 97 соединены с двунаправленными шинами 22 системной магистрали.

Первые входы управления сдвигов узлов 97 соединены с входом 41 величины

0 сдвига блока, а вторые входы управления видом сдвига узлов 97 соединены с управляющим 35 входом блока.

Второй сдвигатель 8 (фиг.12) предназначен для правильного расположения

5 байтов обменного слова, принимаемого из ОП.

Он содержит п/2 узлов 97 комбинационного сдвигателя, реализованного на микросхеме К 1800 ВР8.

0 Информационные входы узлов 97 соединены с двунаправленными шинами 22 системной магистрали, а информационные выходы узлов 97 соединены с двунаправленными шинами 24 буферной магист5 рали.

Первые входы управления сдвигом узлов 97 соединены с входом 41 величины сдвига блока, а вторые входы управления видом сдвига узлов 97 соединены с управляющим входом 34 блока, устройство для обмена данными между оперативной памятью и периферийными устройствами работает следующим образом.

Оперативная память (ОП) и периферийное устройство (ПФУ), обменивающиеся информацией, используют для промежуточного хранения передаваемых данных блок 1 памяти (БП1).

БП1 представляет собой двухадресную двухпортовую память емкостью mxn байтов (где m - количество строк, an- количество байтов в строке), позволяющую вести одновременно обмен данными между БП1 и ОП по порту А и между БП1 иПФУпо порту В.

Ширина БП1 выбрана равной ширине обменного слова ОП, т.е. формат обмена с ОП равен п байтам.

БП1 содержит п узлов 42. Каждый узел представляет собой двухадресную двухпортовую память емкостью плх1 байт.

Двунаправленные входы-выходы портов А п узлов 42 образуют п-байтовую двунаправленную шину 24 буферной магистрали, которая используется для параллельной записи-чтения п байтов данных при обмене между ОП и БП1.

Двунаправленные входы-выходы портов В п узлов 42 объединены и образуют однобайтовую двунаправленную шину 23 канальной магистрали, которая используется для последовательной записи-чтения байтов данных при обмене между ПФУ и

БП1.

При обмене данными с ПФУ блок 1 памяти всегда заполняется сначала независимо от начального адреса данных ОП.

Обмен данными с ПФУ начинается по сигналу, поступающему на вход 20 запроса на обмен устройства. В ответ на запрос в блоке 4 анализа запросов вырабатывается единичный сигнал на выходе 19 ответа устройства, который разрешает работу первого блока 3 управления памятью и первого блока 2 адресации (см. временную диаграмму фиг.13).

Первый блок 2 адресации выдает в БП1 адрес одной из m строк по шинам 25 адреса строки порта В, а в первый блок 3 управления памятью номер байта в строке по шинам 26. По этому номеру первый блок 3 управления памятью выдает на шине 27 записи порта В в блок 1 памяти один из п стробов записи, если выполняется операция ввода, или один из п чтения на шины 28 чтения порта В и один из п сигналов разрешения выходов на шины 29 разрешения выходов порта В, если выполняется операция вывода.

Какая операция выполняется, определяет сигнал задания направления обмена на входе 17 устройства. Единичный уровень этого сигнала задает операцию ввода, а нулевой - вывода.

После приема или выдачи байта данных в первом блоке 2 адресации увеличивается на единицу номер байта порта В, а в блоке 4 анализа запросов увеличивается при вво0 де или уменьшается при выводе количество принятых или выданных байтов на константу равную единице, поступающую с входа 21 устройства.

Блок 4 анализа запросов сравнивает

5 количество принимаемых при вводе или выдаваемых при выводе байтов данных с количеством байтов, которым необходимо обменяться с ОП за один цикл связи. Это количество задается величиной константы

0 передачи, поступающей на вход 18 устройства.

Если при вводе в БП1 накопилось нужное количество байтов, а при выводе есть куда принять нужное количество байтов,

5 блок 4 анализа запросов вырабатывает на выходе 16 запрос на обмен с ОП.

Обмен данными между БП1 и ОП может происходить начиная с адреса данных ОП кратному обменному слову ОП, т.е. количе0 ство младших разрядов адреса данных равное Iog2n равно нул,ю., ,

В этом случае порядок расположения байтов данных вПБ1 соответствует порядку расположения данных в ОП, т.е. каждая из

5 m строк БП1 является обменным словом для ОП.

Если же адрес данных не кратен обменному сдову - количество младших разрядов равное logzn не равны нулю, то в первом

0 цикле связи с ОП будет передано в ОП байтов меньше п и расположены они дожны быть в зависимости от значения Iog2n младших разрядов адреса данных ОП.

В следующем цикле связи с ОП надо

5 передать в ОП полное обменное слово из п байтов, которое содержит оставшиеся байты текущей строки и часть байтов (дополнение до п)следующей строки и расположить их в нужном порядке.

0 Какие байты адресовать в текущей строке, а какие е следующей, определяются по количеству переданных байтов в первом обменном слове, т.е. по номеру байта в строке, который получился в результате модифика5 ции адреса номера байта порта А на количество переданных байтов в первом цикле связи.

Например, при п 8 анализируются при (Iog2 8 3) младшие разряды адреса данных ОП. Если они равны, например, пяти (101),

о в первом цикле связи с ОП надо будет предать три первые байта нулевой строки зП1 и расположить их с адреса равного пя- и. После передачи модифицированный ад- ес номера байта порта А будет равен 3 и в :ледующем цикле связи надо передать пять ютавшихся байтов нулевой строки и три 1ервые байта первой строки и расположить IXB нужном порядке. Следующее обменное ;лово будет состоять из пяти оставшихся бай- ов первой строки и трех первых байтов )торой строки и так далее.

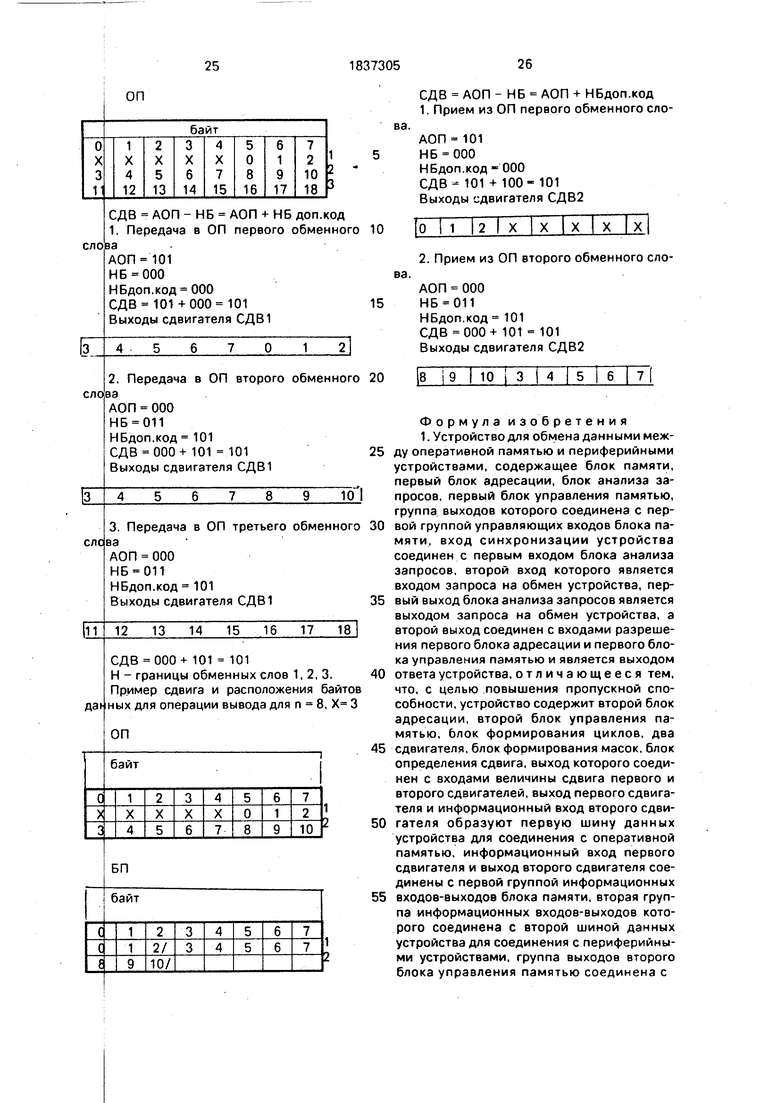

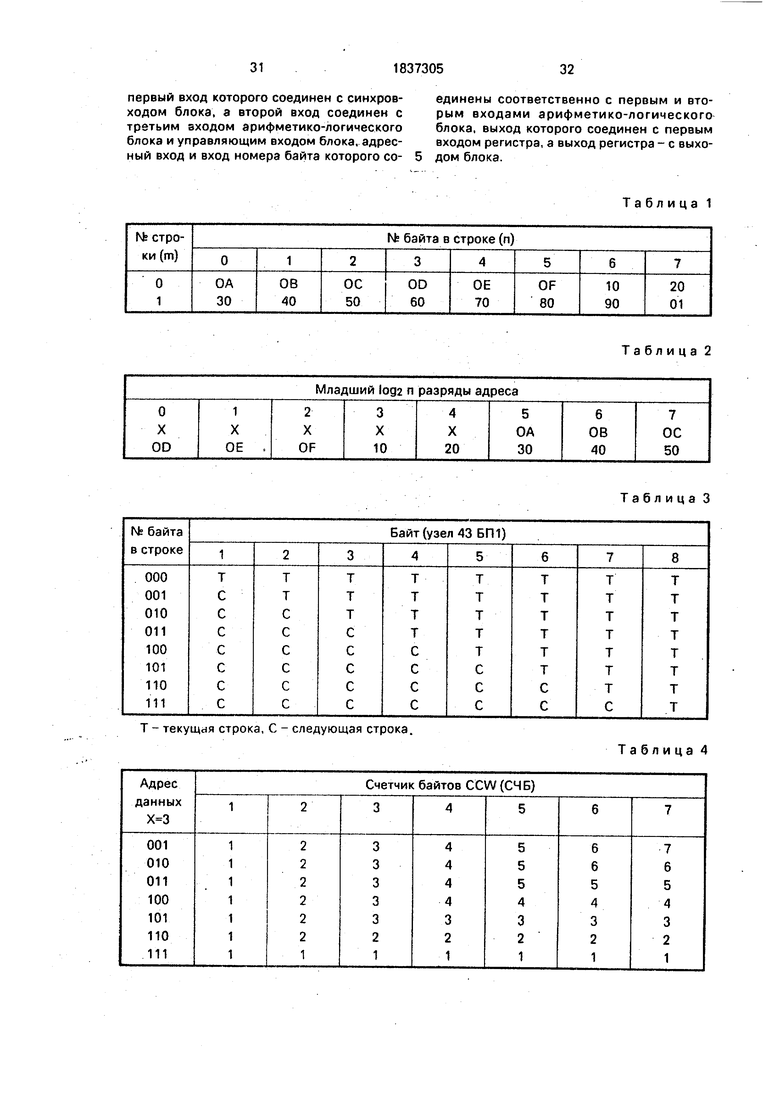

Расположение байтов данных в БП1 фиведено в табл.1.

Расположение байтов данных в ОП при- )едено в табл.2.

При приеме байтов из ОП, расположен- шх не по границе двойного слова, в первом 1икле связи будет принято количество бай- ов меньше п и расположены в БП1 они удут начиная с нулевого байта. В следую- цем цикле связи от ОП будет принято п айтов, часть из которых будет расположе- а в текущей строке БП1, а часть в следу- ощей.

Для расположения байтов в соответст- жи с адресом данных ОП применены одно- 1аправленные сдвигатели 8. Первый 1спользуется при выполнении операций шода, а второй при выполнении, операций ывода.

Каждый из сдвигателей содержит п/2 1злов 43. Каждый узел представляет собой 1вухбайтовый программируемый сдвига- ель, на входы величины сдвига которого юдается величина сдвига с группы выходов ;1 регистра сдвига блока .10 определения :двига, а на управляющие входы код операми сдвига. Для первого сдвигателя код опе- ации задается сигналом 35 разрешения шходов порта А, а для второг сдвигателя ;игналом 34 разрешения сдвига второго 5лока 6 управления памятью.

При отсутствии сигналов на выходах 34, 5 второго блока 6 управления памятью вы- соды соответствующих сдвигателей отклю- ены.

Таким образом, при выполнении опе- )ации ввода отключены выходы второго двигателя 8 от буферной магистрали 24, а 5ыходы первого сдвигателя открываются на ремя цикла обмена с ОП.

При выполнении операций вывода вы- юды первого сдвигателя 8 отключены от системной магистрали 22, а выходы второго :двигателя 8 открываются во время цикла :вязи с ОП.

Обмен данными с ОП начинается по сиг- 1алу разрешения обмена поступающему на зход 12 устройства. В ответ на разрешение

обмена во втором блоке 6 управления памятью вырабатывается единичный сигнал на выходе 33 триггера связи с оперативной памятью, который разрешает работу второго блока 5 адресации, второго блока 6 управления памятью, блока 7 формирования циклов, блока 9 формирования маски и блока 10 определения сдвига на время цикла связи с ОП (см. временную диаграмму

0 фиг. 14).

Второй блок 5 адресации проадресует одну из m строк, задав адрес текущей строки для каждого из п узлов 42 блока 1 памяти на шинах 32 адреса строки порта А, если обмен

5 ведется байтами, расположенными на границе обменного слова.

Если данные расположены не по границе обменного слова, то второй блок 5 адресации проадресует часть байтов (узлов 42)

0 текущей строкой, а часть байтов (узлов 42) следующей строкой, т.е. будет адресовано обменное слово, байты которого содержат- . ся в двух соседних строках.

Второй блок 5 адресации выдает также

5 по шинам 31 номер байта в строке порта А в блок 10 определения сдвига, по которому в зависимости от младших logan разрядов адреса данных, поступающих с входа 11 устройства, сформируется величина сдвига на

0 выходах 41 регистра сдвига блока 10 определения сдвига.

Второй блок 6 управления памятью при выполнении операций ввода вырабатывает строб 37 чтения порта А для всех п узлов 42

5 блока 1 памяти для параллельного чтения обменного слова, сигнал 35 разрешения выходов порта А БП1, который также задает код сдвига для первого сдвигателя и информация с выходов первого сдвигателя

0 будет выдана на шины 22 системной магистрали.

При выполнении операций вывода второй блок 6 управления памятью вырабатывает код сдвига на выходе 34 разрешения

5 сдвига для второго сдвигателя и обменное слово с шин 22 системной магистрали через второй сдвигатель поступит на шины 24 буферной магистрали для записи по порту А БП1 по стробу 36 записи порта А, который

0 вырабатывает второй блок 6 управления памятью.

После приема-выдачи обменного слова модифицируется номер байта порта А во втором блоке 5 адоесации на количество ч

5 переданных байтов в сторону увеличения. В блоке 4 анализа запросов модифицируется количество байтов устройства в сторону уменьшения при вводе и в сторону увеличения при выводе также на величину переданных байтов.

С целью увеличения пропускной способности устройства после выравнивания данных по границе обменного слова обмен данных ведется несколькими обменными словами, т.е. блоками данных.

Величина блока задается константой передачи на входе 18 устройства и может быть равной k,n, где k - количество строк (k m) передаваемых за один цикл связи с ОП.

Длительность цикла связи с ОП в зави- симости от величины константы передачи определяет блок 7 формирования циклов.

По мере передачи-приема обменных слов константа передачи модифицируется на величину константы модификации в сто- рону уменьшения. Величина константы модификации равна количеству байтов обменного слова и выдается на выход 4U блока 7 формирования циклов для модификации номера байта порта А по мере при- ема-выдачи обменных слов в сторону увеличения. Когда обмен блоком кончится, блок 7 формирования циклов вырабатывает на выходе 39 сигнал равенства нулю константы передачи по которому второй блок б управления памятью выдает на выход 15 устройства сигнал конца обмена с ОП и вырабатывает нулевой уровень на выходе 33 триггера связи с ОП, который прекращает работу всех блоков по обслуживанию порта А.

Сигнал конца обмена с ОП будет присутствовать на выходе 15 устройства до тех пор пока не промодифицируется количество байтов в устройстве в блоке 4 анализа за- просов на величину константы передачи при вводе в сторону уменьшения, а при выводе в сторону увеличения. После модификации блок 4 анализа запросов на выходе 30 формирует сигнал, по которому второй блок 6 управления памятью сбрасывает на выходе 15 устройства сигнал конца обмена с ОП. Устройство готово для следующего цикла связи с ОП.

Блок 1 памяти (фиг.2) работает следую- щим образом.

При выполнении операций ввода сигнал на входе 17 задания направления обмена устройства задает направление обмена от ПФУ в ОП, т.к. канальная магистраль 23 будет входной, а буферная магистраль 24 выходной.

Байт данных, поступающий от ПФУ по канальной магистрали 23 присутствует на входах-выходах порта В каждого из узлов 42 БП1. Шины 25 адреса строки порта В проадресуют нулевую строку во всех узлах 42, а на шинах 27 записи порта В вырабатывается один строб записи в первый узел 42 БП1.

При поступлении следующего байта данных от ПФУ вырабатывается строб записи во второй узел 42 БП1 и . до заполнения нулевой строки п байтами, а затем проадресуется первая строка и заполнится п байтами. Аналогичным образом будут заполняться следующие строки БП1.

По порту А читается обменное слово для. О.П по стробу 37 чтения порта А, поступающему во все узлы 42. Обменное слово-может состоять из байтов одной строки или двух соседних строк, в зависимости от адреса, который задается индивидуально для каждого узла 42 на шинах 32 адреса строки порта А.

Проадресованное и прочитанное обменное слово выдается на шины 24 буферной магистрали по сигналу 35 разрешения выходов порта А, общему для всех узлов 42 БП1.

Первый блок 2 адресации (фиг.З) работает следующим образом:

Для адресации количества nxm байтов БП1 по порту В используется счетчик 44 номера байта порта В. Количество разрядов счетчика определяется по формуле:

2 Iog2(nxm) logzn + logam X +.Y. где X - количество младших разрядов счетчика, адресующих п байтов в строке, Y - количество оставшихся разряду, адресующих m строк.

Младшие разряды 1-Х образуют шину 26 номера байта в строке порта В, Следующие Y разрядов (X + 1)-Z образуют шины 25 адреса строки порта В.

Каждый раз во время обслуживания ПФУ, т.е. при наличии единичного сигнала на выходе 19 ответа устройства после приема-передачи байта данных содержимое счетчика 44 увеличивается на +1 по синхросигналу 65 входа 14 синхронизации. Сигнал модификации вырабатывается на выходе элемента 43 И.

Первый блок 3 управления памятью (фиг.4) работает следующим образом:

Во время обслуживания ПФУ при обмене байтом данных по порту В блока 1 памяти срабатывает либо первый 49, либо второй 50 и третий 51 селекторы в зависимости от кода выполняемой операции.

Код выполняемойеоперации определяет сигнал на входе 17 задания направления обмена.

Единичный уровень этого сигнала определяет операцию ввода, а нулевой - вывода.

О том, что идет обмен байтом данных между ПФУ и портом В БП1 говорит единичный уровень сигнала на входе 19 блока.

При выполнении операций ввода по синхросигналу 45 входа 14 синхронизации на выходе первого 47 элемента И вырабатывается строб разрешения для первого 49 селектора, разрешая выдачу одного из п стробов на шины 27 для записи поступившего от ПФУ байта данных по порту В блока 1 памяти.

Второй 50 и третий 51 селекторы при этом не работают, так как на их входах разрешения нулевые уровни.

При выполнении операций вывода каждый раз при выдаче байта данных в ПФУ по синхросигналу 45 входа 14 срабатывает второй 48 элемент И, разрешая работу второго I 50 селектора, с выхода которого выдается | один из п стробов в шины 28 чтения порта | В. С выхода третьего 51 селектора выдается | один из п сигналов в шины 29 разрешения I выходов порта В для выдачи прочитанного по порту В БП1 байта данных в канальную | магистраль 23.

Какой из п стробов будет выдан на вы- I ход каждого из селекторов, определяет де- I шифратор 46 по номеру байта в строке порта В, поступающему по шинам 26 на | вход дешифратора 46, | Блок 4 анализа запросов (фиг.5) работа- ет следующим образом. | При желаний ПФУ обменяться байтом данных на вход 20 блока поступает сигнал | запроса ПФУ, при наличии которого по син- I хросйгналу 64 входа 14 устанавливается в I единичное состояние триггер 53 обслужи- | вания ПФУ (ТОПФУ), на фоне которого | происходит обмен байтом данных между | ПФУ и портом В блока 1 памяти. В ответ I на установленный триггер 53 ПФУ сбрасы- I вает сигнал запроса на входе 20 блока, вы- зывая в свою очередь сброс триггера 53

ТОПФУ.

Для подсчета и хранения количества | байтов данных содержащихся в блоке 1 па- I мяти при обмене данными между ПФУ и ОП используются арифметико-логическое уст- ройство 57 и регистр 59 счетчика байтов. | При обмене данными между ПФУ и пор- I том В БП1 содержимое регистра 59 модифи- | цируется на константу равную единице, | поступающую на вход 21 блока, а при об- I мене данными между ОП и портом А содер- (жимое регистра 59 модифицируется на I величину константы передачи, поступаю- | щую на вход 18 блока. Обе константы поступают на вход арифметико-логического устройства 57 через мультиплексор 52. вы- |бором направления которого управляет триггер 53 ТОПФУ. При установленном в единичное состояние триггере 53 выбирается первое направление мультиплексора

и на вход АЛУ 57 подается единичная константа.

При сброшенном триггере 53 выбирается нулевое направление мультиплексора и

на вход АЛУ 57 подается константа передачи,

Режим работы АЛУ 57 определяет схема 54 сложения по.модулю два в зависимости от состояния триггера 53 и кода выполняе0 мой операции, который определяется сигналом на входе 17 задания направления обмена.

Нулевой уровень сигнала на выходе схемы 54 сложения по модулю два задает

5 режим сложения, а единичный - режим вычитания.

При обмене байтом данных с ПФУ при выполнении операции ввода (единичный сигнал на входе 17 блока) на выходе схемы

0 54 сложения по модулю два нулевой уровень, задающий режим сложения для АЛУ 57, а при выполнении операций вывода на выходе схемы 54 единичный уровень задающий режим вычитания.

5Результат модификации на ±1 с выхода

АЛУ 57 заносится по синхросигналу 65 с выхода первой 55 схемы И.

При обмене данными с ОП модификация регистра 59 происходит при сброшен0 ном триггере 53 ТОПФУ. При выполнении операций ввода на выходе схемы 54 сложения по модулю два единичный уровень задающий режим вычитания, и при выводе - нулевой, задающий режим сложения для

5 АЛУ 57.

Результат модификации на +константу передачи заносится в регистр 59 с выхода второго 56 элемента И по синхросигналу 65 при сброшенном триггере 53 и при наличии

0 единичного сигнала конца обмена устройства с ОП на входе 15 блока.

Сигнал с выхода второго 56 элемента И поступает также на выход 30 блока для сброса сигнала конца обмена устройства с

5 ОП.

При выполнении операций ввода содержимое регистра 59 сравнивается первой 60 схемой сравнения с величиной константы передачи и если оно больше или равно кон0 станты передачи, то на выходе третьего 62 элемента И вырабатывается сигнал 66 запроса на выдачу данных в ОП, поступающий на выход 16 блока и говорящий о том, что в блоке 1 памяти накопилось достаточное ко5 личество байтов для передачи в ОП.

При выполнении операций вывода пятая 61 схема И выдает единичный сигнал по состоянию регистра 59 счетчика байтов, которое показывает, что незаполненный обь- ем БП1 больше максимально допустимого

блока обмена с ОП. По этому сигналу на выходе четвертой 63 схемы И вырабатывается сигнал 67 запроса на прием данных из ОП, поступающий на выход 16 блока и говорящий о том, что в блоке 1 памяти есть достаточно места на прием блока данных из ОП.

Второй блок 5 адресации (фиг.7) работает следующим образом:

Для адресации номера байта, начиная с которого будет вестись обмен с ОП по порту А блока 1 памяти используется регистр 68 номера байта порта А..

Количество разрядов регистра определяется по формуле:

Z loga(nxm) loQ2n + Iog2m X + Y, где X - количество младших разрядов, адресующих п байтов в строке;

Y - количество старших разрядов, адресующих m строк.

При обмене данными, расположенными по границе обменного слова, т.е. адрес данных ОП кратен п байтам, каждая строка БП1 является обменным словом для ОП, т.е. адрес для каждого из п байтов (узлов 43 блока 1 памяти) определяется Y старшими разрядами регистра 68 и равен номеру текущей строки.

При обмене данными не по границе обменного слова в первом цикле связи с ОП будет передано количество байтов текущей строки меньше п и последующие передачи будут происходить обменными словами, байты которых расположены в двух соседних строках - оставшиеся байты текущей строки и часть байтов (дополнение до п) следующей строки.

Номер следующей строки определяет счетчик 71 номера строки.

Таким образом, адрес строки для каждого из п байтов (узлов 43 блока 1 памяти) может быть равным номеру строки и определяется Y старшими разрядами регистра 68, либо равным номеру следующей строки и определяться содержимым счетчика 71.

Какие байты адресовать текущей строки, а какие следующей определяет номер байта в строке - это X младших разрядов регистра 68, которые поступают на вход дешифратора 70, а выходы дешифратора управляют через элементы 73 ИЛИ переключением адресов двухвходовых мультиплексоров 74.

На первые входы всех мультиплексоров 74 подаются У старших разрядов регистра 68, а на вторые входы содержимое счетчика 71.

Те байты, для которых не вырабатываются сигналы переключения адреса, проадресуются текущей строкой, а байты, для которых вырабатываются сигналы переключения адреса, проадресуются следующей строкой.

Принцип адресации байтов текущей и

следующей строки в зависимости от номера байта в строке для п 8, X Iog28 3 приведен в табл.3.

Для первого байта сигналы переключе0 ния адреса будут вырабатываться для всех состояний дешифратора 70, кроме нулевого. Это состояние равенства нулю X младших разрядов регистра 68 не используется для переключения адреса и все байты в этом

5 случае адресуются текущей строкой.

Для второго байта сигналы переключения адреса будут вырабатываться для всех состояний дешифратора 70, кроме нулевого и первого. Для третьего кроме нулевого,

0 первого и второго и так далее.

Последний п байт всегда адресуется текущей строкой.

В каждом цикле связи с ОП присутствует единичный сигнал на входе 33 блока, на

5 фоне которого,после приема-передачи обменного слова модифицируется в сторону увеличения содержимое регистра 68 арифметико-логическим устройством 72 на величину константы модификации, поступа0 ющей на вход 40 блока и равной количеству байтов обменного слова.

Результат модификации с выхода АЛУ 72 заносится в регистр 68, а разряды с (Х+1) до 2(это Y старших разрядов, определяю5 щих номер строки) заносятся в счетчик 71 номера строки по синхросигналу 65 входа 14 синхронизации с выхода элемента 69 И.

Затем по синхросигналу 75 входа 14 со0 держимое счетчика 71 увеличивается на единицу. На выход 32 блока выдаются адреса для байтов следующего обменного слова,

Второй блок управления памятью

5 (фиг.7) работает следующим образом:

Когда оперативная память готова к обмену данными, на вход 12 блока поступает сигнал разрешения обмена устройства с ОП. В ответ на этот сигнал устанавливается

0 в единичное состояние триггер 76 с ОП (ТСОП) по синхросигналу 64 входа 14.

На фоне этого триггера в зависимости от кода выполняемой операции вырабатываются при вводе стробы чтения порта А

5 на выходе четвертого 81 элемента И по синхросигналу 45 входа 14 и сигнал разрешения выходов порта А на выходе первого 78 элемента И. При вы воде вырабатываются стробы записи порта А на выходе третьего 80 элемента И по синхросигналу 45, а на

зыходе второго 79 элемента И сигнал разрешения сдвига. Стробы чтения при вводе и :тробы записи при выводе будут вырабатываться по каждому синхросигналу 45 до тех юр, пока не установится в единичное состояние триггер 77 равенства нулю константы передачи (ТКПДНО). по которому сбрасывается триггер 76 ТСОП по синхросигналу 64, (запрещая работу всех элементов И.

Триггер ТКПДНО устанавливается в единичное состояние по синхросигналу 75 при наличии сигнала равенства нулю константы передачи на входе 39 блока. Выход этого триггера является сигналом конца обмена устройства с ОП, который выдается на выход 15 блока, а также блокирует повторную установку триггера ТСОП до тех пор, пока не смодифицируется регистр счетчика байтов на величину константы передачи, т.е. до прихода на вход 30 блока сигнала сброса.

Блок 7 формирования циклов (фиг.8) работает следующим образом.

На вход 18 блока поступает константа передачи (КП), указывающая количество байтов, которым необходимо обменяться с ОП за один цикл связи.

В общем случае значение константы передачи определяется по формуле: КП Кхп йайтов, где К - количество строк, К т.

В дальнейшем для простоты описания примем К т, т.е. максимальное значение константы передачи будет определяться емкостью блока 1 памяти: КП nxm.

Величина КП определяется X младшими разрядами адреса данных ОП и общим количеством байтов, которыми должны обменяться ОП и ПФУ, т.е. счетчиком байтов CCW.

| При X 0 КП 1 -(п-1) байтов. | Величина КП для п 8, X Iog2 8 3 в зависимости от счетчика байтов (СЧБ) CCW представлена в табл.4.

При X 0 величина КП зависит от счетчика байтов CCW следующим образом:

а) СЧБ п, КП СЧБ - будет передано одно обменное слово, количество байтов в котором определяется счетчиком байтов; | б) этом случае будет два цикла связи с ОП, которым соответствуют две константы КП1 и КП2. | Величины КП1 и КП2 определяются по формуле:

СЧБ:п а + Ь, где а -- целая часть частного, а т;

b - остаток делимого, b п.

Эти величины определяют соответст- венно количество строк и количество байтов в строке для КП1 и КП2, т.е. КП1 а п байтов, КП2 b байтов, при b О КП2 0;

Ь) СЧБ m n - для передачи такого количества байтов потребуется три вида констант;

КП m п, КПн-1 а п, КП|+2 b Величины I, a, b определяются из формул:

СЧБ:т n i + п

h:n A + b, где I, a - целые части частного,

b - остатки делимого. 0При h п КПн-1 0, при b 0 КПи-2 О

Для хранения константы передачи используется регистр 86 константы передачи.

Количество разрядов регистра 86 определяется по формуле:

5С 1одг(п К) + 1 logan + log2K + 1 X +

+Ь+ 1, где С - количество разрядов регистра 86.

Константа передачи перед началом обмена с ОП поступает по линии 89 входа 18 0 блока и с нулевого направления мультиплексора 82 заносится в регистр 86 по сигналу 90 входа 18 блока.

В цикле связи с ОП, т.е. при установленном триггера ТСОП, выход которого поступа- 5 ет на вход 33 блока, содержимое регистра 87 модифицируется арифметико-логическим устройством 87 в сторону уменьшения на величину константы модификации (КМ).

0Результат модификации заносится в регистр 86 с первого направления мультиплексора 82 по синхросигналу 65 входа 14.

Выбором направления мультиплексора 82 и режимом работы АЛУ 87 управляет 5 триггер ТСОП с входа 33 блока.

Строб занесения результата модификации будет вырабатываться на выходе первого 84 элемента И до тех пор, пока содержимое регистра 86 не обнулится. В 0 этом случае на выходе второго 88 элемента И вырабатывается сигнал равенства нулю константы передачи, который поступает на выход 39 блока, вызывая сброс триггера ТСОП на входе 33 блока.

5Константа модификации указывает количество байтов каждого обменного слова передаваемого или принимаемого в/из ОП.

Константа модификации вырабатывается на выходе постоянного запоминающего 0 устройства (ПЗУ) 83 в зависимости от значения X младших разрядов адреса данных ОП, поступающих на вход 11 блока и от X младших разрядов регистра 86.

Величина КМ может быть равной от 1 до

5 п байтов. Если в цикле связи с ОП обмен

ведется одним обменным словом, то величина КМ равна величине КП, т.е. КМ КП

1 - (п-1) байтов.

При обмене блоками данных КМ п байтам.

Пример формирования КМ для п 8, X 3 приведен в табл.5,

Блок 9 формирования маски (фиг.9) работает следующим образом:

При выполнении операции ввода одновременно с обменным словом в ОП с выхода регистра 93 маски выдается маска записи, указывающая какие байты обменного слова должны быть записаны в ОП, а какие нет.

Разрядность регистра 93 равна количеству байтов п в обменном слове.

При передаче блока данных каждому обменному слову соответствует единичная маска для всех байтов.

При передаче одного обменного слова маска формируется как и константа модификации в зависимости от X младших разрядов адреса данных ОП и X младших разрядов константы передачи, поступающих соответственно с входов 11 и 38 бяока на входы постоянного запоминающего устройства 91. С выхода ПЗУ 91 при выполнении операций ввода маска заносится в регистр 93 в циклах связи с ОП по синхросигналу 64 входа 14 с выхода элемента 92 И.

Код выполняемой операции определяется сигналом задания направления передачи на входе 17 блока.

Цикл связи с ОП определяет триггер ТСОП на входе 33 блока.

Пример формирования маски записи ОП для п 8, X 3 представлен в табл.6.

Блок 10 определения сдвига (фиг. 10 работает следующим образом):

Величина сдвига для операций ввода и вывода определяется вычитанием X младших разрядов регистра номера байта порта А, из X младших разрядов адреса данных ОП, поступающих соответственно с входов 31 и 11 блока на входы АЛУ 94.

Величина сдвига с выхода АЛУ 94 заносится в регистр 96 сдвига в циклах связи с ОП по синхросигналу 64 входа 14 с выхода элемента 95 И.

Цикл связи с ОП и код операции для АЛУ 94 задает триггер ТСОП с входа 33 блока.

Разрядность X регистра 96 сдвига определяется по формуле:

X logan.

Величина сдвига определяется по формуле:

СДВ АОП-НБ, где СДВ - величина сдвига.

АОП - X младших разрядов адреса данных ОП.

НБ - X младших разрядов регистра номера байта порта А.

Сдвигатели 8 (фиг. 11, 12) работают следующим образом:

Для сдвига п байтового слова в каждом сдвигателе используются п/2 узлов 97. Каждый узел содержит микросхему К1800ВР8, представляющую собой комбинационный

16-разрядный многофункцинальный сдви- гатель с возможностью расширения на любое число разрядов. Микросхема содержит входы управления сдвигом, определяющие число разрядов, на которое необходимое

произвести сдвиг и входы управления видом сдвига.v

Из видов сдвига в первом сдвигателе (фиг. 11) используется циклический сдвиг вправо, во втором сдвигателе (фиг. 12) циклический сдвиг влево и в обоих сдвигателях используется код блокировки выходов.

При выполнении операций ввода на информационные входы первого сдвигателя (фиг.11) поступают данные по буферной магистрали 24.

В цикле связи с ОП на первые входы узлов 97 подается величина сдвига с входа 41 блока, а на вторые входы узлов 97 подается сигнал с входа 35 задающий код циклического сдвига вправо. Результат сдвига выдается с выходов узлов 97 на шины 22 системной магистрали до тех пор пока присутствует единичный сигнал на входе 35. По сбросу этого сигнала запрещается выходы

узлов 97.

При выполнении операций вывода информация с системной шины 22 поступает на входы второго сдвигателя 8 (фиг, 12). Величина сдвига также задается с входа 41

блока, а код циклического сдвига влево поступает с входа 34 блока. Результат сдвига с выходов узлов 97 выдается в буферную магистраль 24 до тех пор пока не сбросится сигнал, задающий код циклического сдвига

влево на выходе 34 блока.

По сбросу этого сигнала выходы узлов 97 отключены от буферной магистрали 24.

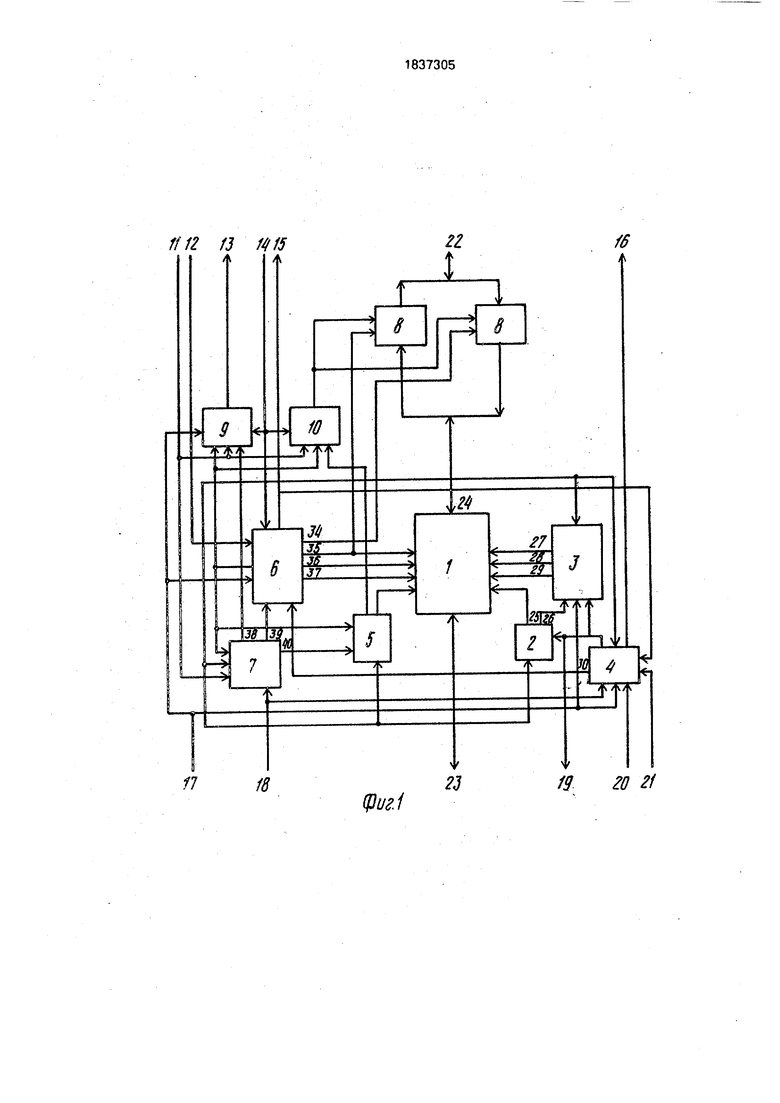

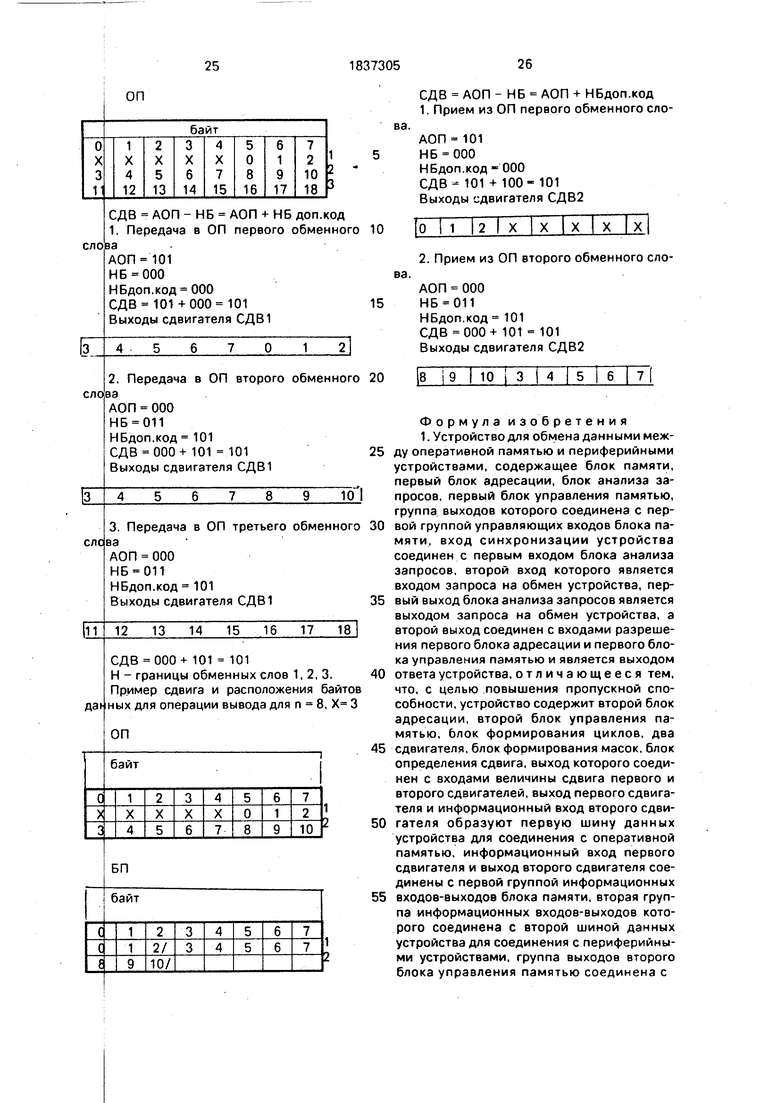

Ниже приводятся примеры определения величины сдвига и расположения байтов данных на выходах сдвигателей в ОП, в блоке 1 памяти для операций ввода и вывода для п 8, Х 3.

Пример сдвига и расположения байтов данных для операции ввода при п 8,

Х 3.

Расположение байтов данных

БЛ

1 2 3

on

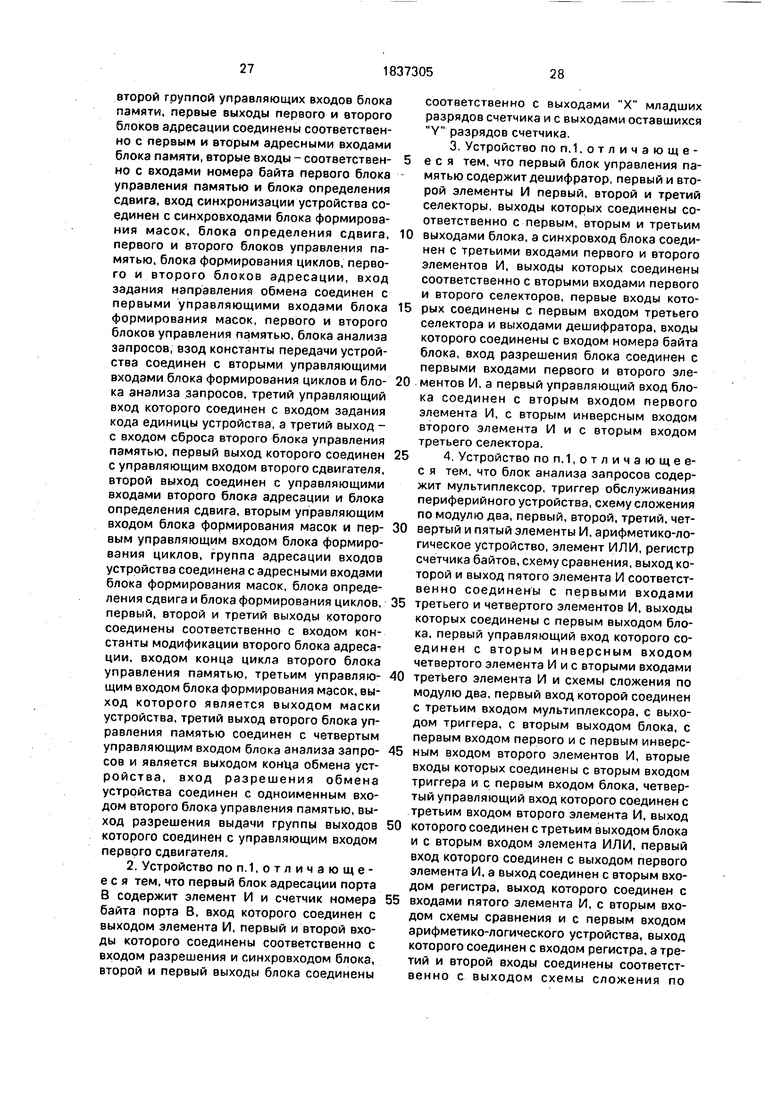

СДВ АОП - НБ АОП + НБдоп.код 1. Прием из ОП первого обменного слоАОП - 101 НБ 000 НБдоп.код-000 СДВ- 101 + 100- 101 Выходы сдвигателя СДВ2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для обмена информацией | 1982 |

|

SU1059561A1 |

Изобретение относится к области вычислительной техники, в частности, к устройствам обмена данными. Оно может быть использовано в качестве буфера данных для каналов ввода-вывода ЭВМ. Цель изобретения - повышение пропускной способности, сокращение оборудования. Цель достигается тем, что в устройство для обмена между оперативной памятью и периферийными устройствами, построенное на основе двухадресного полупроводникового блока памяти, Изобретение относится к области вычислительной техники и может быть использовано в качестве буфера данных для каналов ввода-вывода ЭВМ. Целью изобретения явлется повышение быстродействия устройства. Сущность изобретения заключается в том, что для повышения пропускной способности каналов в устройстве для обмена данными между ОП и периферийными устройствами для буферизации данных используется полупроводниковая память и комбинационный сдвигатель. Управление введены второй блок адресации, второй блок управления памятью, блок формирования циклов, два сдвигателя, блок формирования масок, блок определения сдвига. Введение новых блоков позволило построить устройство для обмена данными на основе двухадресного полупроводникового блока памяти и комбина-ционных сдвига- телей. При этом управление адресацией, режимами считывания, записи блока буферной памяти организовано таким образом, что имеется возможность одновременного обращения к разным байтам слов двух смежных строк, а комбинационный сдвигатель расположит байты данных на шинах данных в соответствии с адресом памяти, в которую производится запись. Это позволяет производить накопление данных в буферной памяти, не ожидая появления начального адреса оперативной памяти, и организовать обмен данных с оперативной памятью блоком данных (в несколько обменных слов за одну передачу данных в ОП). 8 з.п. ф-лы, 14 ил. 6 табл. адресацией, режимами считывания, записи буферной памяти, применяемой для хранения данных, построено таким образом, что разрешается одновременное обращение к разным байтам слова двух смежных слов данных.« Комбинационный сдвигатель используется для правильного расположения байтов обменного слова при записи их в ОА или буферную память. При реализации такого устройства для управления одновременным обращением к смежным словам буферной памяти разрабоfe С CJ VJ CJ о ел

АОП 101 НБ 000 НБдоп.код 000 СДВ 101+000 101 Выходы сдвигателя СДВ1

АОП - 000 НБ 011 НБдоп.код 101 СДВ 000+ 101 101 Выходы сдвигателя СДВ1

слова

АОП 000 НБ 011 НБдоп.код 101 Выходы сдвигателя СДВ1

СДВ 000 + 101 101 Н - границы обменных слов 1, 2, 3. Пример сдвига и расположения байтов дайных для операции вывода для п 8, Х 3

ОП

I БП

ва.

5

0

5

0

5

5

0

Формула изобретения 1. Устройство для обмена данными между оперативной памятью и периферийными устройствами, содержащее блок памяти, первый блок адресации, блок анализа запросов, первый блок управления памятью, группа выходов которого соединена с первой группой управляющих входов блока памяти, вход синхронизации устройства соединен с первым входом блока анализа запросов, второй вход которого является входом запроса на обмен устройства, первый выход блока анализа запросов является выходом запроса на обмен устройства, а второй выход соединен с входами разрешения первого блока адресации и первого блока управления памятью и является выходом ответа устройства, отличающееся тем. что, с целью повышения пропускной способности, устройство содержит второй блок адресации, второй блок управления памятью, блок формирования циклов, два сдвигателя, блок формирования масок, блок определения сдвига, выход которого соединен с входами величины сдвига первого и второго сдвигателей, выход первого сдвигателя и информационный вход второго сдвигателя образуют первую шину данных устройства для соединения с оперативной памятью, информационный вход первого сдвигателя и выход второго сдвигателя соединены с первой группой информационных входов-выходов блока памяти, вторая группа информационных входов-выходов которого соединена с второй шиной данных устройства для соединения с периферийными устройствами, группа выходов второго блока управления памятью соединена с

второй группой управляющих входов блока памяти, первые выходы первого и второго блоков адресации соединены соответственно с первым и вторым адресными входами блока памяти, вторые входы - соответственно с входами номера байта первого блока управления памятью и блока определения сдвига, вход синхронизации устройства соединен с синхровходами блока формирования масок, блока определения сдвига, первого и второго блоков управления памятью, блока формирования циклов, первого и второго блоков адресации, вход задания направления обмена соединен с первыми управляющими входами блока формирования масок, первого и второго блоков управления памятью, блока анализа запросов, взод константы передачи устройства соединен с вторыми управляющими входами блока формирования циклов и блока анализа запросов, третий управляющий вход которого соединен с входом задания кода единицы устройства, а третий выход - с входом сброса второго блока управления памятью, первый выход которого соединен с управляющим входом второго сдвигателя, второй выход соединен с управляющими входами второго блока адресации и блока определения сдвига, вторым управляющим входом блока формирования масок и первым управляющим входом блока формирования циклов, группа адресации входов устройства соединена с адресными входами блока формирования масок, блока определения сдвига и блока формирования циклов, первый, второй и третий выходы которого соединены соответственно с входом константы модификации второго блока адресации, входом конца цикла второго блока управления памятью, третьим управляющим входом блока формирования масок, выход которого является выходом маски устройства, третий выход второго блока управления памятью соединен с четвертым управляющим входом блока анализа запросов и является выходом конца обмена устройства, вход разрешения обмена устройства соединен с одноименным входом второго блока управления памятью, выход разрешения выдачи группы выходов которого соединен с управляющим входом первого сдвигателя.

соответственно с выходами X младших разрядов счетчика и с выходами оставшихся Y разрядов счетчика.

0 выходами блока, а синхровход блока соединен с третьими входами первого и второго элементов И, выходы которых соединены соответственно с вторыми входами первого и второго селекторов, первые входы кото5 рых соединены с первым входом третьего селектора и выходами дешифратора, входы которого соединены с входом номера байта блока, вход разрешения блока соединен с первыми входами первого и второго эле0 ментов И, а первый управляющий вход блока соединен с вторым входом первого элемента И, с вторым инверсным входом второго элемента И и с вторым входом третьего селектора.

5 4. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что блок анализа запросов содержит мультиплексор, триггер обслуживания периферийного устройства, схему сложения по модулю два, первый, второй, третий, чет0 вертый и пятый элементы И, арифметико-логическое устройство, элемент ИЛИ, регистр счетчика байтов, схему сравнения, выход которой и выход пятого элемента И соответственно соединены с первыми входами

5 третьего и четвертого элементов И, выходы которых соединены с первым выходом блока, первый управляющий вход которого соединен с вторым инверсным входом четвертого элемента И и с вторыми входами

0 третьего элемента И и схемы сложения по модулю два, первый вход которой соединен с третьим входом мультиплексора, с выходом триггера, с вторым выходом блока, с первым входом первого и с первым инверс5 ным входом второго элементов И, вторые входы которых соединены с вторым входом триггера и с первым входом блока, четвертый управляющий вход которого соединен с третьим входом второго элемента И. выход

0 которого соединен с третьим выходом блока и с вторым входом элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход соединен с вторым входом регистра, выход которого соединен с

5 входами пятого элемента И, с вторым входом схемы сравнения и с первым входом арифметико-логического устройства, выход которого соединен с входом регистра, а третий и второй входы соединены соответственно с выходом схемы сложения по

модулю два и с выходом мультиплексора, первйй вход которого соединен с первым входам первой схемы сравнения и с вторым управляющим входом блока, второй и третий управляющие входы блока соединены СООТЕ етственно с первым входом триггера и с втоэым входом мультиплексора.

Устройство по п. 1,отличаю щ е е- с я тем, что второй блок адресации содержит регистр номера байта порта А, элемент

И, д

шифратор, счетчик номера строки,

арис

метико-логическое устройство, п-2

энтов ИЛИ и п-1 мультиплексоров, вы- которых соединены с первым выходом ,синхровход которого соединен с периодом счетчика и вторым входом эле- а И, выход которого соединен с

элем ходы блок вым мен

третьим входом счетчика и вторым входом регистра, выход которого соединен с первымвход;

ВХОД1

вход

л вторым выходами блока, с первыми ми (п-1) мультиплексоров, с первым м арифметико-логического блока и с м дешифратора, выход которого соединен с третьим входом (п-1)-го мультиплексора и с входами п-2 элементов ИЛИ, выходы которых соединены соответственно

тьими входами п-2 мультиплексоров, .IB входы которых соединены с выхо- счетчика, второй вход которого соеди- : вторым входом регистра и с выходом метико-логического устройства, вто- зход которого соединен с входом коны модификации блока, а управляющий тЗлока соединен с третьим входом

с тр втор дом нен ари рой стан вхо;

арифметико-логического устройства и с первым входом элемента И.

дов пы

злока, выход разрешения выдачи груп(ыходов которого соединен с первым входом четвертого элемента И и с выходом neptoro элемента И, второй вход которого соединен с первым управляющим входом бло а и с вторым инверсным входом второго элемента И, выход которого соединен с первым входом третьего элемента И и с первым выходом блока, второй выход которого соединен с первыми входами первого и второго элементов И и с выходом триггера связи с оперативной памятью, первый вход которого срединен с входом разрешения обмена

6Л01

а, а второй инверсный и четвертый входы триггера соединены с третьим выходом блока и с выходом триггера равенства нулю

константы передачи данных, перзый и третий входы которого соединены соответственно с входом конца цикла и входом сброса блока, синхровход которого соединен с третьим и пятым входами триггера связи с оперативной памятью, с вторым входом триггера равенства нулю константы передачи данных и с вторыми входами третьего и четвертого элементов И.

0 7. Устройство поп.1,отличающее- с я тем, что блок формирования циклов содержит мультиплексор, постоянное запоминающее устройство, первый и второй элементы И, элемент ИЛИ, регистр констак5 ты передачи данных и арифметико-логическое устройство, выход которого соединен с вторым входом мультиплексора, зыход мультиплексора соединен с первым входом регистра, выход которого соединен с пер0 вым входом арифметико-логического блока, с вторым входом постоянного запоминающего устройства, с третьим выходом блока и с инверсными входами второго элемента И, выход которого соединен с вторым выхо5 дом блока, первый выход которого соединен с выходом постоянного запоминающего устройства и с вторым входом арифметико-логического устройства, третий вход которого соединен с третьим входом мультиплексо0 ра, с первым входом первого элемента И и с первым управляющим входом блока, адресный вход и синхровход которого соединены соответственно с первым входом, постоянного запоминающего устройства и с

5 вторым входом первого элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с вторым входом регистра, а первый вход соединен с первым входом мультиплексора и вторым

0 управляющим входом блока.

0 адресный входы блока соединены соответственно с вторыми и первыми входами постоянного запоминающего устройства, выходы которого соединены с первыми входами регистра, а выход регистра соединен с

5 выходом блока.

первый вход которого соединен с синхров- ходом блока, а второй вход соединен с третьим входом арифметико-логического блока и управляющим входом блока, адресный вход и вход номера байта которого соТ - текущая строка, С - следующая строка.

единены соответственно с первым и вторым входами арифметико-логического блока, выход которого соединен с первым входом регистра, а выход регистра - с выходом блока.

Таблица 1

Таблица 2

Таблица 3

Таблица 4

Таблица 5

Таблица 6

Фиг. 1

/г/Г

&

фиг.3

18

1-Х

J8

ЩиМ

34

1,2

м

/И/7

22

ПП ЛП

jiпП-Л

65П ППП

75

П

п

л

го

19

Л

я.

26

Х

97

12

f 2

§7

Z

1 2

97

(л-f), /7

г

Фиг. К

п

л

Фиг. 13

CvJ

ю

:

I

и

р

10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4272809, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-30—Публикация

1990-07-13—Подача