трсты1 иыходом регистра спизи с п юиессором, третий -- с пятым }5и.одо.м первого регистра , ЧеТ.СрТЫ|1 -- со irrOpblM 15.ЧОЛ.ОМ

устройст; ;, пятый - - с П5гг1 1м пхо,ч(-)м ycTpoiiства, 1 ср:чы-й выход - с четвертым выходом устройства, второй выход - с четвертым входом схемы объедппенпя адресных п ииформацнонпых шнп, 1зыходпую схелгу 1п-1формац 1Н, вход которой соедипеп с третьим выходом регпстра даппых, а выход с пятым выходом

устройства, выходную схему адреса, хстройсП ввода- вывода, выход которой соедипеп с nieстым выходом устройст1 а. Одпако пз сстпое устройство пмеет пизкую пропускную способность, обусловлеппую отсутствпем аппаратных средств для храненпя п модпфпкгщип команды, управляющей передачей массивов данны.х между памятью процессора п его внутренней памятьк;; кроме того, управление ирпорнтетами запросов в этом устройстве нриводнт к сокращепню времепи связн УВВ с процессором за счет потерь времени, связанных с изменением приоритета УВВ в интерфейсе.

Целью нзобретепня я)5ляется rioBijuncnne пропускной способности ycTpoiicTBa п времени связи с процессором. Это достигается тем, что предлагаемое устройство содержит регистр маски запросов, первый вход которого соедииеп с третьим выхо.аом регпстра связи с процессором, второй вход - с выходо.м ден1Ифратора кода операций, а выход--со 15торым входом схемы апалнза приоритета. разретисния реалнзацнн запроса, вход которО Ч) соединен с выходом деншфратора адреса устройства вводавывода, а выход - с третьнм

входом схемы анализа прпорптетов, ип фраT(jp адреса, ход которого- соедпнен со вторым выходом схемы ана;глз;1 ):ор то оя. а - с пятым входом схемы объедпиошя а.чресных и информационных ишн и вхо.юм выходной схемы адреса устройств ввода- вывода, второй регистр команд, первый вход которого соединен с пятым выходом первого регистра команд, второй вход --- е третьим выходом регистра связи с процессором, а nepBbiii выход -- с третьим входом первого регистра команд, вторую схему формирования адреса, первый п второй входы которой соединены со вторым и третьим выходами второго регистра команд, а выход - гиестым входол схемы объединения адресных и информационных шин, вторую схему модпфикацпи, первый п второй входы которой соедипепы с третьим п четвертым выходами второго регистра команд соответственно, а ВЫХОД -- с третьпм входом второго регистра команд, кроме того, шестой выход первого регистра -комапд соедипеп со вторым входом первой схемы модификации.

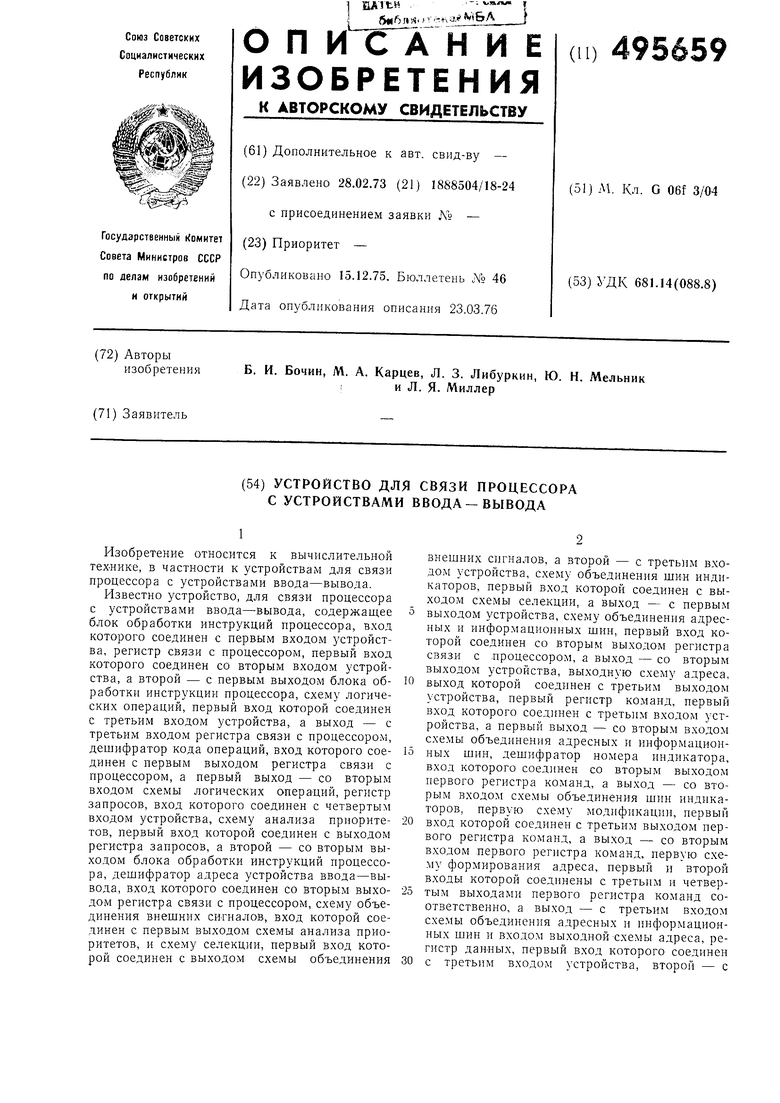

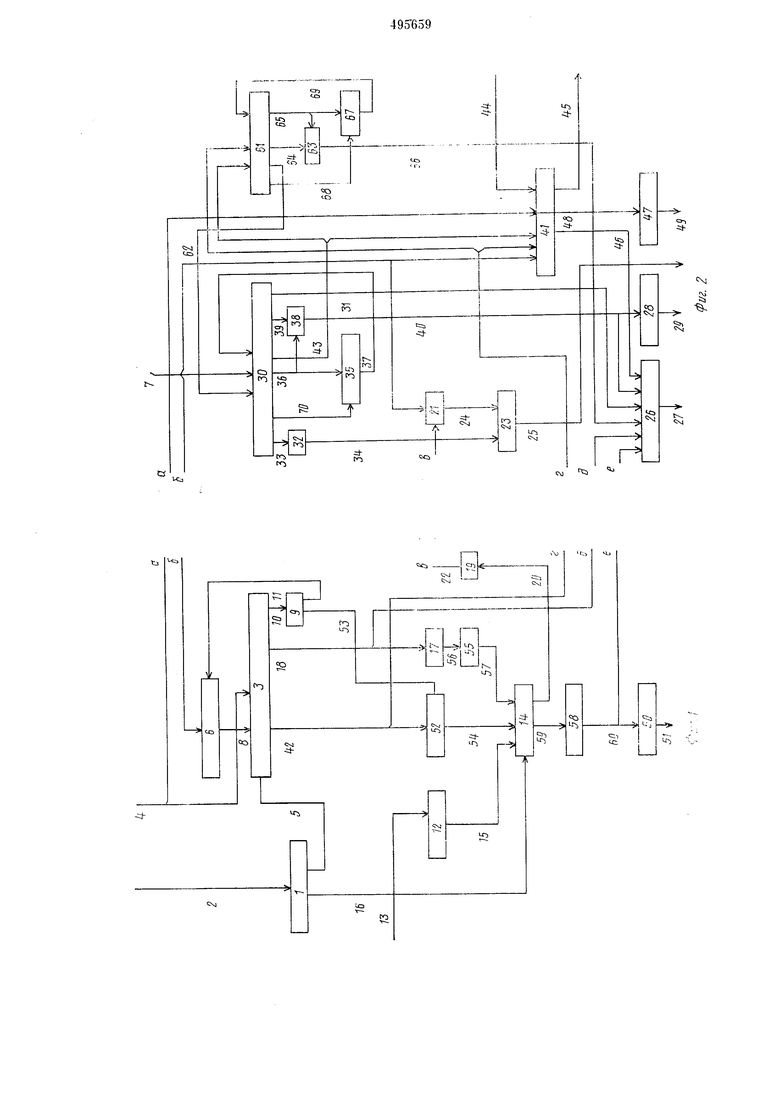

На фиг. 1 представлена блок-схема устройства для связн процессора с устройствамн для звода-вывода; на фнг. 2 -- структура команды управления обменом даинымн между намятью устройства или ироцессора и. устройствам . звода-вывода; на фиг. 3 - структура команды уиравлення обменом данными между намятью ироцеееора и памятью OHiicbiBacMoKj стройства.

ycTpoiicTBo сод.ерЖ1гг блок обработки HHCIрукций нроцессора 1, вхо.т которого игинами 2 соединен с нервым входом устройства; регистр 3 связи с нроцессором, первый вход которого ишнамн 4 сосдине со г/горым выходом стройства, а второй вход ипыамл 5 - с первым выходом блока обрабо1-ки инстр к;ип1 процессора ; схему лснических операц;1Й d, первый i;xo;i, 1ч;;Т1 роГ| 1ипнами 7 сос ллиен с третьим входом устройства, а выход нппами 8 - - с третьим ВХОДОЛ1 регистра 3 связи с процессором; детпифратор кода оиераций 9, вход которого н инамн 10 еоедипеи с пе;з-зым вькходом регистра 3 с нроцессором, а нервьп выход шииами 11 -- со ВТО-рым входом схемы логических операций 6; решютр заиросоз 12, вход которого шинами 13 соедппен с четвертым входо.м устройства; схему ана.лиза ир;10)нтетов 14, первый вход котор;)й njiinj-iMi; 15 соед1;нем с выходом регистра заиросов 12, а BTopoii типиами 16 -- со вторым выходом блока, o6pa6v)TKii инструкции ироцессора 1; дешифратор адреса 17 устройства ввода---вывода, вход которого П1ипами 18 .тииен со вторым выходом регистра 3 связи с процессором; схему объединения BHCHiHHx сигналов 19, вход которой junnaми 20 соедннен с первым 15ыходол1 схемы анализа нрноритетов 14; схему сетекцин 21, нервый вход которой ншнамн 22 со-эд,1гнеи с выходом схемы об1)е,.инен1;я вненгннх с11гна.1ов 19, а, второй вход ишиами 7 с третьнм ходом устройства; схему объединения HIHH пидикато М);з 23, вход которой 1иииами 24 соединен с выходом cxeMLii селекцни 21, а выход тинами 25 -- с иервым выходом устройства; схелгу объединения адресных и ниформацнониых 26, первый вход которой шииами 18 еоедннен со вторым выходом регистра связн 3 с ироцесcOiJOM, а выход нишами 27 - со BTOJJIJM BI-,IXOдом устройства; выходихю схему адреса 28. выход который И1ннамн 29 соединен с третьим выходом устройства; первый регистр коман.т 30, первый вход которого ип-шами 7 соединен с третьнм входом устройства, а первый выход шинами 31 со вторым входом схемы 28 объединения адрееных н ннформаЦ1-ю Д)1х ппш; дешифратор 32 номера ни;1нка.тора, вход которого Н1инамн 33 соединен со вторым выходо.1 первого регистра комапд 30, а выход пшиами 34 - со вторым входом схел1Ы объединення шин индикаторов 23; иервую схему модификации 35, первый вход которой шинами 36 соединен с третьим выходом первого ре1истра команд 30, а выход шинами 37 - со вто)ым входом иервого регистра команд 30; иерзую схему форм 1рова1 ия a;ipeca 38, иерв1 1й и второй входы которой птииами 36 и 39 соединены с третьим и четвертым выходами первого регистра команд 30 соответствешю, а выход Ш1 нами 40 -- с третьнм входол схемы объединения адрееных н информациоин1ях ишн 25 и вхол,ом выхо.чной схемы адреса 28; регистр данных 41 первый вход которого шинами 7

соединен с третьим входом устройства, второй шинами 42 - с третьим выходом регистра связи 3 с процессором, третий шинами 43 - с иятым выходом первого регистра команд, четвертый 4 - со вторым входом устройства, 1ПЯТЫЙ шинами 44 - с пятым входом устройства, первый выход шинами 45 с четвертым выходом устройства, второй выход шииамм 46 с четвертым входом схемы объединения адресных и информационных шин 25; выходную схему информации 47, вход которой иаинами 48 соединен с третьим выходом рггист-ра данных 41, а выход шииами 49 - с иятым выходом устройства; выходную схему адреса 50 устройств ввода-вывода, выход которой шинами 51 соединен с шестым выходом устройства; регистр маски запросов 52, первый вход которого шинами 42 соединен с третьим выходом регистра связи 3 с процессором, второй вход шинами 53 с выходом дешифратора кода операции 9, а выход шинами 54 со вторым входом схемы анализа приоритета 14; регистр разрешения реализации запроса 55, вход которого шииами 56 соединен с выходом дешифратора адреса 17устройства ввода-вывода, а выход шинами 57 - с третьим входом схемы анализа приоритетов 14; шифратор адреса 58, вход которого шинами 59 соединен со вторым выходом схемы анализа приоритетов 14, а выход шинами 60 - с пятым входом схемы объединения адресиых и информационных шин 26 и входом выходной схемы 50 адреса устройств ввода-вывода; второй регистр команд 61, первый вход которого шинами 43 соединен с пятым выходом первого регистра команд 30, второй вход шинами 42 - с третьим выходом регистра связи 3 с процессором, а первый выход шинами 62 - с третьим входом первого регистра команд 30; вторую схему формирования адреса 63, первый и второй входы которой шииами 64 и 65 соединены со вторым и третьим выходами второго .регистра команд 61, а выход шииами 66 - с шестым входом схемы объединения адресиых и информационных шии 26; вторую схему модификаци} 67, первый и второй входы которой шинами 65 и 68 соединены с третьим И четвертым выходами второго регистра команд 61 соответствеино, а выход шинами 69 - с третьим входом второго регистра команд 61, кроме того, шестой выход первого регистра команд 30 шинами 70 соединен со вторым входом первой схемы модификации 35.

Передача команд управления из процессора в устройство осуш,ествляется следуюшим образом. По шинам 2 инструкций процессора в блок обработки ииструкций процессора 1 поступает инструкция «прием команды управления из процессора. С выхода блока обработки инструкций процессора 1 сигнал приема команды управления поступает в регистр 3 связи с процессором. При наличии этого сигнала команда управления, считанная из памяти процессора, с сопровождающей ее служебноП

информацией по илшам 4 ир;: имастся гистр 3 связи с ироцоссопом.

Запись коман.чы упраклеиия в память устройства осушсствляется следующим образгм. Адрес размещения команды ; памяти ycTp:;; iстза по niMiuiM ЬВ поступает на схему объе нения адресиых и информационных 2 и далее ио шинам 27 - в память устройст i. Затем производится аиал13 кода onepai ni

записи, который по шинам 10 пос Лпгют K;I дешифратор 9. Если задана запись комг.лды iравления без осхществлелия редактиОочаичя (посредством выполнения логических опо шruiii «П и «ПЛИ с информацией комапд1 1,

хранящейся з памяти), то вслед за передачей адреса в память устройства обмена произ;,:)дится передача команды управлешя, котоп я по шинам 42 поступает в регистр даииых 41. п далее по шинам 46 через схему объедиме-;; ;

26 выдается на шины 27. Если на дешифрат-,ре операций 9 расшифровываетея код логикеской операции, то сигнал об этом по шинам 11 передается на схему логическ; х операций О. на вход которой по шинам 7 поступает комапда управления, считанная по адресу, переданному в память. Данные со схемы логических операций 6 по шинам 8 пост пают в регистр 3, в котором в зависимости от кода записывается логическая сумма пли произведеиие информации команды, принятой из ироцессора и считанной из памяти. Результат выиолнешя логичеекой операции затем записывается в память устройства по адресу команды управления.

Во время передачи команды управ.тентя пз процессора в память устройства работа зла управления приоритетами запросов блокируется, для чего из блока обряботки инструкций процеесора по пшнам 16 па схему анализа

приоритета запросов 14 поступают бдокир чощие сигналы.

Реализация запросов стройства ввода - вьь вода на обмен информацией осунтествляется в такой последовательности. Запросы хстройстг.

ввода- вывода на обмен данным по шинам 13 поступают на вход регистра запросов 12, связанного щинами 15 со схемой анализа приоритетов 14. При наличии команды управления, индицируемой регистром разрещения реализяции запроса 55 (который возбуждается сигналами, поступающими по шинам 56 с дешифратора адреса 17), и отсутствии сигналов маски запроса в регистре маски запросов 52 (сигналы с которых ПО шинам 57 и 54 поступают на

схему анализа приоритетов 14) последняя выделяет сигнал, соответствующий старщему ззпроеу, который по шинам 59 поступает па шифратор адреса 58. С выхода щифратора 58 адрес команды управления по щикам 60 чере

схему объединения адресных и информационных шпн 26, поступает в память устройства, одновременно с этим производится возбуждение ;51дходной схемы 50 адреса устройства ввода-вывода. Команда управления, считанная из

памятп устройства, по шиналт 7 поступает в

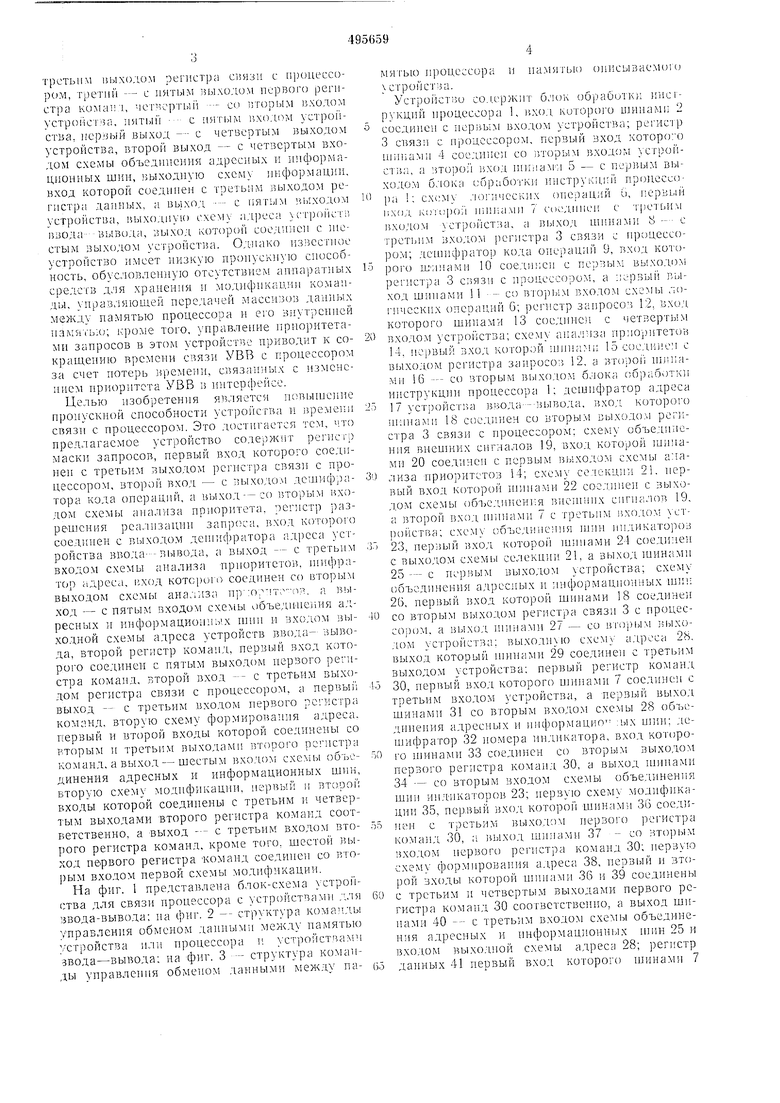

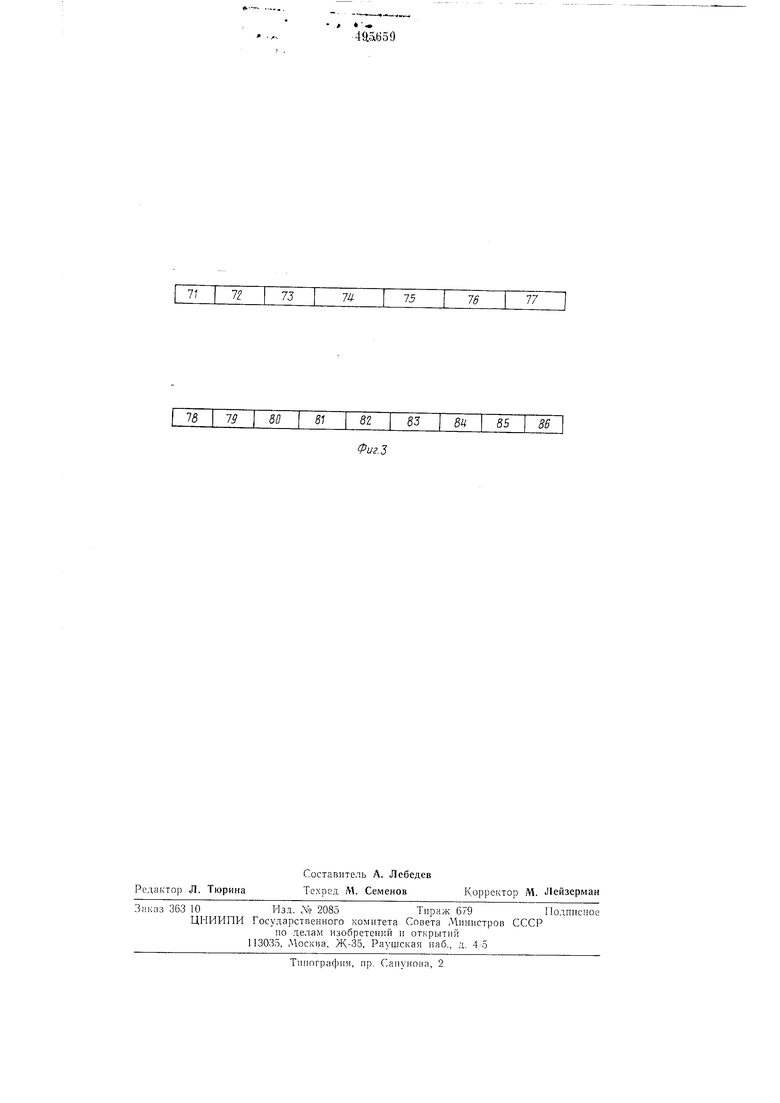

первый регистр команд 30. Структура команды ..правления, принимаемой в первый регистр команд 30, показана на фиг. 2.

Команда управления содержит следующие ноля: 71 - номер индикатора прерывания программы процессора при окончании обмена ио данной команде уиравления; 72 - формат данных, передаваемых между памятью и устройствами ввода-вывода; 73 - счетчик количества обменов, которое необходимо выполнить для завершения обмена; 74 - счетчик адресов размещения данных; 75 - упорядоченный список блоков , определяюи1ий последовательность размещения данных; 76 - упорядоченный список страниц блоков памяти; 77 - адрес дополнительной команды упразления.

Модис1 ицируемь е по;1Я 73 и 74 команды управления по планам 36 поступают па первую схему модификации команд управления 35, на эту схему по шинам 70 поступает информация о формате данных. Первая схема модификаций 35 увеличивает на «1 состояние счетчика адреса данных поля 74 и уменьшает на «1 состояние счетчика количества обмена поля 73, и по Шинам 37 передает их в соответствующие зоны первого регистра комапд 30. По окончании модификации команда управления по шинам 43 поступает на регистр данных 41, а с выхода регистра 3 но шинам 46 - на схему объединения адресных и информационных шин 26 для возврата в память устройства. Затем первая схема адреса 38 на основании информации о состояиии счетчика адресов дачных, ноступающей по шинам 36, производит выбор соответствуюших иомеров страниц и блоков, поступающих по шинам 39, объединени е их с номером ячейки и выдачу по иииам 40 в выходную схему адреса 28 или схему объединения адресных и информационных шин 26.

Если обмен данными осуществляется между устройством ввода-вывода и памятью процессора, то возбуждается выходиая схема адреса 28. Если данные записываются в память процессора, то информация от устройств ввода-вывода ио шинам 44 через регистр данных 41, ишны 48, выходную схему информации 47 и шины 49 поступает в память. Если читаются из памяти процессора, то информация по шинам 4 через регист р данных 41 шины 45 поступает в пнформационные шины устрой тп ввода-вывода и используется тем устройством ввода-вывода, номер которого возбужден на шпнах51.Если данные записываются в пад-ять устройства для связи процессора с устройствами -ввода-вывода, то информация от устройств ввода-вывода по шипам 44 через регистр данных 41, шины 46, схему объединения адресных и информационных шн}: 26 и шины 27 поступает в память. Если данные читаются из памяти устройства, то информация но m iнам 7 через регистр данных 41 и шипы 45 поступает к устройствам н; ода-вывода. Особенность 11еализации запроса устройства

В во да---вывод а, имеющего дополнительною команду уиравления, заключающуюся в том. что, после обмена по основной команде уиравления, производится обмен той же информацией по дополиительной комаиде управления. Чтение дополнительной комаиды уиравления производится ио адресу, хранящемуся в поло 77 команды уиравления, который по шинам 31 поступает на схему объедиисння адресных ипформациоииых шин 26. По мере реализаци запросов устройств ввода-вывода состояиие счетчика количества обменов команды уиравления достигает нулевого значения. Это служит сигналом для возбуждения шин индикаторов ирерывания программы процессора.

Возбужде 1ие шип индикаторов прерываИ:1Я осуществляется следующим образом. Код )ioмсра индикатора с иервого регистра команд 30 по щинам 33 поступает на дешифратор 32 номера индикатора и далее по шииам 34 через схему объедииеиия шин иидикаторов 23 и выходные шииы 25 - в ироцессор.

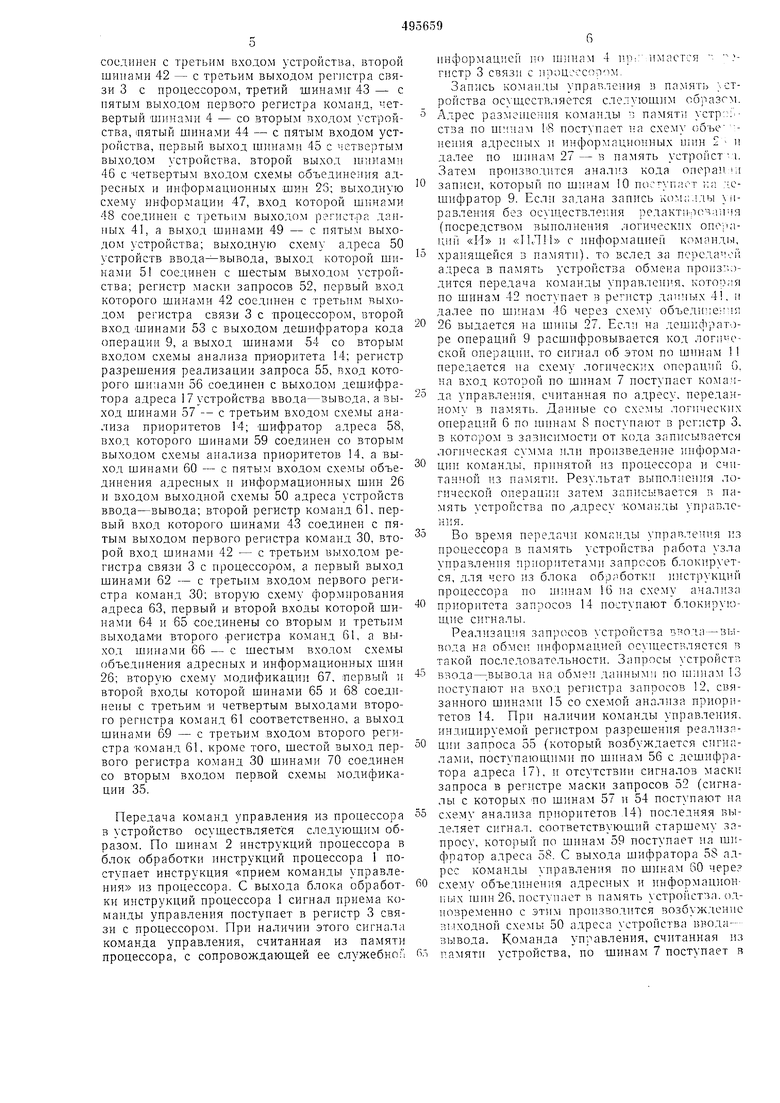

Обмен информацией между буферными зонами памяти устройства и памятью процессора осзществляется с помощью комаиды управлеиия, изображенной на фиг. 3. Команда иравлепия содержит следующие иоля: 78 - - номер иидикатора прерывания ирограммы процессора при окончании обмена по даниой ирограмме управления; 79 - формат данных, передаваемых между памятями процессора и устройства; 80 - счетчик количества обмеиов. которое )1еобходимо выиолнить для завершения обмена; 81 -- счетчик адресов размеи1,ения данных в памяти процессора; 82 - упорядоченный список блоков памяти процессора, определяющий последовательность размещ,еиия данных; 83 - упорядоченный список страниц блоков памяти процессора; 84 - счетчик адресов размещения данных в памяти устройства; 85 - упорядоченный список страниц памяти устройства; 86 - код направления персдачи информации.

Для повышения пропхскной способности устройства обмена хранение команд уиравления обменом информацией между памятялги процессора и устройства осуществляется не ч памяти, а во втором регистре комаил, 61. П..MI обмене информацией между памятялш процессора и устройства последнее одновременно формирует два адреса, между которыми иа основании кода направления иередачи информации, содержащейся в поле 86, осуществляется передача данных. Формирование адреса размещения данных и модификация адресных полей 80 и 81 осуществляются с помощью первой схемы формирова1П-1я адреса 38 н иервой схемы модификации 35 соответственно. Передача полей 78-83 в первый регистр кo.тaнд 30 осуществляется по Щинам 62; возврат полей 78-83 во второй регистр команд 61 осуществляется но игипам 43. Адрес ра:;меи1;еипя да;;иых в памяти процессора по птииам 40 через выходную схему адреса 28 и щины 29 пост -пает в память процессора. Формирование а.чреса размещения данных в памяти устройства осуществляется с помощью второй схемы формирования адреса 63, на которую по шинам 64 поступает поде 85 списка страниц, а по шинам 65 - поле 84 счетчика адресов данных. С выхода второй схемы формирования адреса 63 сформированный адрес -по шинам 66 через схему объединения адресных и информационных шин 26 и шины 27 поступает в память устройства. Модификация адреса размещения данных в памяти устройства осуществляется второй схемой модификации 67, на которую по шинам 65 поступает поле 84 счетчика адресов данных, а по шинам 68 поле 79 формата данных. После увеличения состояния счетчика адресов данных по шинам 69 осуществляется запись состояния счетчика адреса данных во второй регистр команд 61. Направление передачи данных определяется полем 86.

При передаче данных из памяти процессора информация по шинам 4 через регистр данных 41, шины 46, схему объединен 1я адресных и информационных шин 26 и шины 27 поступает в память устройства. При передаче данных из памяти устройства, 1 нформация по шинам 7, через регистр данных 41, шины 48, выходную схему информации 47 и шины 49 поступает в память процессора.

Реализация программно-управляемой коммутации сигналов прерывания программы процессора от внешних сигналов включает в себя, во-первых, запись в фиксированные ячейки памяти устройства обмена слов прерывания и, во-вторых, чтение этих слов по адресам, сформированным узлом управления приоритетами запросов устройств ввода-вывода и внешних сигналов и передачи их по шинам индикаторов в процессор. Запись слов прерывания для внешних сигналов осуществляется аналогично засылке команд управления для устройства ввода-вывода.

Реализация запросов внешних сигналов на прерывание осуществляется следующим образом. Запросы внешних сигналов по шинам 13 поступают в регистр запросов 12. При разрешения (код «1) в соответствующих разрядах регистра маски запросов 52 старщий запрос внешних сигналов проходит через схему анализа приоритетов 14, по шинам 59 поступает на шифратор адреса 58 и по Шинам 20 - на схему объединения внешних сигналов 19. По адресу, сформированному шифратором адреса 58 и переданному по шинам 27 в память устройства, производится чтение слова прерывания. Слово прерывания, выбранное из памяти устройства обмена, ПО шинам 7 поступает на схему селекции 21. При наличии разрешающего сигнала, поступающего по шинам 22 со схемы объединения внешних сигналов 19, слово прерывания проходит через схему селекции 21 и по шинам 24 выдается на схему объединения шин индикаторов 23 и далее по шинам 25 - в процессор.

Применение регистра маски запросов 52 на входе схемы анализа приоритетов 14 позволяет

организовать гибкую дисциплину обслужипаиия. Для этого процессор с помощью инструкции «прием команды управления осуществляет прямую Передачу информации в регистр маски запросов 52. При этом запросы, для которых в соответствующих разрядах регистра маски запросов 52 имеются нули, оказываются исключенными из очереди на обслуживание. Таким образом, изменяя состояние регистра

маски запросов 52. можно обеспечить любую комбинацию запросов на входе схемы анализа приоритетов 14.

Форм у л а и 3 о б р е т е н и я

Устройство для связи процессора с устройством ввода-вывода, содержащее блок обработки инструкций процессора, вход которого соединен с первым входом устройства, регистр связи с процессором, первый вход которого

соединен со вторым входом устройства, а второй - с первым выходом блока обработки инструкций процессора, схему логпчески.х операций, первый вход которой соединен е третьим входом устройства, а выход-с третьим входом регистра связи с процессором, дешифратор кода операций, вход которого соединен с первым выходом регистра связи с процессором, а первый выход - со вторым входом схемы логических операций, регистр запросов.

вход которого соединен с четвертым входом устройства, схему анализа ириоритетов, первый вход которой соединен с выходом регистра запросов, а второй - со вторым выходом блока обработки инструкций процессора, дешифратор адреса устройства ввода-вывода, вход которого соедпнен со вторым выходом регистра связи с процессором, схему объединения внешних сигналов, вход которой соединен с первым выходом схемы анализа приоритетов.

II схему селекции, первый вход которой соединен с выходом схемы объединения внешних сигналов, а второй - с третьим входом устройства, схему объединения щпн индикаторов, первый вход которой соединен с выходом

схемы селекции, а выход - с первым выходом устройства, схему объединения адресных и информационных шин, первый вход которой соединен со вторым выходом регистра связи с процессором, а выход - со вторым выходом

устройства, выходную схему адреса, выход которой соединен с третьим выxoдo устройства, первый регистр команд, первый вход которого соединен с третьим входом устройства, а первый вы.од - со вторым входом схемы объединения адресных и информационных шин. дешифратор номера индикатора, вход которого соединен со вторым выходом первого регистра команд, а выход - со вторым входом схемы объединения шин индикаторов, первукт схему

модификации, первый вход которой соедпнен с третьим выходом первого регистра команд, а выход - со птО|)ым входом первого регистр команд, перзую схему (1)ормирования адреса первый и BT:)po:i пходы которой соединены с третьим и четвертым выходами первого регист11

pa команд соответственно, а ныхол с третьим входом схемы объединения адресных н информационных шии н входом выход}1ой схемы адреса, регистр данных, нервый вход которого соединен с третьим входом устройства, тто рой - с третьим выходом регистра связи с процессором, третий --- с нятым выходом но)вого регистра команд, четвертый - со вторым входом устройства, иятый - с нятым входом устройства, нервый выход - с четвертым выходом устройства, второй выход - с четвертым входом схемы объединения ад11есг1ых и информационных шии, выходную схему и)ц|)ормации, вход которой соедипе: с третьим выходом регистра данных, а выход - с иятым выходом устройства, выходную схему адреса устройств ввода-вывода, выход которой соединен с шестым выходом устройства о т д и ч а ющееся тем, что, с цедью повышения иронускной способности устройства и времени связи с процессором, оно содержит регистр маски запросов, первый вход которого соединен с третьим выходом регистра связи с процессором, второй вход - с выходом дешифратора кода операций, а выход - со вторым входом схемы анализа приоритета, регистр разреше12

ИНН реализации заироса, вход которого соедиHeii с выходом дешифратора адреса устройства ввода--вывода, а выход -- с третьим вхо;:0.м схемы анадиз;, п)юритетов, ишфратор адреса, вход которого соединен со вторым выxoдo i схемы анализа приоритетов, а выход - с иятым входом схемы объедииения адресных и 1и-1формацио11ных П1ии н входом выход}юй схемы адреса устройств ввода-вывода, второй регистр команд, первый вход которого соединен с иятым выходом rie)Boro ре)Л1Стра команд, второй вход --- с третьим выходом регистра связи с нроцессором, а нервый выход с третьим входом иервого рег1;стра команд, вторую схему формирования адреса, первый i второй входы которой соединены со вторым :i третьим выходами второго регистра команд. а выход - с шестым 15ходом схемы объедин. Н11Я адресных и информационных шин, вторую схему модификации, первый и второй входы которой соединены с третьим и четвертым выходами второго регистра команд соответственно, а выход - с третьим входом второго ре1истра команд, кроме того, шестой выход первого регистра команд соединен со вторым входом нервой схемы модификаци;г

N

J

%

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал | 1980 |

|

SU868743A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Процессор ввода-вывода | 1979 |

|

SU798782A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

rn

EOQ

CO

CvJ

ci«

И

t

l-l

4i

l-

-5

-

C:,

J

Ч;

LJ

11

73

71

81

IB 79

77

76

75

83

86

85

84

Авторы

Даты

1975-12-15—Публикация

1973-02-28—Подача