.-.:

Изобретение относится к области автоматики и вычислитецьной техники и может быть испопъэовано в информа :ционно иэмервтельных и управляющих системах для формирования в виде ци4н рового кода производной частотно 41М пульсного сигнала..

Известно частотно- мпульбноё дифференцирующее устройство 1 J, содержащее блок возведения в куб, блок выделения разности пёриоабв, зпёмент И и счетчик результата.

Недостатком такого устройства является низкая точность дифференцирования сигйалоь.

Известно также дифференцирующее устройство 2 , содержащее блок управления, генератор опорной частоты, управляемые делители частоты, неуправляемый делитель частоты, счетчик периода, группы 9леЬ(1ентов И, счетчик результата и блок приращения периода.

Недостатком этого устройства является пониженное быстродействие..

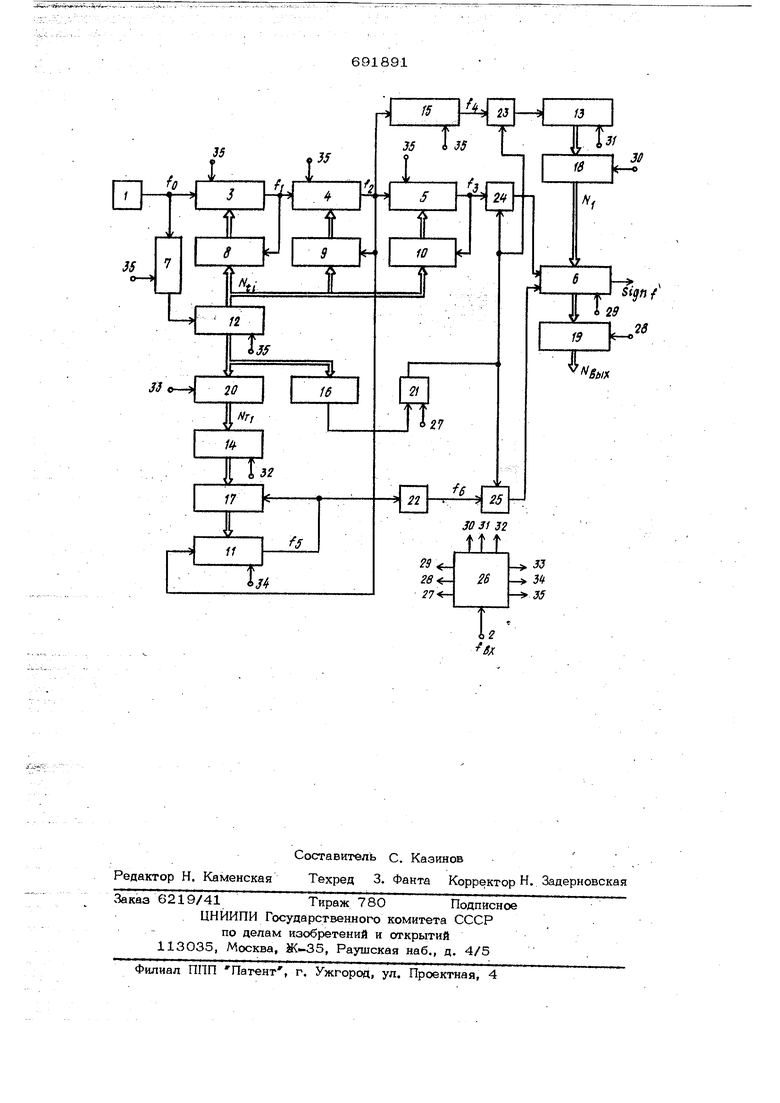

Наиболее близким к данному изобретвник) является тастготно-импульсное дифференцирующее ybtpOftCTBo 3 ; содержащее генератор опорной частоты, подключенный выходом к входу делителя частоты и к счетному входу первого счетчика, соединенного разрядными входами с выходами snoMeHiPOB И первой группы подключенньтх первым:и входами к выходу первого счетчика и счетному входу второго счетчика, соединенного разрядными входами с выходами элементов И группы, подключенныпс первыми входами к выходу второго счетчика, счетному входу третьего счетчика, соединённого разрядными. входак«и с выходами элемен;тов И третьей группы, и счетному входу четвертого счетчика, соединенного разрядными входами с выходами элемен:тов И четвертой группы, подключенных первыми входами к выходу четвертого счетчика, выход третьего счетчика соединен с первыми входами элементов И третьей группы, вторые входы которых 3 подключены к вторым входам элемонтов И первой и второй групп и к разрядным выходам пятого счетчика, соединенного счетным входом с выходом делителя час ТС1ТЫ, причем разрядные выходы шестого счетчика подключены к первым входам элементов И пятой группы, соединенных выходами с разрядными входами ревер- сивного счетчика результата, разрядные выходы которого подключены к первым входам элементов И шестой группы, а устШОвочные входы первого, второго, третьего, четвертого и пятого счетчиков вторые входы элементов И пятой и шее- , той групп и входь обнуления делителя частоты, реверсивного счетчика результата и шестого счетчика соединены с соответствующими выходами блока управления, подключенного входом к входной шине устройства, Недостатком этого устройства являет ся сложность конструктивной реализации понижающая надежность работы и не обе печивающая вьфавнивание коэффициентов пропорциональности составляющих кода в счетчике результата. Целью изобретения является упрощение устройства. Эт6 д6стигается тем, что в предлага емое устройство введены дешифратор, ре гйстр памяти, дополнительная группа эле ментов И, дополнительный делитель частоты, два триггера и три элемента И, подклйчённые первыми входами к выходу первого триггерав соединенного первым входом с выходом дешифратрра, под кгиочейнбго входами к разрядным выходам пятого счетчика и к первым входам элементов И дополнительной группы, выходы которых через регистр памяти подключены к вторым входам элементов И четвертой группы, соединенных первыми входами со счетным входом второго три гера, подключенного выходом к второму входу первого элемента И, выход которого соединен с суммирующим входом реверсивного счетчика рез1ультата, под- клю5енного вычитающим входом к выходу второго элемента И, соедйнённого вт рым входом с выходом третьего счетчика, счетный вход которого подключен через дополнительный делитель частоты к второму входу третьего элемента И, соед;иненного выходом со счетным входо шестого счетчика,причем вторые входы элементов И дополнительной группы, вто рой вход первого триггера и входы обнуления регистра памяти и дополнительOJ4кого делителя частоты гтодюпочергы к соответствующим выходам блока управления. На чертеже показана блок-схема предлагаемого устройства, которое содержит генератор опорной частоты I, входную шину 2, первый 3, второй 4 и третий 5 счетчики, реверсивный счетчик 6 результата, делитель частоты, первую 8, вторую 9 и третью 10 группы элементов И, . четвертый 11, пятый 12 и шестой 13 счетчики, регистр памяти 14, дополнительный делитель 15 частоты, дешифратор 16, четвертую 17, пятую 18 и шестую 19 группы элементов И, дополнительную группу 20 элементов И, первый 21 и второй 22 триггеры, первый 23, второй 24 и третий 25 элементы И, блок управления 26, 27 35-«Ь1ходы блока управления. Выход генератора 1. соединен со счетным входом счетчика 3. Выход счетчика 3соединён со счетным входом счетчика 4и подключен к первым входам элементов И первой группы 8, выходы которых соединены с поразрядными входами счетчика 3. Выход счетчика 4 подключен к счетным входам счетчиков 5 и 11, входу делителя частоты 15 и первым входам элементов И второй группы 9, выходы которых соединены с поразрядными входами счетчика 4. Выход счетчика 11 соединен с первыми входами элементов И четвертой группы 17, подключенных выходами к поразрядным входам счетчика 11 и подключен к счетному входу триггера 22. Первые входы элементов И группы 17 через регистр памяти 14 соединены с выходами элементов И дополнительной группы 20, первые входы которых подключены к поразрядным выходам счетчика 12 и входам дешифратора 16, выход которого соединен с первым входом триггера 21. Выход триггера 21 подключен к первым входам элементов И 23 24, 25. Второй вход элемента И 24, соединенного выходом с вычитающим входом реверсивного счетчика результата 6, подключен к выходу счетчика 5 и первым входам элементов И третьей группы 10. Вторые входы элементов И групп 8, 9, 1О соединены с поразрядными выходами счетчика 12. Выход делителя частоты 15 подключен к второму входу аде мента И 23, соединенному выходом со -счетным входом счетчика 13, поразрядные выходы которого подключены к первым входам элементов И пятой группы 18, соединенных выходами с поразрядными входами реверсивного счетчика 6, подключенного суммиру ющим входом к выходу элемента И 25, второй вход которого соединен с выходом триггера 22, и соединенного поразрядны ми выходами с первыми входами элементов И шестой группы 19. Выходы элеме тов И группы 19 подключены js выходной шине устройства. Выходы блока управления 26f соединенного входом с входной шиной И устройства, подключены следующим образом: выход 27 - к второму входу триггера 21, выход 28 - к вторым входам элементов И группы 19, выход 29 - к входу обнуления реверсивного счетчика 6, выход 30 - к вторым входам элементов И группы 18, выход 31 - к входу обнуления счетчика 13, выход 32 - к входу обнуления регистра памяти 14, выход 33 - к вторым входам элементов И группы 20, выход 34 - к становочному входу счетчика 11, выход 35 - к установочным 1входам счетчиков 3, 4, 5, 12 и входам обнуления делителей частоты 7 и 15. Устройство работает следующим образом. ;- ..-;. .; После поступления каждого импульса входной частоты в блоке управления 26 формируются сигналы, которые последовательно по выходу 27 устанавливают триггер 21 в положение, закрыёающее элементы И 23, 24, 25, по выходу 28 открывают группу элементов И 19 и код результата со счетчика 6 передается на вход устройства. Затем счётчик 6 сигналом по выходу 29 обнуляется ji в него через группу элементов -И 16, бткрйтую сигналом с выхода 30, заносйтсй код из счетчика 13, после чеГо счётчик 13 обнуляется сигналом по выходу 31 блока управления. Затем сигналом rip Bbixo ду 32 обнуляется регистр памяти 14 и в него через группу элементов И 20, от крытую сигналом с выхода 33, заносится код из счетчика 12. После этого в счётчике 11 сигналбм по выходу 34 блока управления устанавливается обратный код единицы (2-1, где п - число разрядов счетчика). Сигналом по выходу 35 обнуляются делители 7, 15, в счетчике 12 устанавливается код единицы, а в счетчиках 3, 4, 5 - обратный код единицы. После этого импульсы высокой частоты { с выхода 1 енератора 1, прошедшие через делитель частоты 7 с ко- эффициентом деления К, поступазрт на вуод счетчика 12, где они суммируются в промежутках времени между входными

691891 импульсами, равных текущим периодам Т- входной частоты 1, . В конце каждого периода входной частоты в счетчике 12 образуется код, пропорциональный заканчивающемуся периоду тг- -Т;Этот код перед установкой счетчика 12 в начальное положение переписывает- ся через группу элементов И 20 в предварительно очищенный регистр памяти 14, где хранится до окончания следующего периода. Первый импуль частоты {р вызывает переполнение счетчиков 3, 4, 5, выходные импульсы которых через соответствующие группы элементов 8, 9, 10 переписывают текущий код счетчика 12 в эти счетчики 3, 4, 5. При последующих переполнениях счет- чиков 3, 4, 5 этот процесс повторяется. На выходе счетчика 3 формируется частота f . К Ч Т 1 -. обратно пропорциональная времени t; , прошедшему с начала текущего периода. На выходе счетчика 4 формируется частота J Vii, обратно пропорциональная квадрату времени t; . На выходе счетчика 5 форми- руется частота f обратно пропорциональная кубу времени Импульсы частоты In с выхода счетчика 4 через делитель частоты 15с коэффициентом деления K,v пропорциональным минимальному периоду Т j входной частоты, поступают че- рез элемент И 23 на вход счетчика 13, где эти Импульсы суммируются за время, на которое открывается элемент И 23. Импульсы с выхода счетчика 4 поступают также на вход счетчика 11, который совместно С регистром памяти 14 и группой элементов И 17 образует управляемь1й делитель частоты с коэффициентом деления, равным коду в регистре 14 и пропорциональным закончившемуся периоду входной частоты. Частота {. на выходе счетчика 11 равна Импульсы частоты i, с помощью триг гера 22 делятся па пва и выходная час тота i этого триггера через элемент И 25 поступает на суммирующий вход реверсивного счетчика результата 6, на вычитающий вход которого поступают импульсы с частотой trj с выхода счетчика 5. Элементы И 23-25 открывают- ся на временной интервал, равный разности ( Т,- - ) между текущим и минимальным периодом входной частоты Этот интервал формируется с помощью триггера 21, который устанавливается в положение, при котором открываются элементы И 23 - 25, в момент времег ни, когпа код в счетчике 1.2 достигает величины : MT . -. т , пип К mm ) и возвращается в исходное положение сигналом 27 блока упра1вяёния по окон- чанию текущего периода и приходу следующего .импульса входной частоты, .Переключение триггера 21 по достиженшо кода счетчика 21 величины NT--, осуществляется дешифратором 16. / За время предыдущего периода Тв счетчике 12 формируется код, пропорциональный этому периоду, который пере писывается в регистр 14. За время . Т, - Т 1 в счетчике 13 сформируется код N; У /.... . ,. . ,Ъ ,. : . , : .4 Wfmdx- J; , maKv-mnv / mio -о который пропорционален Произведению ;.. максимальной частоты imnu следования входных импуйьсов .на разность .между максимальным и мгновенньп текущим значением входной частоты, соответствую щей предшествующему периоду. Этот код NI после окончания предшествующего периода переписывается через группу элементов И 18 в реверсивный счетчик 6, в котором в течение интервала Т -Тг) равного разности между последующим Tji и-минимальным периодом входной частоты, будет проходить вычитание из кода N, импульсов частоты f и суммирование импульсов частоты , .В конце последующего периода То в реверсивном счетчике результата будет сформирован выходной код Njbix (f,-i,) imtm n° 1в который пропориионален производной по времени входного частотно-импульсного . сигнала. При изменении знака производной код в счетчике 6 уменьшается до нуля и меняет свой знак. При этом срабатывает триггер знака счетчика 6 (на чертеже не показан), меняющий направление счёта импульсов в этом счетчике на обратное и выдающий знак минус на выход устройства. При этом импульсы частоты 1, начинают суммироваться, а частоты it вычитаться. Одновременно с формированием кода в счетчике результата 6, в счетчике 12 формируется код К пропорциональный текущему nepHoliy Тт в счетчике 13 код/, пропорциональный произведению максимальной частоты на разность между максимальной и соответствующей текущему. периоду Tj . Таким образом после окончания периода 7 устройство готово к образованию нового значения кода в счетчике результата 6, которые будет происходить в последующем периоде. Предлагаемое устройство, благодаря объединению ряда операций, не использует в отличие от прототипа частотомер мгновенных значений, блок измерения лериода и блок формирования минимального периода в блоке управления; Это приводит к упрощению конструктивной реализации Ч1астотно-импульсного дифференцирующего устройства. В частности, в предлагаемом устройстве используются 10 счетчиков импульсов вместо 17 счетчиков в прототипе. Формула изобретения Частотно-импульсное дифференцирующее устройство, содержащее генератор опорной частоты, подключенный выходом к входу делителя частоты и к счетному входу первого счетчика, соединенного разрядными входами с выходом элементов И первой группы, подключенных первыми входами к выходу первого счетчика и счетному входу второго счетчика, соединенного разрядными входами с выходами элементов И второй группы, подключеннь1х первыми входами к выходу второго счетчика, счетному входу третьего счетчика, соединенного разрядными входами с выходами элементов И третьей группы, и счетному входу четвертого счетчика, соединенного разрядными входа ми элементов И четвертой группы, подключенных первыми входами к выходу четвертого счетчика, выход третьего счетчика соединен с первыми входами элементов И третьей группы, вторые входы которых подключены к вторым входам элементов И первой и второй групп и к разрядным вь1ходам пятогх счетчика, соединенного счетным входом с выходом делителя частоты, причем разрядные выходы шестого счетчика подключены к первым входам элементов И шггой групгоы, соединенных вьтходами с раарядными входами реверсивного счетчика результата, разрядные выходы которого подхлю чены к nepBbiM вхопвм эпементо И шесы. той группы, а устешимйочныё взьоДы йервогЬ, второго, третьего чвтьвртб1х) и пятого счетч|йс6в,. втЬрыё входы яё ёнтов И пятой «г шестой групп и бэвдйы обну пения-делитвйя астйгы (ЙЙй(16 :/ счетчика pedynbTiaTa и йгёстбгЬ ЬЧёТчййа соединень с, ро уГ1№тстйутой(ишBfe| блока управлений; I№tWЙю №нйoi o В к входной щййё устройства, от ji и ч а ю е ё с я тёк, о, с ДёлЬк) упрощения устройства, В йёго введ0нЬ1 дешй чзаТор, {зегйстр йамйтй, допйяни1;«;п ная группа элеметров И, дополйитейь кыЙ делитель частоты, Два Триггера и три элемента И, под Еслюченныё nejpBbiMk Входами к выходу первого триггера, соединённого первым входом с Выходом дёшйф ратора, подключенного вхбдами К рааряД« ным в)ь1ходам пятого счетчика и к пер61 вым входам элементов И дополнительной группы, выходы которых через i регистр памяти подключены к вторым входам элементов И четвертой груцпы, соединенных первыми входами со счетным входом второго триггера, подключенного выходом к второму входу первого элемента И, выход которого соединен с суммирующим входом реверсивного счетчика результата, подключенного вычитающим входом к выходу второго элемента И, соединенного вхсяоМ с выходом третьего счетчика, счетный вход которого подключен ч(в1зеэ дополнительный делитель час5Тоты к BTOjpoMy Взбоду третьего элемента И, соед1гае1Ыо О вЬпсрдом со ЬчетньЫ вхЬдой шестогб счётчежа, причем Bjcbflfii йэДШгбв И дополнительной группы, второй вход nejiBoro трштера и. Врьодьт ЬбяупёнЙ памяти и допй|Цйи1гельй) д&питеп:я подклю екЫ К cooTBe|citByiotmiiMi вШЬдай блокаynpaBjieisHe : , ... ---f.-1- : иЫфорл принятые во вшмаЩё при 9(спёртизе 1.Авторское свидетельство CCCiP № 399S60, кл. G 06F 7/38, 1971. 2.Заявка № 2395060/24, кл, в Об Э З/рб, 19716, по которой принято решение о Шдачё авторского свидетельства, 3.Заявки М 2119484/24, кл, G 0667/18, 1975, по которой принято решение о вьщаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU723599A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Устройство для суммирования частотно-импульсных сигналов | 1977 |

|

SU708361A1 |

| Устройство цифрового задания частоты следования импульсов | 1976 |

|

SU641455A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1084852A1 |

| Устройство для измерения скорости вращения асинхронного электродвигателя | 1977 |

|

SU690390A1 |

Авторы

Даты

1979-10-15—Публикация

1977-06-02—Подача