Изобретение относится к вычислительной технике и может быть использовано при построении устройств формирования адресов команд и данных в универсальных и специализированных вычислительных машинах.

Целью изобретения является расширение функциональных возможностей за счет обработки чисел расширенного

34, третьего 35 и четвертого 36 эле ментов И. Первый тактовьй вход 20 блока 3 синхронизации соединен с вторыми входами первого 33, второго 34 и третьего 35 элементов И и с тактирующим входом дешифратора 32, выходы которого образуют первую группу 28 синхронизирующих выходов блока 3 синхронизации. Выходы треформата без снижения производительно- Ю тьего 35 и/четвертого 36 элементов

сти устройства и упрощения йрограм- мирования за счет хранения индексов при вьтолнении различных участков программы.

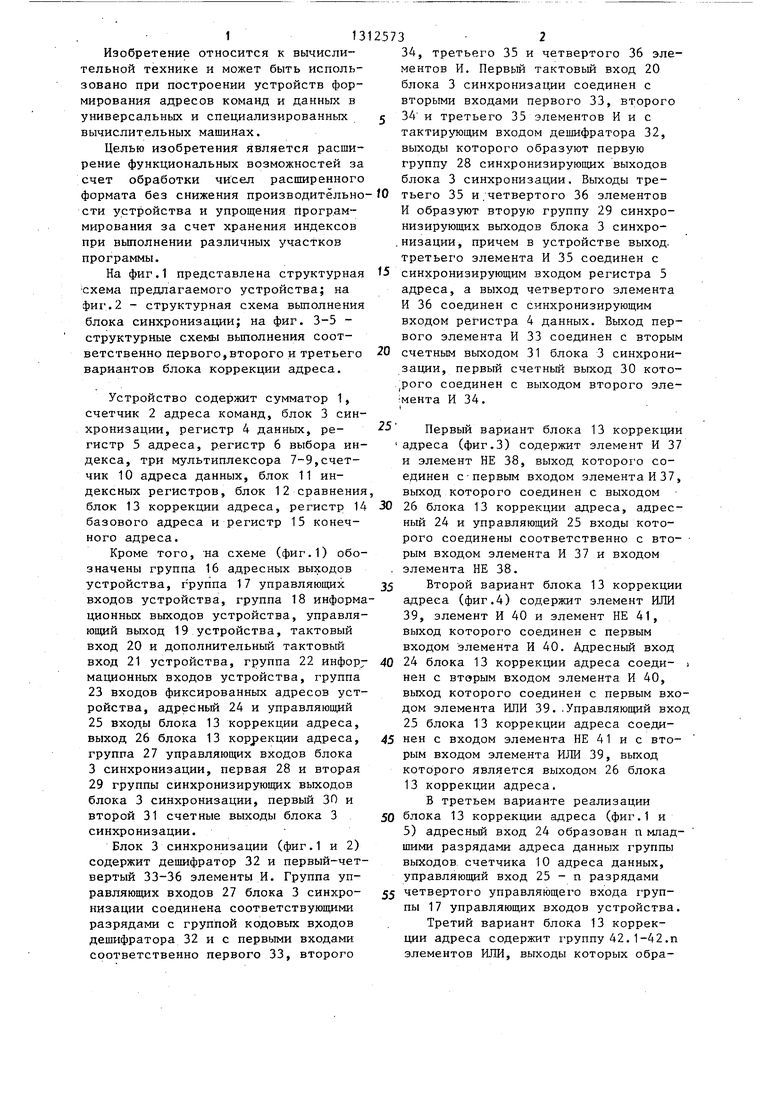

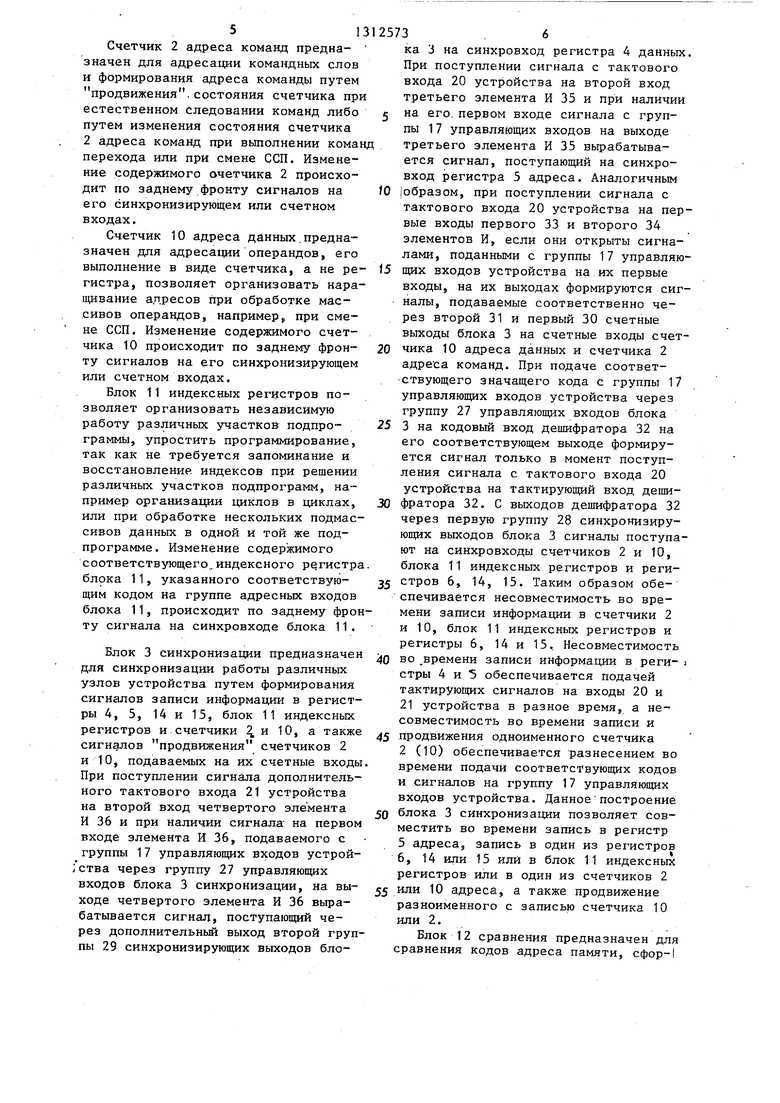

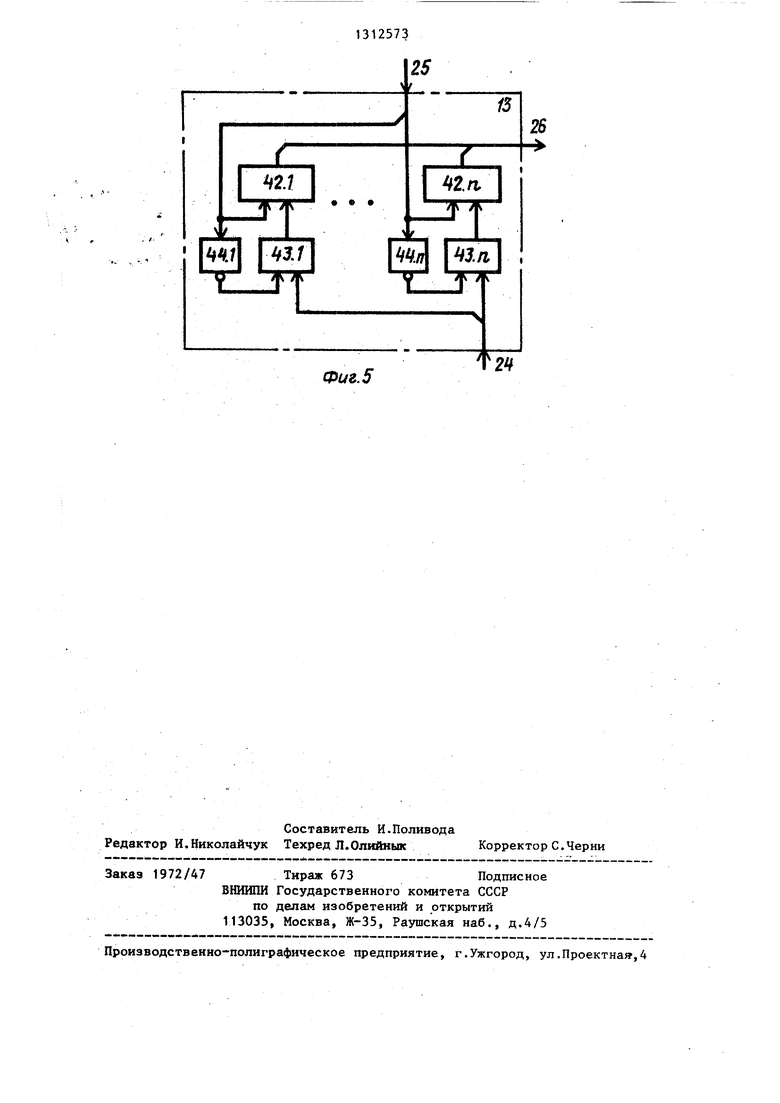

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - структурная схема вьшолнения блока синхронизации; на фиг. 3-5 - структурные схемы выполнения соответственно первого,второго и третьего вариантов блока коррекции адреса.

Устройство содержит сумматор 1, счетчик 2 адреса команд, блок 3 синхронизации, регистр 4 данных, регистр 5 адреса, регистр 6 выбора ин- декса, три мультиплексора 7-9,счетчик 10 адреса данных, блок 11 индексных регистров, блок 12 сравнения блок 13 коррекции адреса, регистр 14 базового адреса и регистр 15 конечного адреса.

Кроме того, на схеме (фиг.1) обозначены группа 16 адресных выходов устройства, г руппа 17 управляющих входов устройства, группа 18 информационных выходов устройства, управляющий выход 19 устройства, тактовый вход 20 и дополнительный тактовый вход 21 устройства, группа 22 инфорг мационных входов устройства, группа 23 входов фиксированных адресов устройства, адресный 24 и управляющей 25 входы блока 13 коррекции адреса, выход 26 блока 13 коррекции адреса, группа 27 управляющих входов блока 3 синхронизации, первая 28 и вторая 29 группы синхронизирующих выходов блока 3 синхронизации, первый 30 и второй 31 счетные выходы блока 3 синхронизации.

Блок 3 синхронизации (фиг.1 и 2) содержит дешифратор 32 и первый-чет- вертый 33-36 элементы И. Группа управляющих входов 27 блока 3 синхро- низации соединена соответствуюш ми разрядами с группой кодовых входов дешифратора 32 и с первыми входами соответственно первого 33, второго

34, третьего 35 и четвертого 36 элементов И. Первый тактовьй вход 20 блока 3 синхронизации соединен с вторыми входами первого 33, второго 34 и третьего 35 элементов И и с тактирующим входом дешифратора 32, выходы которого образуют первую группу 28 синхронизирующих выходов блока 3 синхронизации. Выходы тре0

5

5

0

5 0 5 0

5

И образуют вторую группу 29 синхро- низиpyюшJix выходов блока 3 синхро- .низации, причем в устройстве выход, третьего элемента И 35 соединен с синхронизирующим входом регистра 5 адреса, а выход четвертого элемента И 36 соединен с синхронизирующим входом регистра 4 данных. Выход первого элемента И 33 соединен с вторым счетным выходом 31 блока 3 синхронизации, первый счетный выход 30 кото- |РОГО соединен с выходом второго элемента И 34.

I

Первый вариант блока 13 коррекции адреса (фиг.З) содержит элемент И 37 и элемент НЕ 38, выход которого соединен с-первым входом элемента И 37, выход которого соединен с выходом 26 блока 13 коррекции адреса, адресный 24 и управляющий 25 входы которого соединены соответственно с вто- - рым входом элемента И 37 и входом элемента НЕ 38.

Второй вариант блока 13 коррекции адреса (фиг.4) содержит элемент ИЛИ 39, элемент И 40 и элемент НЕ 41, выход которого соединен с первым входом элемента И 40. Адресньш вход

24блока 13 коррекции адреса соеди- нен с вторым; входом элемента И 40, выход которого соединен с первым входом элемента ИЛИ 39..Управляющий вход

25блока 13 коррекции адреса соединен с входом элемента НЕ 41 и с вторым входом элемента ИЛИ 39, выход которого является выходом 26 блока 13 коррекции адреса.

В третьем варианте реализации блока 13 коррекции адреса (фиг.1 и 5) адресный вход 24 образован п млад- шими разрядами адреса данных группы выходов счетчика 10 адреса данных, управляющий вход 25 - п разрядами четвертого управляющего входа группы 17 управляюш 1х входов устройства.

Третий вариант блока 13 коррекции адреса содержит группу 42.1-42.п элементов ИЛИ, выходы которых обра-3 13

зуют выходы 26 блока 13 коррекции адреса, группу 43.1-43.п элементов И, выходы которых соединены с первыми входами элементов ИЛИ 42.1-42.п группы, и группу 44.1-44.п элементов НЕ, выходы которых соединены с первыми входами элементов И 43.1-43.п группы. Адресный вход 24 блока 13 коррекции адреса соединен соответствующими разрядами с вторыми входами элементов И 43.1-43.п группы. Управляющий вход 25 блока 13 коррекции адреса соединен соответствующими разрядами с входами элементов НЕ 44.1-44.П группы и с вторыми входами элементов ИЛИ 42.1-42.п группы.

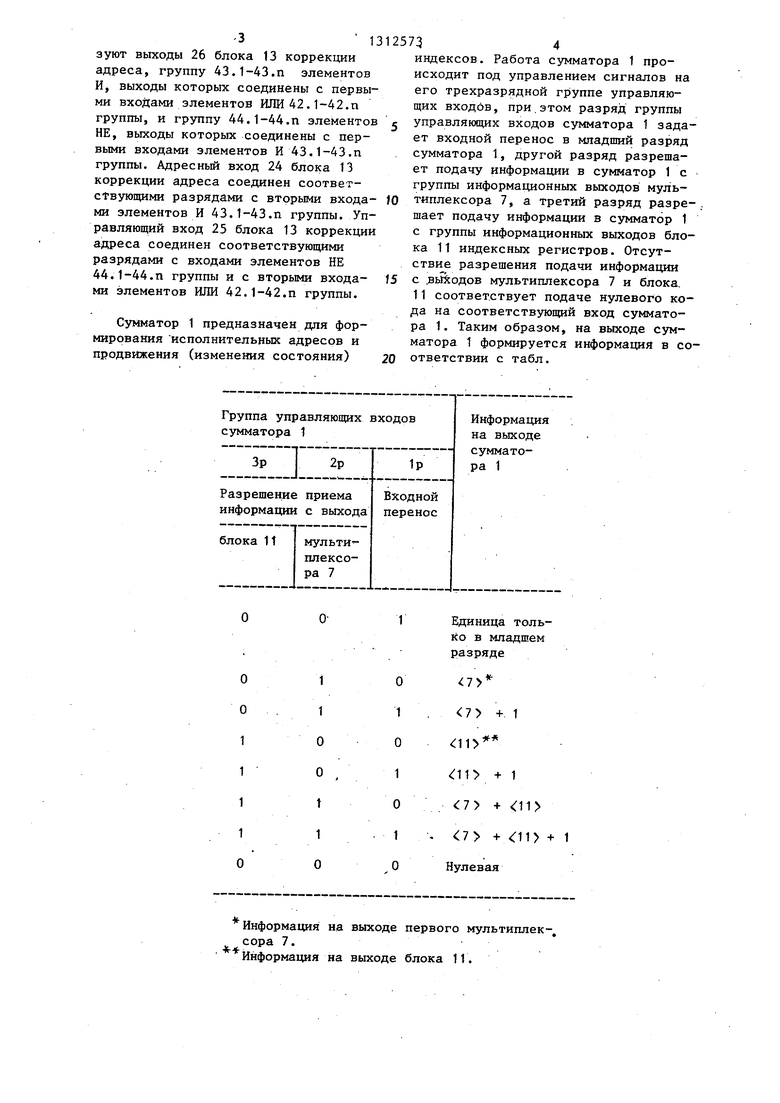

Сумматор 1 предназначен для формирования исполнительных адресов и продвижения (изменения состояния)

Группа управляющих входов сумматора 1

. -« Информация на выходе первого мультиплек-, сора 7. Информация на выходе блока 11.

734

индексов. Работа сумматора 1 происходит под управлением сигналов на его трехразрядной группе управляющих входов, при.этом разряд группы

управляющих входов сумматора 1 задает входной перенос в младший разряд сумматора 1, другой разряд разрешает подачу информации в сумматор 1 с группы информационных выходов мультиплексора 7, а третий разряд разрешает подачу информации в сумматор 1 с группы информационных выходов блока 11 индексных регистров. Отсутствие разрешения подачи информации

с .вь&одов мультиплексора 7 и блока, 11 соответствует подаче нулевого кода на соответствующий вход сумматора 1. Таким образом, на выходе сумматора 1 формируется информация в соответствии с табл.

Информация

на выходе

Единица только в младшем разряде

513

Счетчик 2 адреса команд предка- значен для адресации командньк слов и формирования адреса команды путем продвижения, состояния счетчика при естественном следовании команд либо путем изменения состояния счетчика 2 адреса команд при вьтолнении коман перехода или при смене ССП. Изменение содержимого очетчика 2 происходит по заднему фронту сигналов на его синхронизирующем или счетном входах,

Счетчик 10 адреса дйнных.предназначен для адресации операндов, его выполнение в виде счетчика, а не регистра, позволяет организовать наращивание адресов при обработке массивов операндов, например, при смене ССП. Изменение содержимого счетчика 10 происходит по заднему фронту сигналов на его синхронизирующем или счетном входах.

Блок 11 индексных регистров позволяет организовать независимую работу различных участков подпро- граммь, упростить программирование, так как не требуется запоминание и восстановление индексов при решении различных участков подпрограмм, например организации циклов в циклах, или при обработке нескольких подмас- сивов данных в одной и той же подпрограмме . Изменение содержимого соответствующего..индексного регистра блока 11, указанного соответствующим кодом на группе адресных входов блока 11, происходит по заднему фронту сигнала на синхровходе блока 11,

Блок 3 синхронизации предназначен для синхронизации работы различных узлов устройства путем формирования сигналов записи информации в регистры 4, 5, 14 и 15, блок 11 индексных регистров и счетчики и 10, а также сигналов продвижения счетчиков 2 и 10, подаваемых на их счетные входы При поступлении сигнала дополнительного тактового входа 21 устройства на второй вход четвертого элемента И 36 и при наличии сигнала на первом входе злемента И 36, подаваемого с группы 17 управляющих входов устрой- , ства через группу 27 управляющих входов блока 3 синхронизации, на выходе четвертого элемента И 36 вьфа- батывается сигнал, поступающий через дополнительный выход второй группы 29 синхронизирующих выходов бло36

ка 3 на синхровход регистра 4 данных. При поступлении сигнала с тактового входа 20 устройства на второй вход третьего элемента И 35 и при наличии

на его. первом входе сигнала с группы 17 управляющих входов на выходе третьего элемента И 35 вырабатывается сигнал, поступающий на синхровход регистра 5 адреса. Аналогичным

образом, при поступлении сигнала с тактового входа 20 устройства на первые входы первого 33 и второго 34 элементов И, если они открыты сигналами, поданными с группы 17 управляющих входов устройства на их первые входы, на их выходах формируются сигналы, подаваемые соответственно через второй 31 и первый 30 счетные выходы блока 3 на счетные входы счетчика 10 адреса данных и счетчика 2 адреса команд. При подаче соответствующего значащего кода с группы 17 управляющих входов устройства через группу 27 управляющих входов блока

3 на кодовый вход дешифратора 32 на его соответствующем выходе формируется сигнал только в момент поступления сигнала с тактового входа 20 устройства на тактирующий вход, дешифратора 32. С выходов дешифратора 32 через первзпо группу 28 синхронизиру- юпщх выходов блока 3 сигналы поступают на синхровходы счетчиков 2 и 10, блока 11 индексных регистров и регистров 6, 14, 15. Таким образом обеспечивается несовместимость во времени записи информации в счетчики 2 и 10, блок 11 индексных регистров и регистры 6, 14 и 15.. Несовместимость

во времени записи информации в реги- i стры 4 и 5 обеспечивается подачей тактирующих сигналов на входы 20 и 21 устройства в разное время, а несовместимость во времени записи и

продвижения одноименного счетчика 2 (10) обеспечивается разнесением во времени подачи соответствующих кодов и сигналов на группу 17 управляющих входов устройства. Данное построение

блока 3 синхронизации позволяет совместить во времени запись в регистр 5 адреса, затись в один из регистров 6, 14 или 15 или в блок 11 индексных регистров или в один из счетчиков 2

или 10 адреса, а также продвижение разноименного с записью счетчика 10 или 2.

Блок 12 сравнения предназначен для сравнения кодов адреса памяти, сфор-1

71

мированного на группе 16 адресных выходов устройства, и конечного адреса программы или адреса необходимой ячейки памяти, хранящей данные, заданного в регистре 15 конечного адреса, и для выработки сигнала, подаваемого на управляющий выход 19 устройства при совпадении этих адресов .

Блок 13 коррекции адреса предназначен для формирования последовательности адресов отдельных частей чисел, разрядность которых превышает формат данных устройства и кратна этому формату. При этом в устройстве адрес числа задается согласно целочисленной границе расположения таких чисел (например, для чисел двойного формата задается четный адрес). Коррекция адреса заключается в последовательной выработке адресов отдельных частей чисел, начиная с адреса хранения ее младшей части. Например, для чисел двойного формата сначала должен быть выработан нечетный адрес, т.е. в младший разряд адреса должна подформироваться единица при обращении за младшей частью числа и ноль при обращении за старшей частью числа.

Первый вариант блока 13 коррекции адреса обеспечивает работу устройства следующим образом. После занесения исполнительного (четного) адреса числа в счетчик 10 адреса данных производится продвижение его содержимого на единицу (вырабатьшается нечетньй адрес младшей части числа двойного формата). Затем происходит выборка этого числа из памяти, так как на протяжении всего времени работы устройства сигнал на управляю - щем входе 25 блока 13 коррекции адреса отсутствует, поэтому элемент И 37 открыт и младший разряд адреса с выхода счетчика 3 адреса данных через элемента И 37 блока 13 на вход мультиплексора 8 передается без изменения. Далее на третьем управляющем входе группы 17 управляющих входов вырабатывается сигнал, поступающий на вход элемента НЕ 38, который запрещает прохождение сигналов через элемент И 37, что обеспечивает формирование четного адреса старшей части числа двойного формата. Таким образом, выборка числа двойного формата с использованием первого

12573-8

варианта блока 13 коррекции адреса выполняется за четыре машинных цикла: загрузка исполнительного (четного) адреса числа в счетчик 10 ад- реса данных; продвижение содержимо счетчика 10 на единицу; выборка млашей части числа; -блокировка передачи единицы младшего разряда счетчика 10 через второй коммутатор и выЮ борка старшей части числа.

Уменьшение времени выборки числа двойного формата на один машинный цикл обеспечивает второй вариант по строе.ния блока 13 коррекции адреса,

J5 при этом устройство работает следующим образом. После занесения исполнительного (четного) адреса числа в счетчик 10 на третий управляющий вход группы 17 управляющих входов

20 устройства подается сигнал, которьй через управляющий вход 25 блока 13, элемент ИЛИ 39 поступает в младший разряд второй группы адресных входов мультиплексора 8, т.е. формируется .

25 нечетный адрес числа, по которому производится выборка младшей части этого числа. Затем сигнал на третьем управляющем входе группы 17 управляющих входов устройства снимает30 ся и производится выборка старшей части числа, поскольку содержимое счетчика 10 не изменялось. Несмотря на наличие дополнительного элемента ИЛИ 39 во втором варианте построения

2 блока 13 коррекции адреса, он является более предпочтительным, поскольку увеличивает производительность устройства.

Третий вариант построения блока 0 13 коррекции адреса отличается от второго варианта только тем, что вместо одного младшего разряда адрес корректируются п младших разрядов, причем коррекция производится после- 5 довательно цикл за циклом выработкой кодов на управляющем входе блока 13 от максимального до минимального нулевого кода. Третий вариант блока

13 коррекции адреса используется в 50

R тех случаях , когда logj 1/ где.

г - формат данных, передаваемых уст- ройством; R - формат числа увеличенной разрядности.

Регистры 4 данных и 5 адреса выполнены в виде регистров-защелок, используемых для временного хранения

913

информации. Передача информации с входов на выходы этих регистров производится при подаче сигнала на их синхровходы, а запоминание (защелка) информации осуществляется в момент снятия сигнала на синхровходах буферных регистров 4 данных и 5 ад- :реса.

Регистр 6 выбора индекса предна- значен для выбора соответствующего индексного регистра в блоке 11 индексных регистров. При подаче кода номера индексного регистра на группу адресных входов блока 11 индексных регистров его содержимое подается на группу информационных выходов блока 11, а при подаче сигнала (по его заднему фронту) на сихровход блока 11 в указанный регистром 6 выбора индекса индексньй регистр записывается информация, поданная на группу информационных входов блока 11.

Регистр 14 базового адреса предназначен для разделения всего объема памяти на отдельные базовые области, объем которых определяется разрядностью группы выходов мультиплексора 8 или счётчиков 2 и 10 адреса команд и данных. Таким образом, суммарная разрядность группы 16 адресных выходов устройства равна сумме разрядностей выхода коммутатора 8 и регистра 14 базового адреса.. Позто му адресация каждой указанной базовой области памяти осуществляется так, что после максимального адреса ячейки этой области (например, при продвижении адресов области в счетчиках 2 адреса команд и 10 адреса данных) указьшается начальньй адрес ячейки этой же области, а не начальный адрес следующей по порядку базовой области. Доступность записи в регистр 14 базового адреса только операционной системы обеспечивает не только распределение независимых областей памяти различным подзадачам, но также защиту памяти одних подзадач от вмешательства со стороны других.

Регистр 15 конечного адреса предназначен для задания конечного адреса подпрограммы, по достижении ко4 торой устройство должно вырабатывать управляющий .сигнал, например, в систему прерывания процессора. Разрядность регистра 15 конечного адреса равна суммарной разрядности регистра

310

14 базового адреса и группы выходов второго мультиплексора 8.

Запись информации в регистры 6 выбора индекса, 14 базового адреса

и 15 конечного адреса, подаваемой на их группы информационных входов с группы информацоинных выходов мультиплексора 7, осуществляется по заднему фронту сигналов, подаваемых на

синхровходы регистров б, 14 и 15.

Мультиплексор 7 предназначен для выдачи информации на группу 18 информационных выходов устройства, первую группу информационных входов сумматора 1, группу информационных вхо- дов 11 индексньк регистров, регистра 6 выбора индекса, регистра 14 базового адреса и регистра 15 конечного адреса с групп информационных входов регистров 4 данных и 5 адреса в зависимости от наличия сигнала на первом управляющем входе группы 17

управляющих входов устройства.

I

Мультиплексор 8 предназначен для выдачи информации с выхода счетчика 2 адреса команд или выходов счетчика 10 адреса данных и блока 13 коррекции адреса на группу 16 адресных

выходов устройства в зависимости от наличия сигнала на втором управляющем входе группы 17 управляющих входов устройства.

Мультиплексор 9, в зависимости от

кода, подаваемого на группе его управляющих входов с второй подгруппы управляющих входов группы 17 управляющих входов устройства, осуществляет передачу информации на группы информационных входов регистров 4 данных и 5 адреса со следующих источников: с групп информационных выходов сумматора 1, регистра 14 базового адреса или регистра 15 конечного адреса, группы выходов счетчика 2 адреса команд, а также с группы 22 информационных входов устройства или группы 23 фиксированных адресов устройства.

Устройство для формирования адреса команд и данных работает следующим образом.

Изменение содержимого счетчиков и регистров устройства происходит

под воздействием синхросигналов, вы- рабатьгваемых блоком 3.

В режиме выборки команды содержимое счетчика 2 адреса команд, указывающее адрес очередной команды, чеП. 13

рез мультиплексор 8 передается на группу 16 адресных выходов, а командное слово с выхода памяти через группу 22 информационных входов устройства и мультиплексора 9 подается на регистр 4 данных. Запомненное в регистре данных командное слово через мультиплексор 7 подается на группу 18 информационных выходов устройства причем поле командного слова, указывающее номер индексного регистра в блоке 11, для формирования в дальнейшем исполнительного адреса данных записывается в регистр 6 выбора индекса. Содержимое счетчика 2 адреса команд увеличивается на единицу для формирования адреса очередной команды либо адреса смещения (С) или непосредственного операнда (I). Если командное слово имеет короткий формат, например RR или RX + + 1 (RX + 1 - режим, при котором исполнительным адресом данных является содержимое индексного регистра,, увеличенное на единицу), на этом выборка команды заканчивается. Если командное слово имеет длинный формат например RX или RI, происходит выполнение второго цикла режима выборки команды в котором по содержимому продвинутого значения счетчика 2 адреса числа выбирается непосредственный операнд I в режиме RI либо смещение С в режиме RX, которые записываются в регистр 5 адреса и перезаписываются в счетчик 1.0 адреса данных, а также запоминаются в регистре 4 данных и вьщаются через мультиплексор 7 на группу 18 информационных выходов устройства, при этом содержимое счетчика 2 адреса команд продвигается на единицу. На этом выполнение режима выборки команды заканчивается.

В режимах формирования исполнительных адресов операндов, которые следуют за режимом выборки команд, устройство работает следующим образом.

При прямой адресации исполнительным адресом является смещение С, записанное в счетчике 10 адреса данных поэтому этот адрес через мультиплексор 8 подается на группу 16 адресных выходов устройства. Выбранные из памяти данные через группу 22 информационных входов устройства и мультиплексор 9 поступают и запоминают312

ся в регистре 4 данных, откуда через мультиплексор 7 устройства передаются на группу 18 информационных выхо дов устройства.

при адресации с индексацией ис- полнительньй адрес формируется как сумма смещения С (запомненного в регистре 4 данных и переданного на первую группу информационных входов сумматора 1) и содержимого индексного регистра, адресуемого содержимым регистра -6 выборки индекса и поступающего на вторую группу информационных входов сумма- тора 1. В этом случае на второй и третий разряды группы управляющих входов сумматора 1 подаются сигналы, разрешающие подачу информации с выходов мультиплексора 7 и блока 11 индексных регистров. В этом случае возможны два варианта формирования исполнительного адреса: при нулевом значении первого разряда группы управляющих входов сумматора 1 испол- нит щьный адрес равен сумме смещения и соответствующего индекса, а при единичном значении - сумме сме- щения, соответствующего индекса и

единицы 1падшего разряда. Сформиро- ванный на выходе сумматора 1 испол- нительный- адрес данных через мультиплексор 9 записывается в регистр 5 адреса и перезаписывается в счетчик 10 адреса данных. В следующем цикле работы устройства происходит выборка данных как при прямой адресации.

При необходимости передачи массивов данных устройство позволяет взамен выполнения хдаклической подпро- граммы осуществить передачу массива данных одной командой, что сокращает объем памяти программ и увеличивает производительность устройства. В этом случае формирование исполни- тельного адреса первого операнда формируется аналогично режиму адресации с индексацией, причем в конце цикла выборки первого операнда массива содержимое счетчика 10 адреса данных продвигается на единицу, формируя адрес второго операнда, после выборки которого содержимое счетчика 10 адреса данных продвигается на единицу, и так далее до окончания передачи всего массива данных. Каждый раз при выборке очередого операнда он поступает в регистр данных и выдается на группу 18 нформационных выходов устройства.

13131

При «обработке массивов данных, когда после выборки очередного операнда массива следует команда его преобразования, используется режим RX + 1. В этом случае исполнительный адрес операнда формируется следующим образом. После выборки командного слова в регистре 6 выбора индекса указан номер индексного регистра блока 11, в котором хранится адрес, на единицу меньпшй адреса очередного операнда, поэтому в устройстве на группу управляющих входов сумматора 1 подается код с единицами в первом и третьем разрядах и нулем во втором разряде. Таким образом на выходе сумматора 1 формируется адрес очередного операнда, который через муль- типлексор 9 записывается в регистр 5 адреса и перезаписывается в счетчик 10 адреса данных. Кроме того, данньй адрес с выхода сумматора 1 подается на группу информационных входов блока 11 индексных регистров и записывается в соответствующий ин- дексньй регистр, номер которого указан в ,регистре 6 выбора индекса. В следующем цикле работы устройства происходит выборка операнда из памяти аналогично описанному режиму прямой адресации.

Ч

При решении задач классификации данных возникает необходимость обработки массивов данных, адреса опёран дов которых отличаются не на единицу младшего разряда, как в режиме RX+1, а на величину Л или на единицу большую л , причем значение л для очередного операнда массива в общем случае не равно л для предьщущего операнда массива. При формировании исполнительного адреса операнда в этом случае по окончании выполнения режима выборки команды в регистре 4 данных находится смещение С, которое в данном случае является величиной

д.. Поэтому в данном случае в первом цикле выборки операнда по указанному закону значение д. через мультиплексор 7 подается на первую группу информационных входов сумматора 1 а значение адреса предыдущего операн да с соответствующего индексного регистра, номер которого указан в регистре 6 выбора индекса, поступает на вторую группу информационных входов сумматора 1. На второй и третий разряды группы управляющих входов

57314

сумматора 1 подаются единичные сигналы, разрешающие подачу в сумматор 1 содержимого регистра 4 данных, по- ;ступающего на его вход через мульти5 плексор 7, и содержимого соответствующего индексного регистра, поданного на группу информационных выходов блока 11. В этом случае возможны два варианта формирования исполнительного адреса: при нулевом значении первого разряда группы управляющих входов сумматора 1 исполнитель-, ный адрес равен сумме д- и соответствующего индекса, а при единичном

J5 значении - сумме л,-, соответствующего индекса и единицы младшего разряда. Сформированньш на выходе сумматора 1 исполнительный адрес операнда через) мультиплексор 9 записы0 вается в регистр 5 адреса и перезаписывается в счетчик 10 адреса данных. Кроме того, данный адрес с выхода сумматора 1 подается на группу информационных входов блока 11 ин-/

5 дексных регистров и записывается в соответствующий индексный регистр, номер которого указан в регистре 6 выбора индекса. В следующем цикле работы устройства происходит выборка

30 операнда из памяти аналогично.режиму прямой адресации.

В режиме гщресации двойных слов исполнительный адрес операнда, сформированный и записанный в счетчик 10 35 адреса данных, например, аналогично прямой адресации или адресации с индексацией, является четным. Последовательная выборка младшей части и старшей части двойного слова и пере- 40 дача их с группы 22 информационных входов устройства через мультиплексор 9, регистр 4 данных и мультиплексор 7 на группу 18 информационных выходов устройства происходит

45 аналогично описанному при рассмотрении назначения и работы блока 13 коррекции адреса.

I

В режиме смены ССП при выходе на

50 прерывание программы по окончании

исполнения очередной команды устрой- ство работает следующим образом. Фиксированный адрес зоны хранения старых и новых ССП соответствующего

55 класса прерывания подается через группу 23 входов фиксированных адресов устройства, мультиплексор 9, регистр 5 аДреса и записывается в счетчик 10 адреса данных, с которого

выдается на группу 16 адресных выходов устройства через мультиплексор 8. В качестве слов ССП, сменяемых при прерывании, используется,например, регистр 15 конечного адреса, регистр 14 базового адреса и счетчик 2 адреса команд. Содержимое этих слов ССП последовательно передается через мультиплексор 9, регистр 4 данных и мультиплексор 7 на группу 18 информационных выходов устройства, а их адреса формируются в счетчике 10 адреса данных продвижением его содержимого на единицу каждый раз при пе зедаче старых слов ССП и приеме новых. При необходимости запоминания состояния индексных регистров и их смень при прерывании программы это производится после смены ССП по командам. При этом в командах указывается номер индексного регистра в блоке 11, подлежащего запоминанию или смене информации. При запоминани

20 мируется одним из описанных способо записывается в счетчик 10 адреса да ных и передается через второй мультиплексор 8 на группу 16 адресных выходов устройства, а содержимое со

состояния соответствующего индексного регистра его содержимое с выхода 25 ответствующего счетчика 2, регистра блока 11 передается на выход суммато- 14 или регистра 15 передается через ра 1, для чего на первый и второй

мультиплексор 9, регистр 4 данных и мультиплексор 7 на группу 18 инфор мационных выходов устройства. Запись

разряды группы управляющих входов сумматора 1 подаются нулевые сигналы, а на третий разряд - единичньш. Таким образом содержимое соответ-- ствующего индексного регистра блока 11с выхода сумматора 1 подается на группу 18 информационных выходов устройства через мультиплексор 9, буферный регистр 4 данных и мультиплексор 7. При записи информации на соответствующий индексный регистр его номер, аналогично описанному, задается .в команде и записывается в регистр 6 выбора индекса, а записываемая в индексный регистр информация поступает на группу 22 информационных входов устройства и передается через мультиплексор 9, регистр 4 данных, мультиплексор 7 и суммато 1 на группу информационных входов блока 11 индексных регистров, после чего записьшается в выбраиньй ин- дексньй регистр. В этом случае на группу управляющих входов сумматора подается код 010 (см.таблицу).

При выполнении команд передачи

авления (команды, условного и без- 55 программе овного перехода и т.п.) сформианный исполнительный адрес одним описанных способов записывается в счетчик 10 адреса данных, а в

На про 45 ты устрой адрес, вы группу 16 жимым рег и при. их 50 на управл ва. По эт тановлена мер, при ройство п

Таким о ройство ре бор функци

счетчик 2 адреса команд. Таким образом происходит переход к выполнению новой последовательности команд в программе.

с Кроме смены ССП и смены индексных регистров в подпрограмме обработки прерывания индексные регистры блока 11, счетчик 2 адреса команд и регистры 14 базового адреса и 15 конечO ного адреса могут запоминать и изменять свое содержимое по программе.

Устройство при запоминании состояния счетчика 2 адреса команд и регистров 14 базового адреса и 15 конеч5 ного адреса в памяти по командам

программы работает следующим образом. Исполнительный адрес памяти для запоминания указанных сос.тоягчй счетчика 2 или регистров 14 или 15 фор0 мируется одним из описанных способов, записывается в счетчик 10 адреса данных и передается через второй мультиплексор 8 на группу 16 адресных выходов устройства, а содержимое со5 ответствующего счетчика 2, регистра 14 или регистра 15 передается через

25 ответствующего счетчика 2, регистра 14 или регистра 15 передается через

мультиплексор 9, регистр 4 данных и мультиплексор 7 на группу 18 информационных выходов устройства. Запись

30 информации в регистры 14 базового адреса и 15 конечного адреса от их запоминания отличается тем, что по адресу, сформированному и записанному в счетчик 10 адреса данных, из

25 памяти выбирается информация, котора через группу 22 информационных входов .устройства, мультиплексор 9, регистр 4 данных, мультиплексор 7 поступает на группу информацоинных

40 входов регистра 14 базового адреса (регистр 15 конечного адреса) и записывается в этот регистр.

На протяжении всего времени рабо- 45 ты устройства блок 12 сравнивает адрес, выдаваемьш устройством на группу 16 адресных выходов, с содержимым регистра 15 конечного адреса и при. их равенстве формирует сигнал 50 на управляющем выходе 19 устройства. По этому сигналу может быть остановлена рабо.та устройства, например, при отладке программ или уст-, ройство перейдет к прерывающей подпрограмме

Таким образом предложенное устройство реализует, более широкий набор функций.

1713

Использование изобретения позволяет расширить функциональные возможности устройства и увеличить его производительность в два раза при выполнении отдельных его функций, а также, упростив программирование, сократить сроки разработки и обработку программ.

Формула изобретения

Устройство для формирования адресов команд и данных, содержащее сумматор, счетчик адреса команд, блок синхронизации, регистр данных, регистр адреса, регистр выбора индекса и три мультиплексора, причем выход сумматора соединен с первым информационным входом первого мультиплексора, выход которого соединен с информационными входами регистра адреса и регистра данных, выходы которых соединены с первым и вторым информационными входами второго мультиплексора соответственно, выход регистра адреса соединен с информационным входом счетчика адреса команд, выход второго мультиплексора является .информационным выходом устройства и соединен с входом первого слагаемого сумматора и с информационным входом регистра выбора индекса, выход счетчика адреса команд соединен с первым информационным входом третьего мультиплексора и с вторьм информационным входом первого мультиплексора, третий и четвертый информационные входы которого являются информационным входом и входом фиксированных адресов устройства соответственно, группа управляющих входов блока синхронизации соединена с первой группой разрядов управляющего входа устройства, первый и второй входы блока синхронизации являются соответственно первым и вторым входами синхронизации устройства, первый выход блока синхронизации подключен к счетному входу счетчика адреса команд,первый выход первой группы выходов блока синхронизации подключен к входу синхронизации регистра адреса, а второй выход первой группы выходов блока синхронизации соединен с входом синхронизации регистра данных, первьй выход второй группы выходов блока синхронизации подключен к входу синхронизации счетчика адреса команд, а второй выход

3. 18

второй группы выходов блока синхронизации соединен с входом синхронизации регистра выбора индекса, причем первый разряд управляющего входа устройства подключен к адресному входу второго мультиплексора, вторая группа разрядов управляющего входа устройства подключена к группе адресных входов первого мультиплексора, а третья группа разрядов управляющего входа устройства подключена к группе управляющих входов сумматора, отличающее с я тем, что, с целью расширения функциональных возможностей за счет обработки чисел расширенного формата без снижения производительности устройства, а также; упрощения программирования за счет хранения индексов при

выполнении различных участков программы, в него введены счетчик адреса данных, блок индексных регистров, блок сравнения, блок коррекции адреса, регистр базового адреса и регистр

конечного адреса, причем выход сумматора соединен с информационным входом блока индексных регистров, адресньй вход которого соединен с выходом регистра выбора индекса, выход блока

индексных регистров соединен с входом второго слагаемого сумматора, а вход синхронизации блока индексных регистров подключен к третьему выходу второй группы выходов блока синхронизации, информационные входы регистра базгового адреса и регистра конечного адреса соединены с информационным выходом устройства, а входы синхронизации регистра базового

адреса и регистра конечного адреса подключены к четвертому и пятому выходам второй группы выходов блока синхронизации соответственно, выход регистра конечного адреса соединен

с пятым информационным входом первого мультиплексора и с первым информационным входом блока сравнения, выход которого является выходом признака конечного адреса устройства, выход регистра базового адреса соединен с шестым информационным входом первого мультиплексора, выход регистра базового адреса и выход третьего мультиплексора образуют адресньй

выход устройства, которьй подключен к вт.орому информационному входу блока сравнения, причем шестой выход второй группы выходов блока синхронизации подключен к входу синхрони1913

зации счетчика адреса данных, а второй выход блока синхронизации подключен к счетному входу счетчика адреса данных, информационньш вход которого соединен с выходом регистра адреса, выход старших разрядов ко- торого подключен к входу старших разрядов второго информационного входа третьего мультиплексора, а выход младшего разряда счетчика адреса данных подг:

15

2В

257320

ключей к информационному входу блока коррекции адреса, выход которого подключен к младшему разряду второго информационного входа третьего

5 мультиплексора, управляющий вход блока коррекции адреса подключен к второму разряду управляющего входа устройства, третий разряд управляющего входа устройства подключен к адре10 ному входу третьего мультиплексора .

Л

}

28 Фиг.2 .

25

38

37

J3i 2

Фиг.З

t

Z

Щ Шл

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство сопряжения процессора с памятью | 1986 |

|

SU1322296A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммный процессор | 1984 |

|

SU1262495A1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для формирования исполнительных адресов цифровой вычислительной машины | 1978 |

|

SU728129A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств формирования адресов команд и данных в универсальных и специализированных вычислительных машинах. Цель изобретения - расширение функциональных возможностей за счет обработки чисел расширенного формата без снижения производительности устройства и упрощение программирования за счет хранения индексов при выполнении различных участков программ. Устройство содержит сумматор 1, счетчики 2 адреса. команд и 10 адреса данных, блок 11 индексных регистров, блок 3 синхронизации, блок 12 сравнения, блок 13 коррекции адреса, буферные регистры данных 4 и адреса 5, регистр 6 выбора индекса, регистр 14 базового адреса, регистр 15 конечного адреса и мультиплексоры 7-9. Новыми элементами в устройстве являются счетчик 10 адреса данных, блок 11 индексных регистров, блок 12 сравнения, блок 13 коррекции адреса и регистры базового адреса 14 и конечного адреса 15. 5 ил. 1 табл. I (Л

Фие.5

Составитель И.Поливода Редактор И. Николайчук Техред Л.Олийнык

Заказ 1972/47 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

2

Корректор С.Черни

| Формирователь адреса | 1972 |

|

SU489106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР | |||

| Устройство для формирования адреса | 1979 |

|

SU860072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1985-10-16—Подача