Изобретение относится к -вычислительной технике и аюжет исиользоваться IB автоматн.ке и приборостроении.

Известны накалливающие сумматоры, которые ПОЗВОЛЯЮТ вводить информацию как последовательным, так и параллельным кодом, содержащие ячейки временной задержки между триггерами для исключения сбоев при одновременном поступлении ла какой-либо трнлгер импульса переноса с предыдущего триггера и имнульса счета 1. Эти сумматоры из-за .наличия ячеек задержки между триггерами характеризуются ио.ниженным быстродействием, причем число этих ячеек растет с увеличением емкости сумматора, что ведет к падению быстродействия с увеличением емкости cy.MiMaTopa. Известны также накапливающие сумматоры с пар аллельньш переносом, обладающие высоким быстродействием 1. Однако -они требуют относительно больщого числа элементов для их построения. Наиболее близким техническим рещением к изобретению является -накапливающий сум.матор, содержащий двоичный счетчик, состоящий из грулп триггеров, распределитель импульсов и управляемые элементы «И, причем выходы распределителя связаны через управляемые элементы «И с первыми счетными (Входами соответствующих триггеров в группах, второй вход Каждого из которых, кроме первОГО триггера в каждой группе, связан с выходами нредыдущего триггера 2. Этот суММатор относится к сумматорам с лараллельно - носледовательным сдг.игом ннформацин и содержит в каждой группе дололнительный триггер для передачи импульса переноса с данной группы триггеров в следующую. В этом суммато ре для лередачи инфор:мации о переносе в лем треПуется

ПО од1ю,му до:полннтельно.му такту нг. кр.ждьш дололнительный триггер, а следователью, и группы, что ограни;чивает быстродейс зие, причем С увеличением емкости сумматора падает его быстродействие и усложняется схема распределителя.

Целью изобретения является у леньшение чис.та элементов и повышение быстродействия. В описываемом сум маторе это достигается тел1, что он содержит узел залрета и уплравляемые узлы задерж1 и, причем второй счетный вхОД .каждого первого триггера в каждой группе подключен к выходу предыдуп1его управляемого узла задержки, нерзый аход каждого управляемого узла задержки подключен к выходу последнего в лредыдущей группе триггера, а второй вход - к выходу узла залрета, вход которого подключен к выходу распределителя импульсов. Кроме того, в сумматоре каждый управляемый узел задержки состоит из двух элементов «И, ячейки памяти, элемента «ИЛИ и элемента «НЕ, причем первые входы элементов «И подключены к .первому входу управляемого узла задержки, второй вход которого .подключен ко второму .входу первого элемента «И, пер.ному входу ячейки памяти и входу элемента «НЕ, (выход которого подключен ко второму входу второго элемента «И, .выход которого связан с первым -входом элемента «Р1ЛИ, выход которого подключен к выходу управляемого узла задержки, а второй вход - к выходу памяти, второй вход которой связан с выходом первого эломе.нта «И.

Нри этОМ управляемый узел задержки выполнен в впде еимметрпчнОГО триггера с одним БмнульсныМ входом, связалным с первым .входом управляемого узла задержки, и одним потенциальным входОгМ, связалным со вторым входом управляемого узла задерней.

Все это позволяет уменьшить общее число ячеек путем уменьшения ячеек в распределителе, а также повысить быстродействие в результате одновременной записи информации во всех группах счетчи ка.

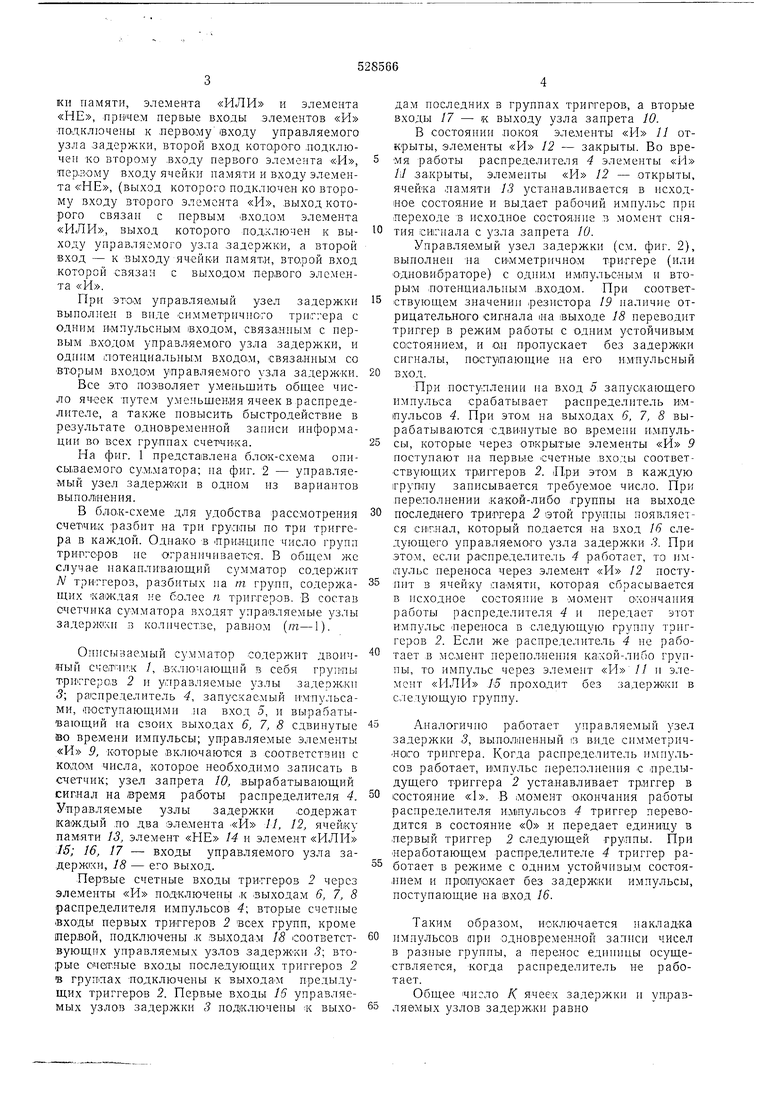

На фиг. 1 предста.влена блак-схема описываемого сум.матора; на фиг. 2 - управляемый узел задер;Ж1КИ в одпом из вариаитов выпол1не.ния.

В бло.к-схеме для удобства рассмотрения счетчи;к разбит на три груплы по три триггера в каждой. Одиако в принципе число групп триггеров пе ограничивается. В общем же случае паканливающий сумматор содержит N триггеров, разбитых иа т групп, содержащих «а1ждая lie более п триггеров. В состав счетчика сумматора входят управляемые узлы задержли з количестве, рав.ном (т-1).

Описываемый сумматор содержит двоичный счетп1:к /, включающий в себя группы триггеров 2 и управляемые узлы задеож.кп 3; раснределитель 4, запускаемый Импульсами, поступающими на вход 5, и вырабатывающий на своих выходах 6, 7, 8 сдвинутые во времени имнульсы; управляемые элементы «И 9, которые включаются в соответствии с кодоМ числа, которое необходимо записать в счетчик; узел запрета 10, вырабатывающий сигнал на время работы раснре.делителя 4. Управляемые узлы задержки содержат каждый .по .два элемента -«И 11, 12, ячейку памяти 13, элемент «НЕ 14 и элемент «ИЛИ 16; 16, 17 - входы управляемого узла за.держ1хи, 18 - его выход.

Первые счетные входы триггеров 2 через элементы «И подключеиы j выходам 6, 7, 8 распределителя импульсов 4; вторые счетные входы первых триггеров 2 всех групп, кроме первой, подключены к .-выходам 18 соответствующих управляемых узлов задерж-ки .; вто;рые очотлые входы последующих триггеров 2 в группах подключены к выходал предыдущих триггеров 2. Первые входы 16 управляемых узлов задер.жки 3 подключены а выходам последних в группах триггеров, а вторые входы 17 - к выходу узла запрета 10.

В состояиип покоя элементы «И // открыты, элементы «И 12 - за.крыты. Во время работы распределителя 4 элементы «И и закрыты, элемепты «И 12 - открыты, ячейка пам.яти 13 уста.иавливается в исходное состоя.ние и выдает рабочий импульс при переходе в исходное состоя.нне з момент снятия сигнала с узла занрета 10.

Управляемый узел задержки (см. фиг. 2), выполнен па симметрично.м триггере (или одновибраторе) с одии.м импульсным и вторым .потенциальным входом. При соответствующем значении резистора 19 наличие отрицательного сигнала ina выходе 18 переводит триггер в режим работы с одним устойчивым состоянием, и o,n пропускает без задерж(ки сигналы, иостуиающИб иа его импульсный

вход.

При поступлении на вход 5 зануокающего импульса срабатывает распределитель импульсов 4. При этом на выходах 6, 7, 8 вырабатываются сдвинутые во времени нм.пульсы, которые через открытые элементы «И 9 поступают иа первые счетные .входы соответствующих триггеров 2. При этом в каждую группу записывается требуемое число. При иереполнении какой-либо группы на выходе

последнего триггера 2 этой группы появляется сигнал, который подается па вход 16 следующего управляемого узла задержки -9. При этом, если распр.е.делитель 4 работает, то импульс переноса через элемент «И 12 ноступит в ячейку памяти, которая сбрасывается в исходное состояние в момент ОХончания работы распределителя 4 и иередает этот импульс .переноса в сл.едующую группу триггеров 2. Если же распределитель 4 ие работает в мс.мент перепоЛНення ка;лой-либо группы, то имиульс через элемент «И // и элемент «ИЛИ 15 прохо.дит без задержки в с.ледующую группу.

А.иалогично работает управляемый узел задержки 3, выполагеипый п виде симметричного триггера. Когда распределитель импульсов работает, иашульс переполнения с предыдущего триггера 2 устанавливает триггер в

состояние «Ь. В 1момент о-кончания работы распределителя и.м1пульсов 4 триггер переводится в состояние «О и передает единицу в .первый триггер 2 следующей группы. При неработающем распределителе 4 триггер работает в режиме с одним устойчивым состоя.нием и нроиускает без задержки импульсы, поступающие на вход 16.

Таким образом, исключается накладка импульсов при одновремен.ной записи чисел в разные группы, а перенос едииицы осуществляется, когда распределитель не работает.

Общее число К ячеек задержки и управляемых узлов задержки равно f + . + ll-0 -bTт. е. акономия в ячейках будет равна N N - n1. Выведем соотношение между jV и п, обеспе чивающее минимальное число ячеек задерж ки. Для этого определим экстремум для /( dk J dn п Приравняв полученлое выражение нулю, по луиим . При этом обеспечивается минимальное число ячеек задержки в счетчике и в распредели теле. Общее число ячеек в этом случае равно /Г.2/ЛГ- 1, что дает эколомию в Д / - 1 - 2 /;V + - 2 УЫ ячеек задерЖКИ. Принцип, заложенный в описываемый сум М.атор, может быть использован и для тех случаев, когда коэффициент пересчета сум матора в целом или его групп отличается от двоичного, т. е. когда .в счетчик вводятся дополнительные связи, а также когда запись чисел ведется в «оде, отлич.ном от двоичного Фор iM ула изобретения 1. Накапливающий сумматор, содержащий двоичиый счетчик, состоящий из групп триг геров, распределитель и.мпульсов п управляемые элементы «П, причем БЫ.од1з; распределителя связаны через управляемые элементы «И с первымп счетными входами соответствующих триггеров в группах, второй вход каждого из .которых, 1кроме первого триггера в .каждой группе, -связан с выходом предыдущего триггера, отличающийся тем, что, с целью уменьщенпя числа элементов и повыщелия быстродействия, сумматор содержит узел запрета и управляемые узлы задержки, иричем вто1рой счетный вход каждого первого триггера в каждой группе подключен к выходу Предыдущего управляемого узла задержки, первый вход каждого управляемого узла задержки подключен .к выходу последнего в (Предыдущей группе триггера, а второй вход - к выходу узла запрета, вход которого подключен к выходу распределителя М1М|ПуЛЬСОВ. 2.Сумматор по п. 1, о т л и ч а ю ииг и с я тем, что каждый управляемый узел задержки состоит из двух элементов «И, ячейки памяти, элемента «ИЛИ и элемента «ПЕ, .причем первые входы элементов «И подключены к .первому ВХО.ДУ управляемого узла залаерж.ки, второй вход которого подключен ко вт.орол1у входу первого элемента «И, первому .входу ячейки памяти и входу элемента «НЕ, .выход iKOTOporo подключен ко второму входу второго элемента «И, выход которого связан с перзы.м входом элемента «ИЛИ, выход .которого подключен .к выходу управляемого узла задержки, а второй вход - к выходу ячейки памяти, второй вход .которой связан с выходом первого элемента «И. 3.Сум.матор по п. 1, о т л п ч а ю щ п и с я тем, что управляемый узел задерл ки выполнен в виде симметрич.ного триггера с одним иМ|Пульсным входо. связанным с первым входом управляемого узла задержки, и одним потенциальным входом, связанным со вторым входом управляемого узла задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки чисел | 1983 |

|

SU1151952A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство цифровой информации | 1991 |

|

SU1815653A1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| Корреляционный дискриминатор времени транспортного запаздывания | 1983 |

|

SU1107130A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Устройство для определения теоретического веса проката | 1976 |

|

SU560145A1 |

| Ассоциативная однородная обучаемая среда для распознавания объектов | 1983 |

|

SU1149287A1 |

| Устройство для считывания графической информации | 1980 |

|

SU955133A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

Авторы

Даты

1976-09-15—Публикация

1973-09-24—Подача