Фи&1

Изобретение относится к технике цифрового измерения частоты.

Цель изобретения - повьппение быстродействия. .

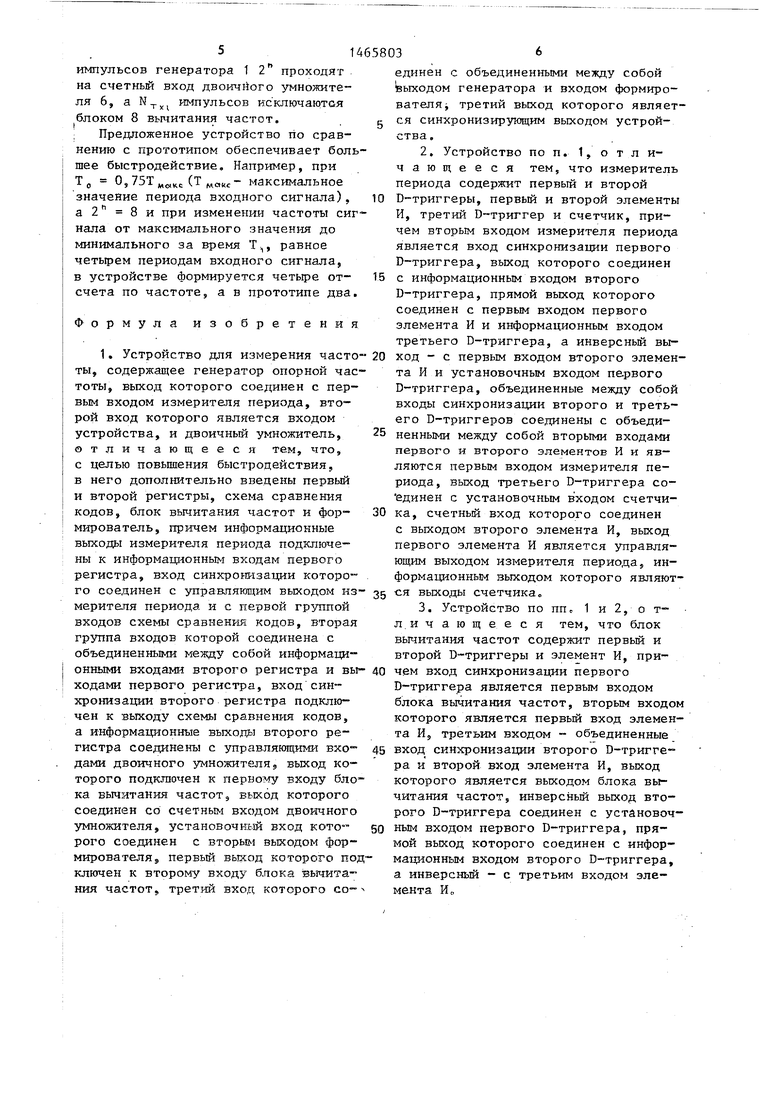

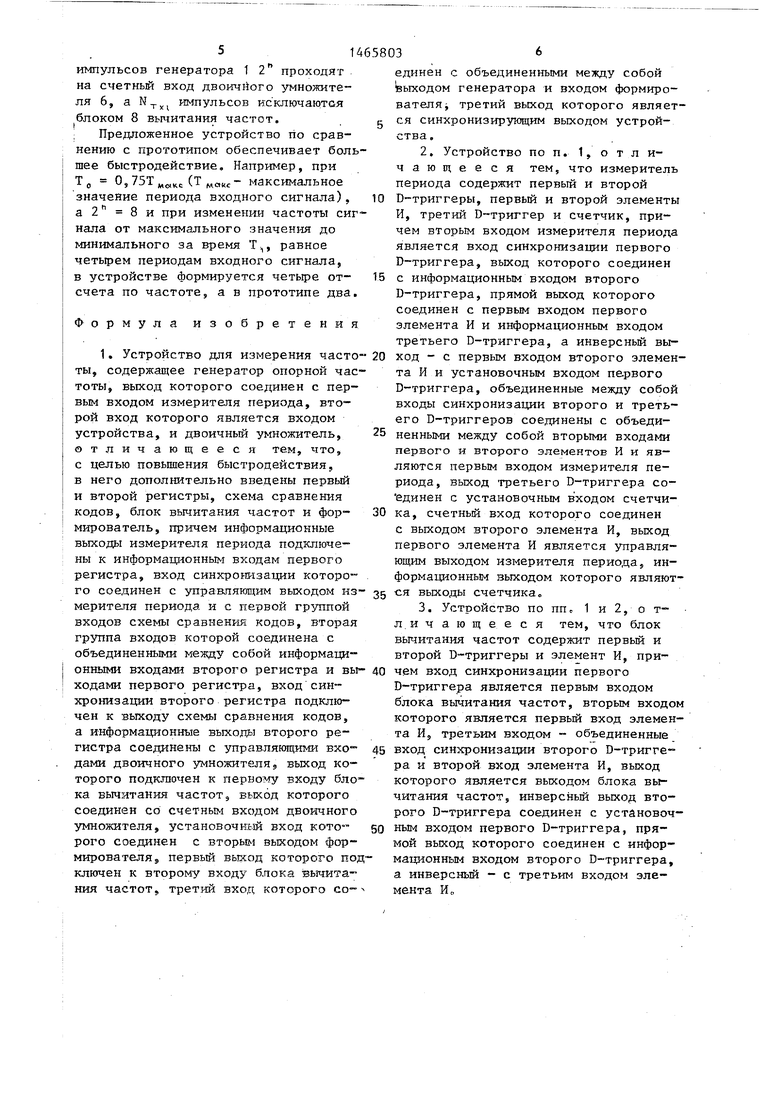

На фиг. 1 представлена функциональная стрема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство содержит генератор 1 опорной частоты, измеритель 2 периода, первый регистр 3, схему 4 сравнения кодов, второй регистр 5, двоичный умножитель 6, формщ ователь 7 и блок 8 вычитания частот,

Измеритель периода 2 включает в себя первый 9 и второй 10 В тригге- ры, первый 11 и второй 12 элементы И третий D-триггер 13 и счетчик 14.

Блок 8 вычитания частот содержит первый, 15 и второй 16 D-триггеры и элемент И 17.

Выход генератора 1 опорной частоты соединен с первым входом измерителя 2 периода, второй вход которого является входом устройства, информационные выходы измерителя 2 периода подключены к информационным входам регистра 3, вход синхронизации которого соединен с управляющим выходом измерителя 2 периода и первой группой входов схемы 4 сравнения кодов, вторая группа входов которой соединена с объединенным информационными входами регистра 5 и выходами регистра 3, вход синхронизаз: ии регистра 5 подключен к выходу схемы 4 сравнения кодов, а информационные выходы регисра 5 соединены с управляющими входами двоичного умножителя 6, выход ко- торого подключен к первому входу блока 8 вычитания частот, выход которого соединен со счетным входом двоичного умножителя 6, установочный вход которого соединен с вторым выходом формирователя 7, первый вход которого подключен к второму входу блока 8 вычитания частот, третий вход которого соединен с объединенными выходом генератора 1 и входом формирователя третий выход которого является синхр низирующим выходом устройства. Вторым входом измерителя 2 периода является вход синхрог-шзаьщи D-тригге- ра 9, выход которого соединен с информационным входом В-триггера 10, прямой выход которого соединен с первым входом элемента И 11 и информационным входом D-триггера 13, а ин

Q 5

0

5 O Qn

5

5

версный выход - с первым входом элемента И 12 и установочным входом D-триггера 9, объединенные входы синхронизации D-триггеров 10 и 13 соединены с объединенными вторыми входами элементов И 11 и 12 и являются первым входом измерителя 2 периода. Выход D-триггера 13 соединен с установочным входом счетчика 14, счетньй вход которого соединен с выходом элемента И 12, выход элемента И 11 является управляющим выходом измерителя 2. периода-, информационным выходом которого являются выходы счетчика 14. Первым входом блока 8 вычитания частот является вход синхронизации D-триггера 15, вторым - первый вход элемента И 17, а третьим - объединенные вход синхронизации D-триггера 16 и-второй вход элемента И 17, выход которого является вьг- ходом блока 8 вычитания частот, ин- версньш выход D-триггера 16 соединен с установочным входом D-триггера 15, прямой выход которого соединен с информационным входом D-триггера 16, а инверсный - с третьим входом эле- мента И 17,

Устройство работает следующим образом.

Измеряемая частота f поступает на вход измерителя 2 периода. По пе- репаду входного сигнала (фиг. 2) триггер 9 переключается и на инфор- мационньй вход триггера 10 поступа- ет единичный потенциал. Затем первьй импульс с генератора 1 устанавливает триггер 10 также в единичное со- тояние, при этом элемент И 12 закры- .вается, триггер 9 возвращается в ис- ходное состояние, элемент И 11 открывается Очередной импульс с генератора 1 (второй относительно момента переключения триггера 9) выделяется на элементе И 11 и переключает триггер 13 в единичное, а триггер 10 - в нулевое состояние. Третий импульс из последовательности с генератора 1 .устанавливает триггер 13 в нулевое состоя ние. Таким образом, один из импульсов генератора 1 не приходит через элемент И 12, а выделяется на выходе элемента И 11. Длительносл-ь . импульсов сброса счетчика 14 равна периоду сигнала генератора 1, поэтому соответствующий импульс, поступающий на его счетный вход, не вызывает изменения кода в счетчике 14. Следовательно, по сигналу установки на , входе R в счетчик 14 необходимо записать код равный 2.

Триггеры 9 и 10 обеспечивают син- хронизацию входного сигнала f« отно- сительно импульсов генератора 1, в результате кодируемый период сигнала f кратен периоду сигнала генератора 1. Это -обеспечивает синхронизацию ю работы и уменьшение погрешнс сти устройства.

Период синхронизированного входного сигнала ft кодируется в измерителе 2 периода.15

Коэффициент деления счетчика 14 выбирается из условия

п

Последовательность импульсов н выходе двоичного умножителя 6 сфо рована из импульсов генератора 1 при поступлении очередного импуль на синхроновод триггера 15 послед переключается и закрьшает элемент И 17. Очередной импульс генератор устанавливает триггер 16 в единич ное состояние, сигналом с инверсн выхода которого возвращается в ис ходное состояние триггер 15. Зате следующим импульсом с генератора реключается в исходное состояние триггер 16.

Если в выражение (4) подстави значение f ц,, д.,, из (3) и учест

k - f о / f Mate

где f

(1)

что

т; (NT, + ),

в

ТО

64 f.i

f 2. Значение кода частоты в

- к мсльс.

максимальное значение вход- о чике двоичного умножителя 6 (где

ной частоты;

п - целое положительное число;

k - коэффициент деления счетчика 14.

При условии (1) код периода определяется соотношением:

Т с. fx- 2 (где TO - время коди вания , формируемое на первом вых формирователя 7). По окончании и рительного интервала Т сигналом

25 третьего выхода формирователя 7 из счетчика двоичного умножителя переписывается на регистрацию и пульсом с второго выхода формиро теля 7 сбрасывается в исходное с

N

т х

il-2,(2)

-о где Т х - период синхронизированного

входного сигнала; Си - период сигнала генератора.

По окончании периода Т ,( код из измерителя 2 периода переписывается в регистр 3. Выходы счетчика 14 и регистра 3 подключены к первой группе входов блока 4 сравнения кодов, при этом сравнивается, например, обратный код счетчика 14 и прямой код.регистра 3, При равенстве кодов блок 4 сравнения кодов вырабатьгоает сигнал, по которому код из регистра 3 переносится в регистр 5, Выходы регистра 5 подключены к управляющим входам дар- ичного умножителя 6, сч етный вход которого соединен с выходом блока 8 вычитания частот. При коэффициенте деления равном 2 частота на выходе двоичного умножителя

ЬХ 4.

NT,

БЫК . А i

Частота на выходе блока -8 вычита нйя частот

f RX А. fo - f 6ЫХ ft.3

, ю15

Последовательность импульсов на выходе двоичного умножителя 6 сформирована из импульсов генератора 1 и при поступлении очередного импульса на синхроновод триггера 15 последний переключается и закрьшает элемент И 17. Очередной импульс генератора устанавливает триггер 16 в единичное состояние, сигналом с инверсного выхода которого возвращается в исходное состояние триггер 15. Затем следующим импульсом с генератора переключается в исходное состояние триггер 16.

Если в выражение (4) подставить значение f ц,, д.,, из (3) и учесть,

что

т; (NT, + ),

в

ТО

64 f.i

f 2. Значение кода частоты в счетд- о чике двоичного умножителя 6 чике двоичного умножителя 6 (где

Т с. fx- 2 (где TO - время кодирования , формируемое на первом выходе формирователя 7). По окончании измерительного интервала Т сигналом с

25 третьего выхода формирователя 7 код из счетчика двоичного умножителя 6 переписывается на регистрацию и импульсом с второго выхода формирователя 7 сбрасывается в исходное состо30 яние. При использовании предлагаемого устройства в многоканальных информационно-измерительных системах, когда необходимо получить отсчеты в одни и те же моменты времени, ис3g пользуется общий на требуемое число каналов формирователь 7. Тем самьм обеспечивается синхронность вьздачи результатов по всем каналам.

Введение в устройство схемы 4 сравнения кодов и регистра 5 позволяет ставить в-соответствие каждому периоду сигнала fх точно 2 импульсов (т.ео точно выполнить соотноше40

ние f

Bt А. V

fV 2 для среднего зна- 45 чения частоты). Действительно момент f; переписи кода из регистра 3 в регистр 5 относительно начала соответствующего периода синхронизированного сигнала f х можно определить из соотношения;

50

(2 + N.

+ NTV,)

е)

55

t; U Tx - . где FTj .- обратньй код значения N у

Значение суммы NTXJ+ N Г|„ 2 Ч т.е. равно постоянной величине. Это значит, что код очередного периода сигнала f. хранится в регистре 5 строго в течение времени, равного . значений этого периода, и из 2 + Nrtv,.

5

импульсов генератора 1 2 на счетньй вход двокмйого

ля 6, а -гyf импульсов исключаются блоком 8 вычитания частот,I

; Предложенное устройство по сравнению с прототипом обеспечивает большее быстродействие. Например, при Тд О, 75Т лцс (Т окс максимальное значение периода входного сигнала), а 2 8 и при изменении частоты сигнала от максимального значения до минимального за время Т, равное четырем периодам входного сигнала, в устройстве формируется четыре отсчета по частоте, а в прототипе два.

Формула изобретения

1. Устройство для измерения часто ты, содержащее генератор опорной час тоты, выход которого соединен с первым входом измерителя периода, второй вход которого является входом устройства, и двоичный умножитель, отличающееся тем, что, с целью повьшения быстродействия, в него дополнительно введены первый и второй регистры, схема сравнения кодов, блок вычитания частот и формирователь, причем информационные выходы измерителя периода подключены к информационным входам первого регистра, вход синхронизации которо

единен с объединенными между собой выходом генератора и входом формирователя j третий выход которого является синхронизирующим выходом устройства.

2. Устройство по п. 1, о т л и- чающееся тем, что измеритель периода содержит первый и второй D-триггеры, первый и второй элементы И, трет:нй В триггер и счетчик, причем вторым входом измерителя периода является вход синхронизации первого D-триггера, выход которого соединен

с информационным входом второго D-триггера, прямой выход которого соединен с первым входом первого элемента И и информационным входом третьего D-триггера, а инверсньй выход - с первым входом второго элемента И и установочным входом п&рвого D-триггера, объединенные между собой входы синхронизации второго и третьего D-триггаров соединены с объединенными между собой вторыми входами первого и второго элементов И и являются первым входом измерителя периода, выход третьего D-триггера со- единен с установочным входом счетчика, счетный вход которого соединен с выходом второго элемента И, выход первого элемента И является управляющим выходом измерителя периода, ин- формационньв выходом которого являют

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1980 |

|

SU868756A1 |

| Умножитель частоты | 1983 |

|

SU1176439A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1267601A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU894847A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для отображения информации на экране электроннолучевой трубки | 1984 |

|

SU1257635A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

Изобретение относится к измерительной технике. Цель изобретения - повышение быстродействия. Для достижения цели в устройство для измерения частоты введены регистры 3, 5, схема сравнения кодов 4, формирователь 7 и блок вычитания частот 8. Устройство ДЛЯ измерения частоты содержит также опорный генератор 1, измерите,пь периода 2 и двоичный умно- жIiтeль 6. Приведены конкретные примеры реализации измерителя периода 2 и блока вычитания частот 8. Устройство ДЛЯ измерения частоты может быть использовано в информационно-измерительных приборах. 2 ил. (Л с

го соединен с управляклцим выходом из- выходы счетчика меритепя периода и с первой группой 3. Устройство по пп, 1 и 2, о твходов схемы сравнения кодов, втораял.ичающееся тем, что блок

группа входов которой соединена свычитания частот содержит первый и

объединенными между собой информаци-второй D-триггеры и элемент И, прионными входами второго регистра и вы- 40чем вход синхронизации первого

ходами первого регистра, вход синхронизации второго регистра подключен к выходу схемы сравнения кодов, а информационные выходы второго регистра соединены с управляющими дами двоичного умножитгшя, выход которого подключен к пергю входу бло ка вычитания частот, выход которого соединен со счетным входом двоичного умножителя, установочный вход которого соединен с вторым выходом формирователя , первый выход которого под- ключен к второму входу блока вычитания частот третий вход которого со

D-триггера является первым входом блока вычитания частот, вторым входом которого является первый вход элемента И, третьим входом - объединенные

вход синхронизации второго D-триггера и второй вход элемента И, выход которого является выходом блока вычитания частот, инверсный выход второго D-триггера соединен с установочным входом первого D-триггера, прямой выход которого соединен с информационным входом второго D-триггера, а инверсный - с третьим входом элемента И„

f JTJ1Jl JlJb JlJb J1 rLrL

cpusZ

| Шмендин В.М | |||

| Цифровые измерительные преобразователи и приборы | |||

| - М.: Высшая школа, 1973, с | |||

| Катодное реле | 1918 |

|

SU159A1 |

| Шмендин В.М | |||

| Цифровые электроизмерительные приборы | |||

| - Энергия, 1972, с | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

Авторы

Даты

1989-03-15—Публикация

1987-02-27—Подача