И четвертый автоматы Уилкса-Стринджера, первый, второй, третий и четвертый блоки опроеа, триггер, первый и второй элементы И, причем третья и четвертая группы разрядных выходов четвертого автомата соединены соответственно с третьей группой разрядных входов и адресными входами третьего автомата, вторая и третья группы разрядных выходов третьего автомата соединены со вторыми группами разрядных входов соответственно второго и первого автоматов, четвертые группы разрядных выходов четвертого и третьего автоматов соединены соответственно с адресными входами третьего и первой группой адресных входов четвертого автоматов, первые группы разрядных выходов четвертого и третьего автоматов соединены с первыми группами разрядных входов соответственно третьего и второго автоматов, кодовые входы устройства соединены со второй группой адресных входов четвертого автомата, входы регистра микрокоманд соединены с первой группой разрядных выходов первого автомата, выходы первого, второго, третьего и четвертого блоков опроса соединены с управляющими входами соответственно первого, второго, третьего и четвертого автоматов, первые подготовительные входы первого и второго блоков опроса соединены соответственно с выходами второго и первого блоков опроса, вторые подготовительные входы первого и второго блоков опроса соединены соответственно с первым и вторым выходами регистра микрокоманд, третий выход которого соединен со входами запрета первого и второго блоков опроса, выход третьего блока опроса соединен с единичным входом триггера и первым подготовительным входом четвертого блока опроса, выход которого соединен с пулевым входом триггера и первым подготовительным входом третьего блока опроса, входы запрета третьего и четвертого блоков опроса соединены с четвертым выходом регистра микрокоманд, пятый выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с единичным и нулевым выходами триггера, выходы первого и второго элементов И соединены со вторыми подготовительными входами соответственно четвертого и третьего блоков опроса, тактовые входы первого, второго, третьего и четвертого блоков опроса соединены с тактовым входом устройства, третий и четвертый автоматы содержат первый и второй дополнительные блоки памяти переходов, адресные выходы блока памяти переходов соединены через первый дополнительный блок памяти переходов с адресными входами второго дополнительного блока памяти переходов, разрядные входы первого дополнительного блока памяти переходов и регистра адреса третьего автомата соединены соответственно с третьей группой и адресными входами этого автомата, третья и четвертая группы разрядных выходов автомата соединены с разрядными выходами соответственно первого и второго дополнительных блоков памяти переходов, а итсрая группа адресных входов четвертого аитомата соединена с разрядными входами ре5 гисчра адреса этого автомата.

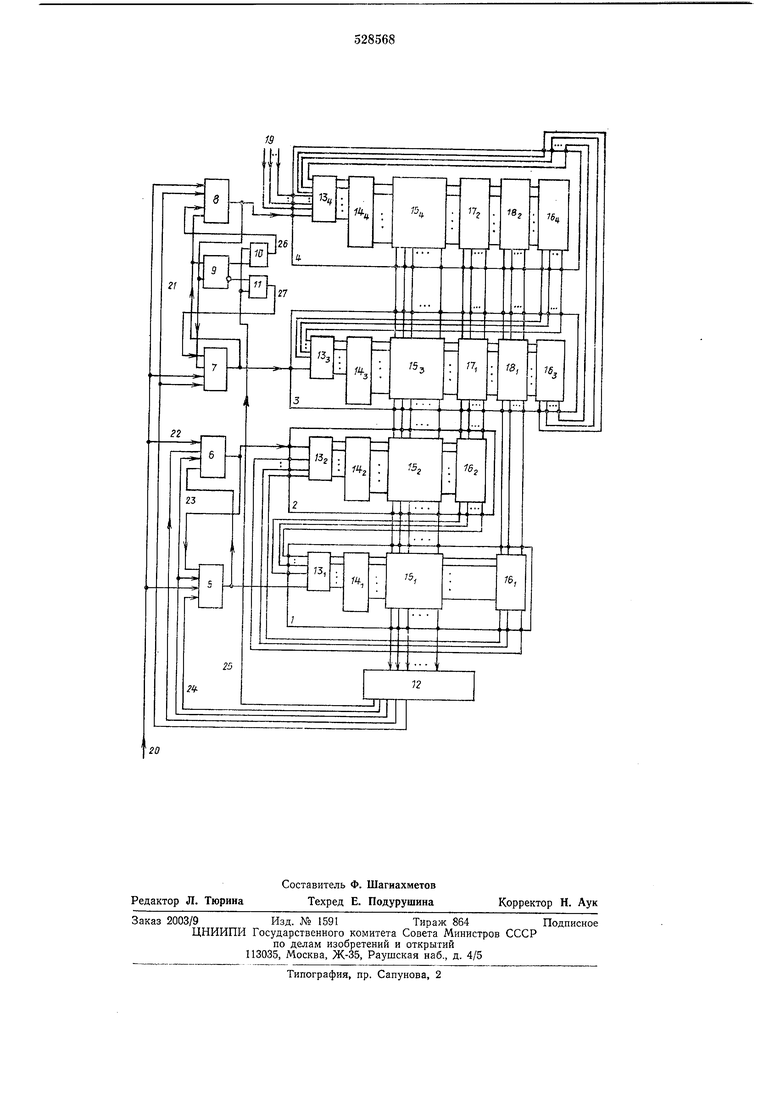

На чертеже представлена блок-схема описываемого устройства.

Оно содержит автоматы 1-4 Уилкса-Стринджера, блоки опроса 5-8, триггер 9, элементы 10 И 10, 11, регистр микрокоманд 12. Первый и второй автоматы Уилкса-Стринджера содержат регистра адреса 13i-134, дешифраторы i4i-144, блоки 15i-154 памяти микрокоманд, блоки 16i-162 памяти переходов, а 15 третий и четвертый автоматы Уилкса-Стринджера содержат блоки 16з, 164 памяти переходов и дополнительные блоки 17i, Пг и 18i, 182 памяти переходов. На чертеже, кроме того, обозначены: 19 - группа входов устройства,

0 20 - тактовый вход устройства, 21-25 - выходы регистра микрокоманд, 26, 27 - выходы элементов И. Автоматы 1, 2 и 3, 4 образуют соответственно нижний и верхний уровень иерархии устройства. Блоки 16i и IGj

5 автоматов 1 и 2 доступны для автоматов 3, 4, а блоки 1бз, 164, 17ь 172, 18, ISg автоматов 3, 4 не перекрываются пи взаимно, ни автоматами 1, 2. В слово микрокоманды введено специальное поле управления переходами с уровня

0 на уровень, которое может выдать пять микроприказов. При этом возможеп переход с любого из автоматов 3, 4 верхнего уровня на любой из автоматов 1, 2 нижнего уровня. Возврат с нижнего уровня на верхний (с любого

5 из автоматов 1, 2) происходит всегда на автомат верхнего уровня, противоположный тому, с которого был совершен переход на нижний уровень, для чего в устройстве 1меется триггер 9, который всегда устанавливается в

0 «1 при выборе микрокоманды из автомата 4 верхнего уровня и в «О - при выборе из автомата 3. При возврате с нижнего уровня выдается микроприказ, который тестирует триггер 9 и разрешает работу автомата 3 или 4.

5 Автоматы обоих уровней могут, в зависимости от комбинации выданных микроприказов, работать одновременно, делая К шагов в начале или в конце микроподпрограммы (или и в начале и в конце), что позволяет строить

0 более универсальные микроподпрограммы.

Предварительно все множество микропрограмм М. вычислительной машины разбивается на две части: подпрограмма верхнего В-- Мь М2,. . . Мтг и нижнего Н Ml,

5 М2, . . ., Мге уровня. Множество Н составляется из отдельных часто встречающихся в различных микропрограммах Мг последовательностей операторов Hj. Длина этих последовательностей может быть любой, но с целью получения оптимальных размеров памяти автоматов нижнего уровня число операторов в последовательности не выбирают больше 12-15. Для более длинных последовательпостей целесообразнее применять многоранговую структуру микроподпрограмм с регистрами возврата, что в сочетании с предложенной структурой позволяет получать максимальную экономию памяти микрокоманд. В дальнейшем оба подмножества В и Н разбиваются каждое на два: В1, В2 и HI, Н2 соответствепно. Каждое подмножество соответствует одному из автоматов 1-4 устройства.

Начала микроподпрограмм нижнего уровня распределяются по автоматам 1, 2 так, чтобы . Все начальные микрокоманды подпрограмм верхнего уровня располагаются во множестве В1. В множества В1 и HI входят нечетные микрокоманды, в множестве В2 и Н2 - четные. Концы микроподпрограмм обоих уровней могут раснолагаться в любом подмножестве.

В исходном состоянии подготовлен блок опроса 8, блоки опроса 5, 6, 7 - не подготовлены. На регистр адреса 13. автомата 4 верхнего уровня по входам 19 из регистра команды введен адрес начальной микрокоманды заданной микропрограммы. На вход 20 от основного задающего генератора вычислительной машины ноступают тактовые импульсы. Первым импульсом запускается блок опроса 8, триггер 9 устанавливается в «О, готовится блок опроса 7, считывается регистр адреса 184 и возбуждается через дешифратор 1-44 шина (слово), соответствуюш.ая введенному коду. Блок опроса 8 становится неподготовленным. На регистр микрокоманд 12 поступает слово выбранной микрокоманды. Если в первой микрокоманде нет обращения на нижний уровень, то на регистр адреса 13з записывается из блока 16. памяти переходов адрес следующей микрокоманды верхнего уровня (из множества В2). Второй импульс тактового генератора по входу 20 запускает блок опроса 7, который устанавливает триггер 9 в состояние «1, готовит блок опроса 8 и возбуждает через дешифратор 14з шину выбранной микрокоманды. На следующий импульс такта по входу 20 срабатывает блок опроса 8, триггер 9 устанавливается в «О, подготавливается блок опроса 7 и считывается микрокоманда из множества В1. Работа автоматов 3, 4 верхнего уровня друг на друга продолжается до тех пор, пока не требуется перейти к подпрограмме нижнего уровня. Если на каком-либо щаге микронодпрогрлммы (микрокоманде) М,-в требуется осуществить переход на нижний уровень, к микрокоманде М;н, то работа устройства происходит следующим образом:

а) , Mi+ieHl. тогда очередным импульсом по входу 20 запускается блок опроса 8, триггер 9 устанавливается в и выбирается через дешифратор 14/, слово М;. При этом на регистр адреса 13з верхнего уровня из блока 164 записывается адрес микрокоманды М,, к которой необходимо перейти после окончания подпрограммы нижнего уровня, на регистр адреса 130 нижнего уровня из блока IGi зап1сывается адрес начальной микрокоманды Мг+1 подпрограммы нижнего уровня. В слове микрокоманды М{ имеется микроприказ, запрен.аюший по входу 21 подготовку блоков 7, 8, и микропрнказ, готовящий по входу 22 блок опроса 6 нижнего уровня. Триггер 9 запоминает состояние «О, так как на блок опроса 7 действует нмпульс запрета по входу 21, он остается неподготовленным. Следующим импульсом такта по входу 20 запускается уже блок опроса 6. готовит блок опроса 5 нижнего уровня и через дешифратор На возбуждает шину из множества HI, соответствующую микрокоманде A1,--Li. При этом, если в микропрограмме нижнего уровня более одной микрокоманды, то на регистр адреса 13i нижнего уровня записывается адрес очередной микрокоманды. В следующем такте срабатывает блок опроса 5, готовит блок опроса б и через дешифратор 14i возбуждает очередную микрокоманду (шину) из множества Н2. Работа автоматов 1, 2 нил-снего уровня друг на друга

продолжается до исполнения микрокоманды , после которой требуется возвратиться на верхний уровень. При выборе микрокоманды М; на регистр адреса не записывается адрес очередной микрокоманды. Выдается

микроприказ, запрешающий по выходу 23 под- ГОТОВКУ блоков опроса 5, 6, и микроприказ, воздействующий на входы элементов «И 10, 11 по выходу 25. Так как триггер 9 находится в состоянии «О, то с выхода 27 первого элемента «И 11 готовится блок опроса 7 верхнего уровня. В следующем такте по входу 20 запускается блок опроса 7, устанавливает триггер 9 в «1, подготавливает блок опроса 8, считывает регистр адреса 13з, на который

перед обращением к нижнему уровню записывается адрес микрокоманды, и через дешифоатор Из возбуждает ШИНУ из множества В2, соответствующую М;. Далее аналогично исполняется микроподпрограмма верхнего уровня.

6} ЛТ,. М,-+;еН2. Работа происходит аналогично, только, вместо записи на регистр 13я из блока 6i, производится запись адреса на регистр адреса 13 нижнего уровня из

блока 162 и, вместо микроприказа, готовящего по ВЫХО.П:У 22 блок опроса 7, выдается микроприказ, готовящий по выходу 24 блок опроса 6. Таким образом, в (i -г 1)-м такте запускается блок опроса 6 и считывает микрокоманду Mf....

в )М;еВ2. М,-.еН1. В (-М такте запускается блок опроса 7, устанавливает в «1 триггер 9. готовит блок опроса 8, который одновременно запрещается по выходу 21, и считывает регистр адреса 13. При этом через дешифратор 14:, возбуждается шина микроколатгды М; TI на регистр адреса 13л записывается адрес микрокоманды Mj, к которой необходимо перейти, после возврата на верхний уровень. Выдаются те же микроприказы, чтс т г, случае M;e;Bl, M;+ieHl. При возврате т-я верхний уровень микроприказ тто выходу 2Е через элемент И 10 и выход 26 (так как триггер 9 установлен в «1) подготавливает бло1

опроса 8. Следующая микрокоманда (М;) выбирается из автомата 4 верхнего уровня.

г) , Мг+1еН2. Работа происходит аналогично, только при переходе к нижнему уровню готовится блок опроса 5, а в микрокоманде М,- производится запись адреса из блока 1б2 на регистр 13|.

Возможна нараллельная работа автоматов верхнего и нижнего уровня. В этом случае выполняются составные микрокоманды, т. е. часть управляющих микроприказов выдается с верхнего уровня By mi, т, . . ., гпп, а часть - с нижнего Ну mi, т,. . ., гпп Должно выполняться условие By п Ну 0 т. е. в каждом подмножестве должны выдаваться различные микроприказы. Это позволяет строить более гибкие микропрограммы, т. е. использовать полностью подпрограмму нижнего уровня, а отсутствующие в ней микроприказы «добавлять из верхнего уровня. Для организации такого при переходе на нижний уровень блоки 16 или IGj возбуждаются не в микрокоманде Mi, а в микрокоманде Мг-к, где К - число совместных шагов обоих автоматов. Тогда же выдается и микроприказ по выходам 22, 24, а в микрокоманде вепхпего УРОВНЯ 5, выдается микроприказ по выходу 21, запреп ающий подготовку блоков опроса 7 и 8. Возврат с нижнего уровня может происходить также заранее, т. е. пе в микрокоманде М,-, а в микрокоманде М;.-к, для чего в этой микрокоманде выдается микроприказ по выходу 25. а в микрокоманде М; выдается микронриказ по выходу 23. запоен1;ающий подготовку блоков опроса 5 и 6. В остальном работа устройства происходит также, как и в предыдущих режимах.

Универсальность микроподпрограмм нижнего уровня заключается в том. что они содержать в себе литнь те микроприказы, которые являются обними для более широкого класса микропрограмм. Так. например, в процессорах на однородных магнитных матрицах часто иснользуется микронодпрограмма «сложение (в микропрограммах «вычитание, «умножение, «деление и т. д.). При этом операнды для сложения берутся, как правило, из разных функциональных линеек, в ряде случаев их требуется регенерировать в эти линейки, а в ряде случаев не требуется. Можно построить микронодпрограмму нижнего уровня такую, что в первых ДВУХ микрокомандах не выдаются микроприказы, возбуждаюн;ие считывание флнкциональных линеек, тогда эта единственная микроподпрограмма «сложение сможет использоваться во всех перечисленных дгакрокомандах. С верхнего уровня при этом при одновременной работе должны выдаваться микронриказы считывания соответствуютних функциональных линеек, в когопьтх хранятся опора 11г,г, II регенерации (т. г записи с дизьюуткнпон в соответстп 10 функциональные линейки. При этом полд чпются составтгые микрокоманды. Хотя обгцее число адресов памяти лтикрокоманд не сокрашлется, резко сокращается суммарное число микроприказов.

Устройство позволяет упростнть нрограммировапие как путем организации больщего числа микроподпрограмм (включая подпрограммы из одной-двух микрокомаид, что для других устройств невыгодно), так и в ре.зультате повьинения гибкости подпрограмм при совместиой работе обоих уровней. Количество ошибок, донускаемых нри составлении микропрограмм тем большее, чем больше общее число микрокоманд и суммарное число (по всем микрокомандам) микроприказов. При применении устройства сокран1ается как общее чтгсло микрокоманд, так и общее число микронриказов и, как следствие этого, уменьшается количество ошибок и сокращается время на црограммирование, проверку и : тоделирование микропрограмм на универсальной ПВМ. Так, при разработке первого устройства затраты времени на составление микропрограмм сократн.ггось примерно на 10% или на 12 человеко-дней, а при эскизном нроектированин второго Устройства -- на 25% или на 40 человеко-дней.

Быстродействие устройства новьпнается, так как отсутствурот пустые операторы согласования типа безусловного нерехода (которые удлнняют микропрограмму во времени на одну единицу автоматного врел1ени каждый); отсутствуют дополнительные онераторы типа формирования и засылки адреса возврата; при выполнении микропрограммы верхнего уровня возможно одновременное выполнение подпрогра.ммы тина установок или засылок на нижнем (есл1г микронриказы, выдаваемые с обоих уровней совместимы); при выиолпеиии подпрограммы нижнего уровня, не содержащей сигпалов установок и засылок, возможна одновременная выдача этих сигналов с верхнего уровня (еслт микронриказы совместимы).

В описываемом устройстве экономия времени, как минимум в одну-две единицы, получена практически во всех микропрограммах. При вычислении увеличения быстродействия было нринято, что программа состоит из 27% команд типа сложение-вычитание, 10% коАТанд - типа умножение, 5% кодганд - деления, 6% команд - типа сравнение кодов, S% команд - пересылок, 21% - логических онераций и 23% комаьгд - унравления и связи с пультолГ оператора и внешними устройствами. Этот частотный снектр соответствует характеру алгоритмов разработанной УЦВМ. Очевидно, что для других частотных снектров можно получать другие результаты, причем увеличение быстродействия будет тем выше, чем выше доля сложных команд типа умножения, деления или преобразоваинй с индексацией. Вывод снраведлив для класса микрокоманд для нронессоров на О.ММ, однако с небольшими оговорками может быть распространен и на общий случай. Увеличение быстродействия рассчитано по формуле

2(Тк..

1009Й,

ЛБгг

ST,,PK

где ДБ - приращение быстродействия;

Т к -время выполнения к-й команды без применения описываемого устройства;Тк2 - то же, с применением описываемого

устройства;

РК - относительная частота встречи К-й команды.

Формула изобретения

Устройство микропрограммного управления, содержащее первый и второй автоматы Уилкса-Стринджера, причем первая группа разрядных входов первого автомата соединена с первой группой разрядных выходов второго автомата, вторые группы разрядных выходов первого и второго автоматов соединены с адресными входами соответственно второго и первого автоматов, регистр микрокоманд, каждый автомат Унлкса-Стринджера содержит регистр адреса, денлифратор, блок памяти микрокоманд и блок памяти переходов, причем выходы регистра адреса через дешифратор соединены с адресными входами блока памяти микрокоманд, адресные выходы которого соединены с адресными входами блока памяти переходов, а разрядные входы блока памяти микрокоманд и блока памяти переходов соединены соответственно с первой и второй руипами разрядных входов автомата, первая и вторая группы разрядных выходов автомата соединены с разрядными выходами соответственно блока памяти микрокоманд и блока памяти переходов, разрядные входы регистра адреса соединены с адресными входами автомата, а управляющий вход автомата соединен с регистром адреса, отличающееся тем, что, с целью повышения быстродействия устройства, экономичности и гибкости программирования, оно содержит третий и четвертый автоматы Уилкса-Стринджера, первый, второй, третий и четвертый блоки опроса, триггер, первый и второй элементы И, причем третья п четвертая группы разрядных выходов четвертого автомата соединены соответственно с третьей группой разрядных входов и адресными входами третьего автомата, вторая и третья грунны разрядных выходов третьего автомата соединены со вторыми грунпами разрядных входов соответственно второго и иер.чого автоматов, четвертые группы разрядных выходов четвертого и третьего автоматов соединены соответственно с адресными входами третьего и первой группой адресных входов четвертого автоматов, первые группы разрядных выходов четвертого и третьего автоматов

соединены с первыми группами разрядных входов соответственно третьего и второго автоматов, кодовые входы устройства соединены со второй группой адресных входов четвертого автомата, входы регистра микрокоманд соединены с первой группой разрядных выходов первого автомата, выходы первого, второго, третьего, четвертого блоков опроса соединены с управляющими входами соответственно первого, второго, третьего, четвертого автоматов, первые подготовительные входы первого и второго блоков опроса соединены соответственно с выходами второго и первого блоков опроса, вторые подготовительные входы первого и второго блоков опроса соединены соответственно с первым п вторым выходами регистра микрокоманд, третий выход которого соединен со входами запрета первого п второго блоков опроса, выход третьего блока опроса соединен с единичным входом триггера и первым подготовительным входом четвертого блока опроса, выход которого соединен с нулевым входом триггера п первым подготовительным входом третьего блока опроса,

входы запрета третьего и четвертого блоков опроса соединены с четвертым выходом регистра микрокоманд, нятый выход которого соединен с нервымп входами нервого и второго элементов И, вторые входы которых соединены соответственно с еднничным и нулевым выходами трпггера, выходы первого и второго элемсптов И соединены со вторыми нодготовительными входами соответственно четвертого п третьего блоков опроса, тактовые

входы первого-четвертого блоков опроса соединены с тактовым входом устройства, третий и четвертый автоматы содержат первый и второй дополнительные блоки памяти переходов, адресные выходы блока памяти переходов соединепы через первый дополнительный блок памяти переходов с адресными входами второго дополните,тьного блока памяти переходов, разрядные входы первого дополнительного блока и регистра адреса третьего

автомата соединены соответственно с третьей группой и адресными входами этого автомата, третья и четвертая группы разрядных выходов автомата соединены с разрядными выходами соответственно первого и второго дополннтельных блоков памяти переходов, а вторая группа адресных входов четвертого автомата соединена с разрядными входами регистра адреса этого автомата.

11сточники информапин, нринятые RQ внимание при экспертизе:

1.Булей Г. Л икропрограммирование. , 1973, с. 37.

2.Авт. св. 412604, М. Кл.- G 06F. 9/16, 1974.

3.Хассоп С. jNluKponporpaMMHoe управление. Мир, 1973. иып. 1, с. -13, рис. 2, 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления | 1980 |

|

SU881748A1 |

Авторы

Даты

1976-09-15—Публикация

1974-09-02—Подача