команд, группы выходов блоков памяти начальных адресов микрокоманд, адресов возврата и адресов последователь ностей микрокоманд соединены соответ ственно-с первой, второй и третьей группами входов блока элементов ИЛИ, группа выходов которого соединена с группой входов буферного регистра, группа выходов которого соединена с группой входов регистра адреса. 2. Микропрограммное устройство управления, содержащее регистр адреса, регистр возврата, блок памяти и элемент И, причем группа выходов регистра адреса соединена с группой адресных входов блока памяти, первая группа вькодов которого является группой выходов устройства, о т л ичающееся тем, что, с целью расширения области-применения устрой ства за счет обеспечения возможности работы его с составными микроподпро- граммами, оно содержит коммутатор, буферный регистр, регистр эталона, схему сравнения и два элемента И-НЕ, причем первый и второй входы элемента И соединены соответственно с первым выходом блока памяти и с выходом первого элемента И-НЕ, первый, второ входы которого соединены соответстве но с вторьи выходом блока памяти и с выходом схемы сравнения, первая и вторая группы входов которой соедине ны соответственно с второй группой выходов блока памяти и с группой вы1ХОДОВ регистра эталона, группа входо и тактовый вход которого соединены соответственно с второй группой выходов блока памяти и с выходом второго элемента И-НЕ, первый и второй входы которого соединены соответстве но с первым тактовым входом устройства и с третьим выходом блока памяти, четвертый выход которого соединен с первой группой входов коммутатора, управляющий вход и вторая группа входов которого соединены соо ветственно с выходами элемента И и с труппой выходов регистра возврата, тактовый вход и группа входов которого cooTBetCTBeHHo с. вторым тактовым входом устройства и с группой выходов буферного регистра, группа входов и тактовый вход которого соединены соответственно с группой выходов коммутатора и с третьим тактовым входом устройства, вход запуска и четвертый тактовый вход которого 1 5 соединены соответственно с входом сброса и тактовым входом регистра ад реса, группа входов которого соединена с группой выходов буферного регистра. 3. Шкропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр возврата, три элемента И и элемент НЕ, причем первая группа выходов блока памяти является группой выходов устройства, группа выходов регистра адреса соединена с группой адресных входов блока памяти, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности работы его г составными микроподпрограммами, в него введены регистр эталонов, коммутатор, счетчик и схема сравнения, ВЬЕХОД которой соединен с управляющим входом коммутатора, первая и вторая группы входов которого соединены соответственно с второй группой выходов блока памяти и с Труппой выходов регистра возврата, тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой выходов счетчика, счетный вход и группа входов которого соединены соответственно с выходом первого элемента И и с группой выходов коммутатора, тактовый вход счетчика соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с вторым тактовым входом устройства 1 с выходом элемента НЕ, вход которого соединен с первым входом первого элемента И, первым .входом третьего элемента И и с выходом блока памяти, вторая группа выходов которого соединена с группой входов регистра эталонов, тактовьй вход которого соединен с выходом третьего элемента И, второй вход которого соединен с третьим тактовым входом устройства, четвертый тактовый вход и вход сброса которого соединены соответственно с тактовым входом и с входом сброса регистра адреса, группа выходов которого соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой вьрсодов регистра эталонов, пятый тактовый вход устройства и irpynna входов регистра адреса соединены соответственно с вторым входом

первого элемента И и с группой выходов счйтчика.,

4. Микропрограммное устройство управления, содержащее регистр адреса, регистр возврата, блок памяти, элемент И и элемент НЕ, причем первая группа выходов блока памяти соединена с группой выходов устройства, группа адресных входов блока памяти соединена с группой выходов регистра адреса, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности работы его с составными микропрограммами, в него введены три элемента И-НЕ, два триггера, счетчик, буферный регистр и коммутатор, причем выход первого триггера соединен с управляющим входом .коммутатора и с nepBbiM входом первого элемента И-НЕ, второй вход и выход которого соединены соответственно с первым тактовым входом устройства и с первым входом элемента И, второй вход которого соединен с входом запуска устройства, , второй тактовый вход которого соединен с тактовым входом регистра адреса, вход сброса и группа входов кото рого соединены соответственно с входом запуска устройства и с группой выходов буферного регистра, тактовый вход и группа входов которого соединены соответственно с первым тактовым

входом устройства и с группой выходов коммутатора, первая и вторая группы входов которого соединены соответственно с второй группой выходов бло ,ка памяти и с группой выходов регистра возврата, тактовый вход и группа входов которого соединены соответственно с третьим тактовым входом устройства и с группой выходов буферного регистра, вькод и третья группа выходов блока памяти соединены соответственно с первым входом второго элемента И-НЕ и с группой входов счетчика, счетный и тактовый входы которого соединены соответственно с вторым тактовым входом устройства и с выходом второго элемента И-НЕ, второй вход и выход которого соединены соответственно с четвертым тактовым входом устройства и с единичным входом второго триггера, тактовый вход , и выход которого соединены соответственно с выходом элемента И и с первым входом третьего элемента И-НЁ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и с единичным входом первого триггера, вход сброса и тактовый вход которого соединены соответственно с входом запуска устройства и с выходом первого элемента И-НЕ, выход переполнения счетчика соединен с входом элемента НЕ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043653A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1981 |

|

SU985790A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

1. Микропрограммное устройство управления, содержащее блок памяти операционных частей микропрограмм, регистр адреса, регистр возврата, блок памяти адресов .возврата, два элемента И, элемент НЕ, причем первая группа выходов блока памяти операционных частей микропрограмм является группой информационных выходов устройства, группа выходов регистра адреса соединена с группой адресных входов блока памяти операционных частей микропрограмм, группа выходов регистра возврата соединена с группой адресных входов блока памяти адресов возврата, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности работы его с составными микроподпрограммами, в него введены блок памяти адресов последовательностей микрокоманд, буферньй регистр, блок элементов ИЛИ, блок памяти начапьньрс адресов микрокоманд. схема сравнения и блок памяти признаков возврата, причем вход запуска устройства соединен с входом сброса регистра адреса, тактовый вход кото- рого соединен с первым тактовым вхо-. дом устройства, группа выходов регистра адреса соединена с группой адpecHi ix входов блока памяти адресов последовательностей микpoкbмaн ;, первый, второй входы управления чтением которого соединены соответственно с выходом элемента Ilf с входом чтения ф1ока памяти.адресов возврата и с выходом первого элемента И, первый и второй входы которого соединены соответственно с первым выходом блока паi мяти операционных частей микропрограмм и с выходом схемы сравнения, первая и вторая группы входов которой соединены соответственно со второй группой выходов блока памяти операционных частей микропрограмм и с . группой выходов блока памяти признаков возврата, группа адресных входов которого соединена с группой выходов регистра возврата, группа входов и 7 О тактовый вход которого, соединены соответственно с группой информационных входов устройства и с выходом второ:л го элемента И, второй выход блока памяти операционных частей микропрограмм соединен с входом.элемента НЕ, с входом управления чтением блока пямяти начальных адресов микрокоманд и с первым входом второго элемента И, второй вход которого соединен с тактовым входом буферного регистра и вторым тактовым входом устройства, группа информационных входов которого соединена с группой адресных входов блока памяти начальных адресов микро

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления.

Известно устройство микропрограммного управления, содержащее блок памяти микрокоманд, регистр микрокоманд, дешифратор кода микрокоманд и дешифратор кода ветвления, блок управления {lj .

Наиболее близким к-изобретению по технической сущности и достигаемому результату является микропрограммное устройство управления содержащее блок памяти микропрограмм, два регистра адреса, блок проверки уелоВИЙ, элемент НЕ, регистр микроко- манд и блок памяти адресов возврата.

причем первая группа входов блока проверки условий соединена с группой входов устройства, группа выходов которого соединена с первой группой выходов блока памяти микропрограмм, первая, вторая группы адресных входов и вторая группа выходов, которого соединены соответственно с группами выходов первого, второго регистров адреса и с второй группой входов блока проверки условий, выходы которого соединены с группой входов регистра микрокоманд, тактовый вход и группа выходов которого соединены соответственно с выходом блока памяти мик;ропрограмм и с группой адресных вхо дов блока памяти адресов возврата. группа выходов которого соединена с группой входов первого регистра адреса zl. Недостатком известного устройства является невозможность его работы с составными микроподпрограммами. Цель изобретения - расширение области применения устройства за счет обеспечения возможности его работы с составными микроподпрограммами. . Поставленная цель достигается тем, что в микропрограммное устройство управления содержащее блок памяти опера ционных частей микропрограмм, регистр адреса, регистр -возврата, блок памяти адресов возврата, два элемента И, эле мент НЕ, причем первая группа выходов .блока памяти операционных частей микропрограмм является группой информационных выходов устройства, группа выходов регистра адреса соединена с группой адресных входов блока памяти операционных частей микропрограмм, группа выходов регистра возврата соединена с группой адресных входов .блока памяти адресов возврата, введены блок памяти адресов последовательносте микрокоманд, буферный регистр, блок элементов ИЛИ, блок памяти начальных адресов микрокоманд, схема сравнения и блок памяти признаков возврата, при чем вход запуска устройства соединен с входом сброса регистра адреса, тактовый вход которого соединен с первым тактовым входом устройства, группа вькодов регистра адреса соединена с группой адресных входов блока памяти адресов последовательностей микрокоманд, первый, второй входы управления чтением которого соединены соответственно с выходом элемента НЕ, с входов чтения блока п амяти адресов возврата и с выходом первого элемента И, первый, второй входы которого соединены соответственно с пер вым выходом блока памяти операционных частей микропрограмм и с выходом схе мы сравнения, первая, вторая группы входов которой соединены соответстве но с второй группой выходов блока па мяти операционных частей микропрограмм и с,группой выходов блока памя ти признаков возврата, группа адрес.ных входов которого соединена с груп пой выходов регистра возврата, групп

входов и тактовый вход которого соединены соответственно с группой информационных входов устройства и с вы1

рая группа входов которого соединены соответственно с вьпсодами элемента И и с группой выходов регистра воз254 . ходом второго элемента И, второй выход блока памяти операционных частей микропрограмм соединен с входом элемента НЕ, с входом управления чтением блока памяти начальных адресов микрокомард и с первым входом второго элемента И, второй вход которого соединен с тактовь м входом буферного регистра и вторым тактовым входом устройства, группа информационных входов которого соединена с группой адресных входов блока памяти начальных адресов микрокоманд, группы выходов блоков, памяти начальных адресов микрокоманд, адресов возврата и адресов последовательностей микрокоманд соединены соответственно с первой, второй и третьей группами входов блока элементов ИЛИ, группа выходов которого соединена с группой входов буферного регистра, группа выходов которого соединена с группой входов регистра адреса. В микропрограммное устройство управления по второму варианту, содержащее регистр адреса, регистр возврата, блок памяти иэлемент И, причем группа выходов регистра адреса соединена с группой адресных входов блока памяти, первая группа выходов которого является группой выходов устройства, введены коммутатор, буферный регистр, регистр , схема срав1 ения и два элемента И-НЕ, причем первый, второй входы элемента И соединены соответственно с первым выходом блока памяти и с выходом первого элемента И-НЕ, первый, второй входы которого соединены соответственно с вторым выходом.блока памяти и с вьсходом схемы, сравнения, первая, вторая группы входов которой соединены соответственно с второй группой выходов блока памяти и с группой выходов регистра эталона, группа входов и тактовый вход которого соединены соответственно с второй группой выходов блока памяти и с выходом второго элемента-И-НЕ, первый, второй входы которого соединены соответственно с первым тактовым входом устройства и с третьим выходом блока памяти, четвертый выход которого соединен с первой группой входов коммутатора, управляющий вход и втоврата, тактовый вход и группа входов которого соединены соответственно с вторым тактовым входом устройства и с группой выходов буферного регистра, группа входов и тактовый вход которого соединены соответственно с группой выходов коммутатора и с третьим тактовым входом устройства, вход запуска и четвертый тактовый вход которого соединены соответствен но с входом сброса-и тактовым входом регистра адреса, группа входов которого соединена с группой вьрсодов буферного регистра, В микропрограммное устройство, управления, по третьему варианту, содер жащёе блок памяти, регистр адреса, регистр возврата, три элемента И и элемент НЕ, причем первая.группа выходов блока памяти я.вляется группо выходов устройства, группа выходов регистра адреса соединена с группой адресньк входов блока памяти, введены регистр эталоно.в, коммутатор, сче чик и схема сравнения, выход которой соединен с управлякицим входом коммут тора, первая и вторая группы входов которого соединены соответственно с второй группой выходов блока памяти и с группой выходов регистра возврата тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой вьрсодов счетчика, счетный вход и группа входов которого соедииены соответственно с вькодом первого элемента И и с группой вьрсодов коммутатора, тактовый вход счетчика соединен с выходом второго элемента И, первый и второй входы которого соединены, соответственно с вторым тактовым входом устройства и с выходом элемента НЕ, вход которого соединен с Первым входом первого эле мента И, первым входом третьего элемента И и с выходом блока памяти, вторая группа -выходов которого соеди нена с группой входов регистра этало на, тактовый вход которого соединен с выходом третьего элемента И, второй вход которого соединен стретьим тактовым входом устройства, четвертый тактовый вход и вход сброса которого соединены соответственно с та товым входом и с входом сброса регистра адреса, группа выходов которого соединена спервой группой входов схемы сравнения, вторая группа входо

которой соединена с группой вькодов регистра эталона, пятый тактовый вход устройства и группа входов регистра адреса соединены соответственно с вторым входом первого элемента И и с . группой выходов счетчика.

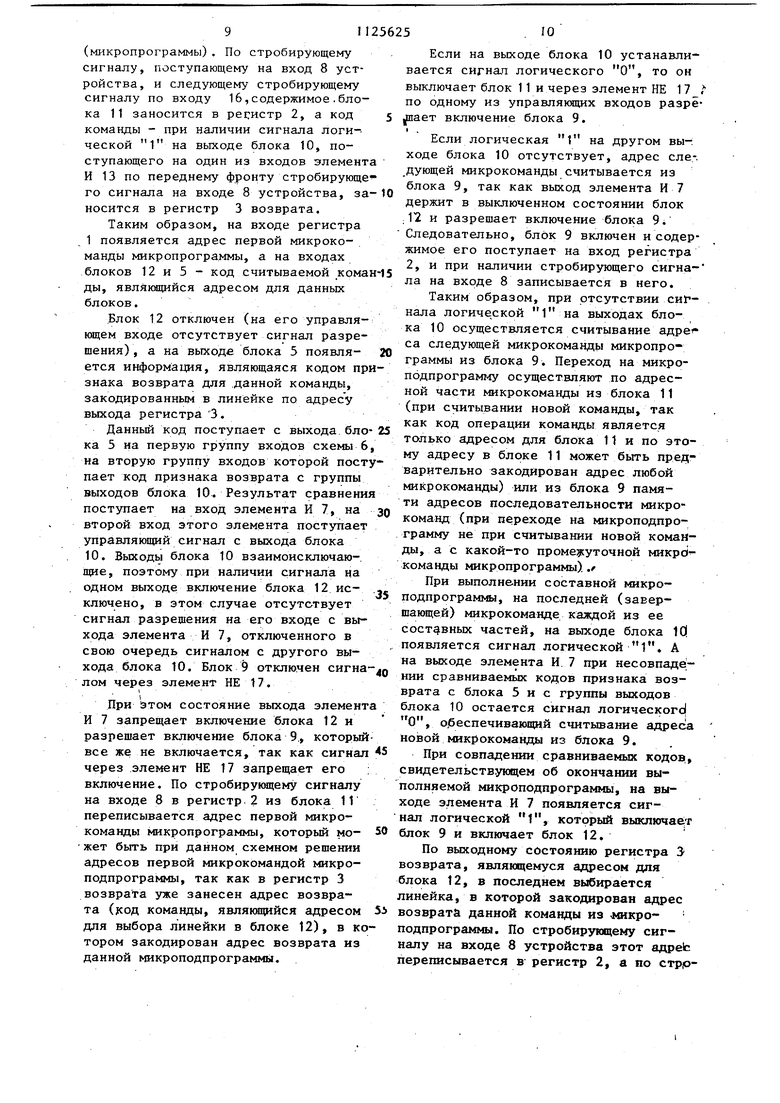

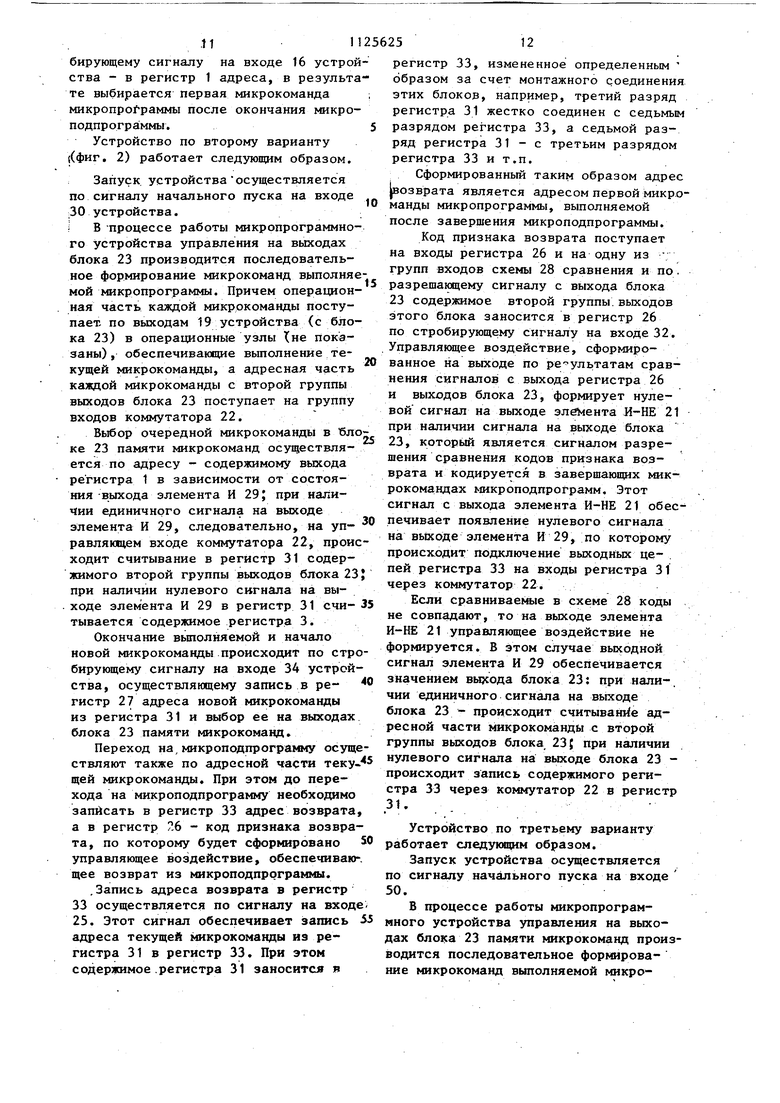

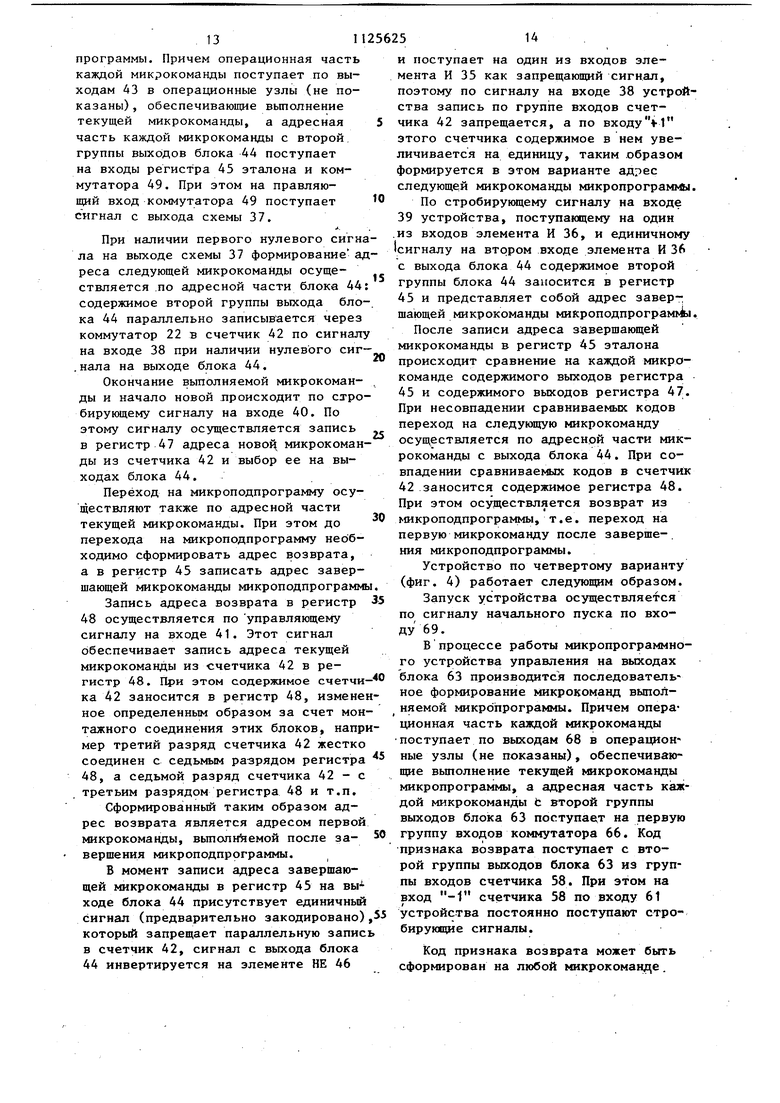

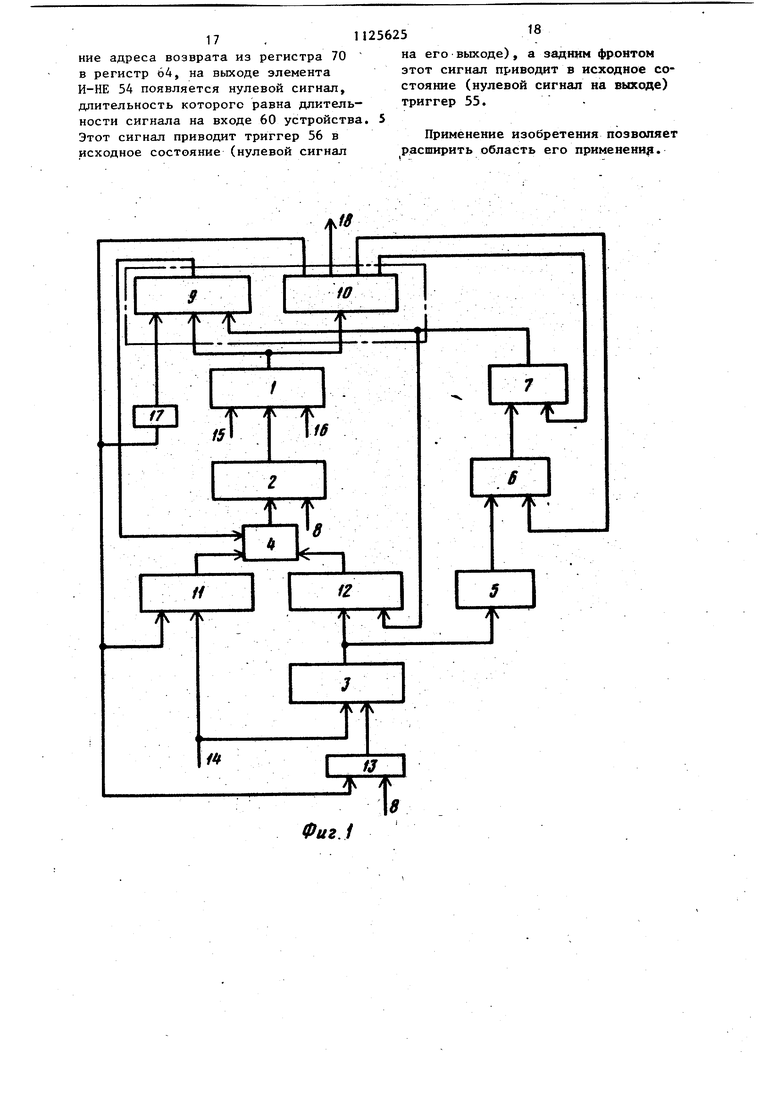

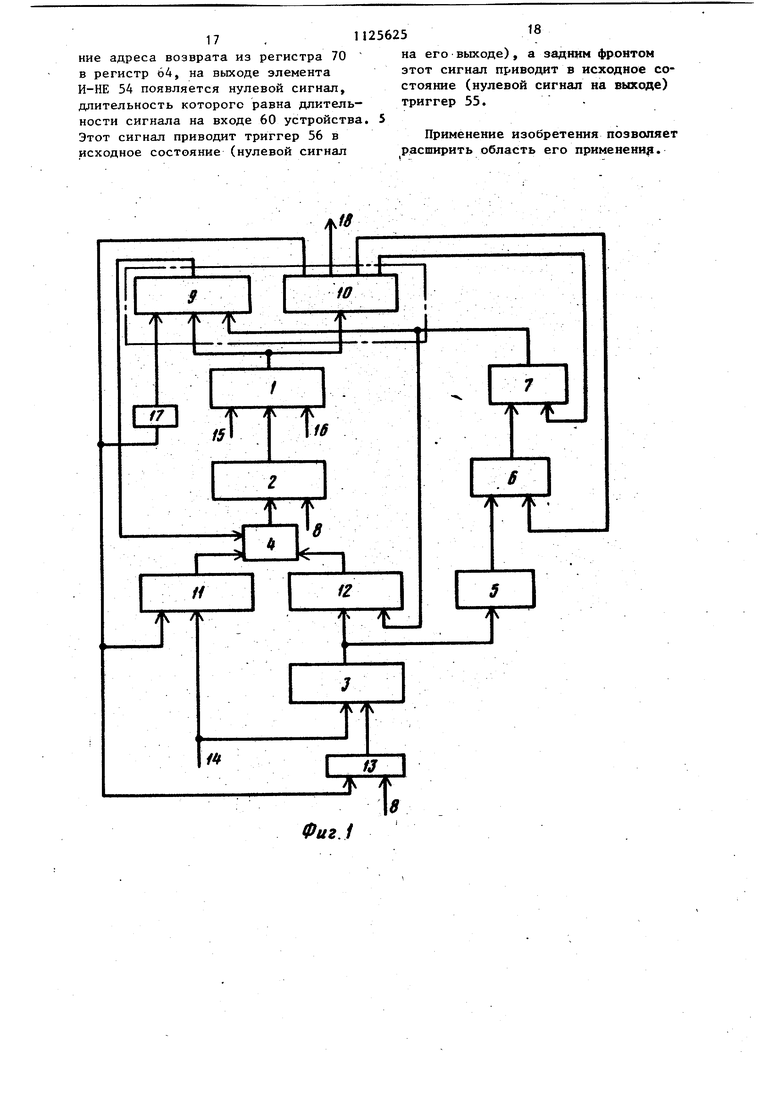

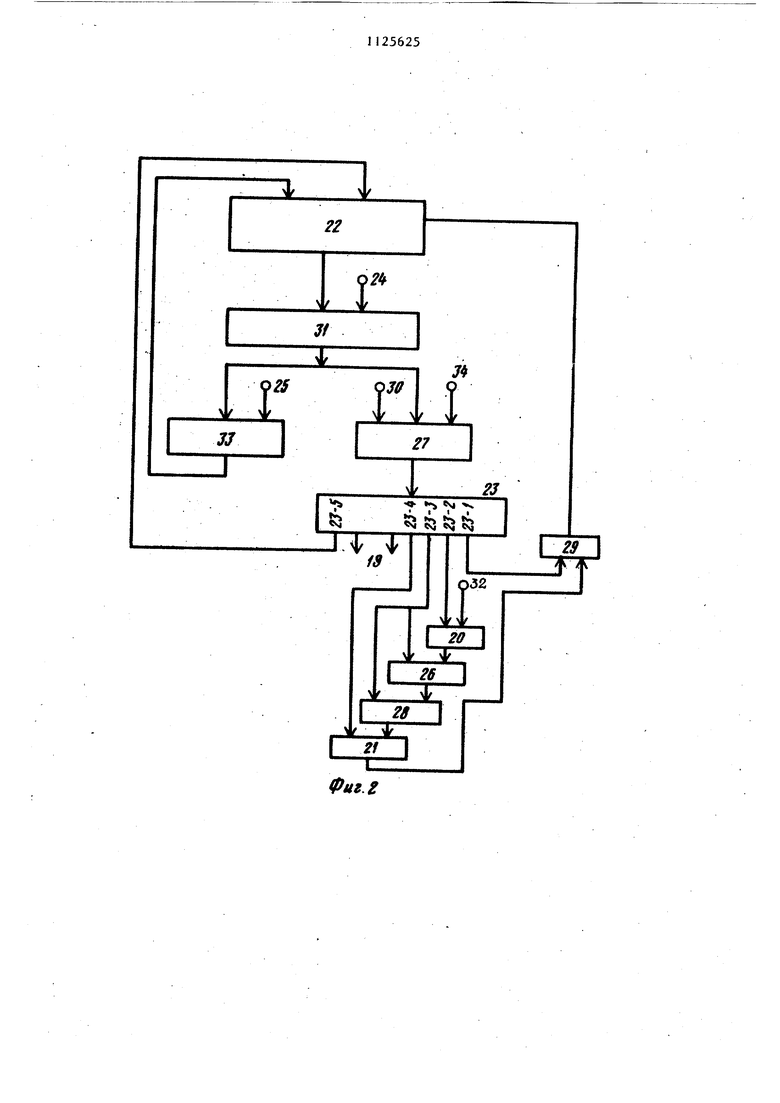

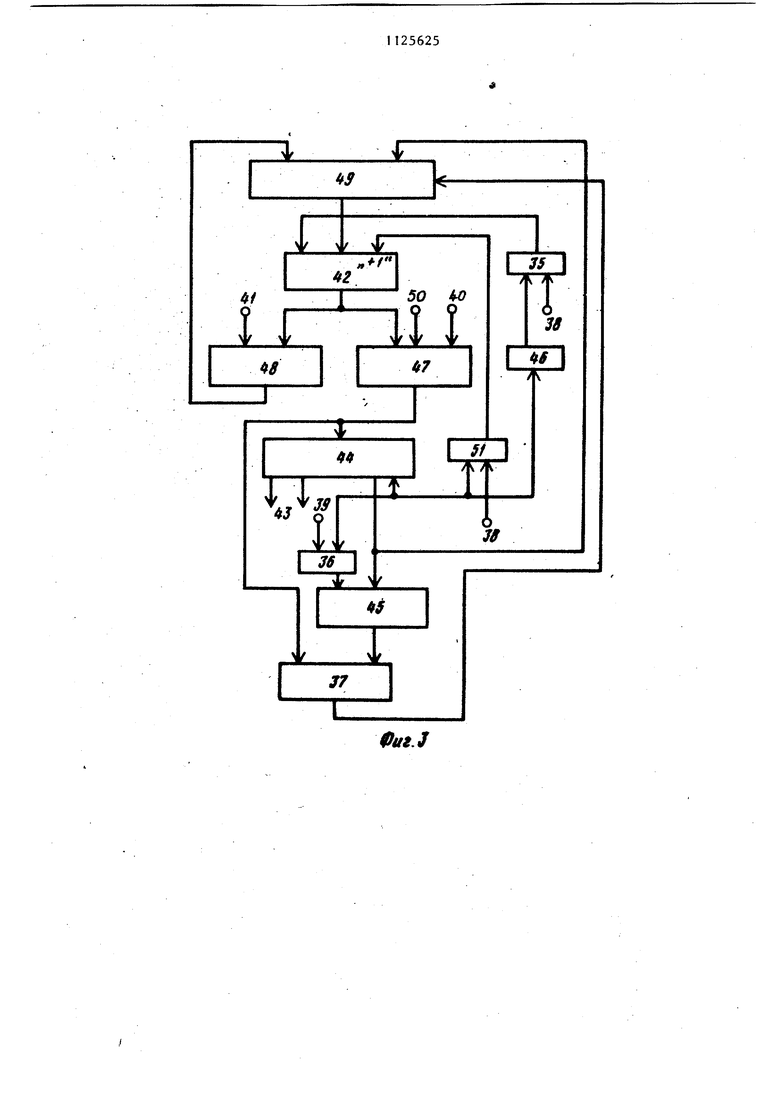

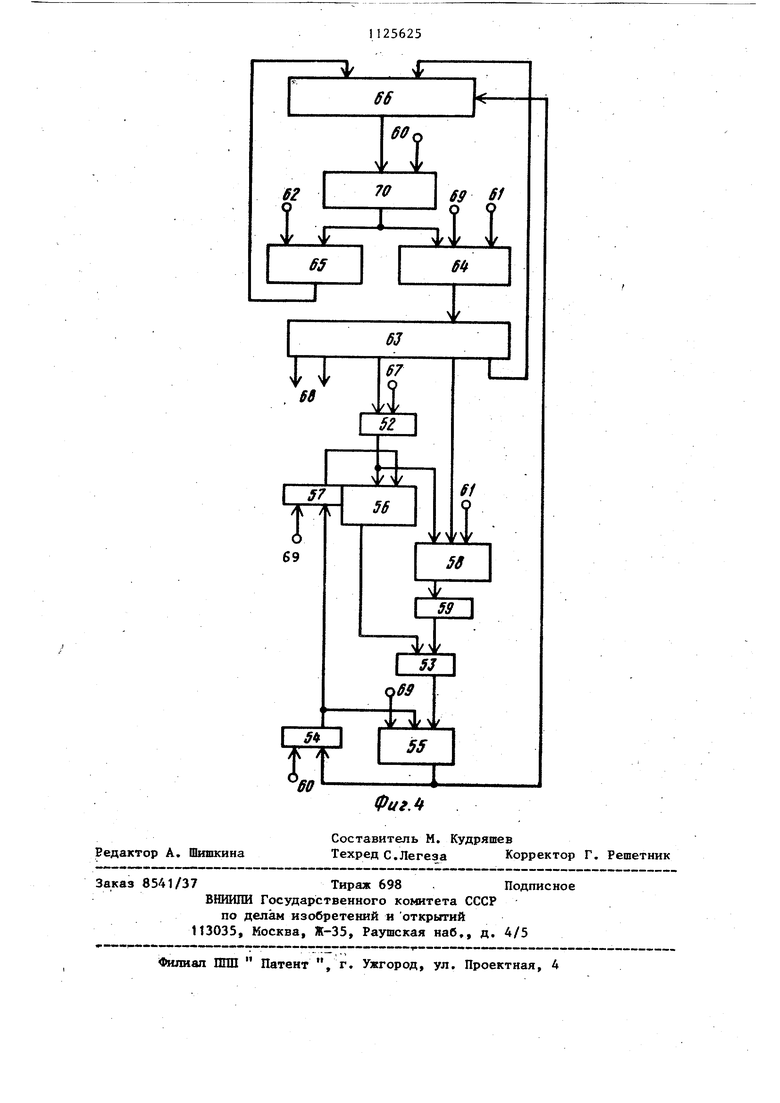

В -микропрограммное устройство управления по четвертому варианту, содержащее регистр адреса, регистр возврата, блок памяти, элемент И и элемент НЕ,причем первая группа выходов блока памяти соединена с группой выходов устройства, группа адресных входов блока памяти соединена с группой выходов регистра адреса, введены три элемента И-НЕ, два.триггера,счетчик ,. буферный регистр и коммутатор, причем выход первого триггера соеди- нен с управляющим входом коммутатора и с первым входом первого элемента , второй вход и выход которого соединены соответственно с первым тактовым входом устройства и с первым входом элемента И, .второй вход которого соединен с входом запуска устройства, второй тактовый вход которого соединен с тактовым входом регистра адреса, вхОд сброса и группа входов которого соединены соответственно с входом запуска устройства и с группой вькодов буферного регистра, тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой выходов коммутатора, первая и вторая группы входов которого соединены, соответственно с второй группой вькодов блока памяти и с группой выходов регистра.возврата, тактовый вход л группа входов которого соединены соответственно с третьим тактовым входом, устройства и с группой выходов буферного регистра, выход и третья группа выходов блока памяти соединены соответственно с первым входом второго элемента И-НЕ и с группой входов счетчика, счетный и тактовый входы которого соединены соответственно о вторым тактовым входом устройства и с выходом второго элемента И-НЕ, второй вход и выход которого соединены соответственно с четвертым т.актовым входом устройства и с единичным входом второго триггера, тактовьй вход и выход которого соеинен соответственно с выходом элемента И и с первым входом третьего элемента И-НЕ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и с едини 1ным входом первого триггера, вход сброса и тактовый вход которого соединены соответственно-с входом запуска.устрой ства и с выходом первого элемента , выход переполнения счетчика соед нен с входом элемента НЕ, На фиг, 1-4 предс-тавлена. блок-схе ма микропрограммного устройства упра ления (варианты исполнения), Устройство по первому варианту (фиг. 1) содержит регистр 1 адреса, буферный регистр 2, регистр 3 возвра та, блок элементов ИЛИ 4, блок 5 пам ти признаков возврата, схему 6 сравнения, элемент И 7, тактовьш вход 8 устройства, блок 9 памяти адресов-по следовательностей микрокоманд, блок 10 памяти операционных частей микропрограмм, блок 11 памяти начальных адресов микрокоманд, блок 12 памяти адресов возврата, элемент И 13, груп пу информационных входов 14 устройства, вход 15 запуска устройства , тактовый вход 16 устройства, элемент НЕ 17, группу информационных выходов 18 устройства. Устройство по второму варианту (фиг. 2) содержит группу выходов 19 устройства, элементы И-НЕ 20 и 21, коммутатор 22, блок 23 памяти, такто вые входы. 24 и 25 устройства, регист 26 талонов, регистр 27 адреса, 28 сравнения, элемент И 29, вход 30 запуска устройства, буферный ре,гистр 31, тактовый вход 32 устройства, регистр 33 воззрата, тактовый вход 34 устройства. Устройство по третьему варианту (фиг. 3) содержит элементы И 35 и 36 схему 37 сравнения, тактовые входы 38-41 устройства, счетчик 42, группу выходов 43 устройства, блок 44 памяти, регистр 45 эталонов, элемент НЕ 46, регистр 47 адреса, регистр 48 возврата, коммутатор 49, вход 50 запуска устройства элемент И 51. Устройство по червертоку вариант (фиг. 4) содержит элементы И-НЕ 52 триггеры 55 и 56, элемент И 57,счетчик 58, элемент НЕ 59, текстовые входы 60-62 устройства,блок 63 памяти, регистр 64 адреса, регистр 65 возврата, коммутатор 66, тактовый вход 67 устройства, группу вьпсодов 68 устройства, вход 69 запуска устройства, буферный регистр 70. Устройство по первому варианту (фиг.1) работает следующим образом , Запуск устройства осуществляется по сигналу начального пуска на входе 15 устройства, при этом сигнал начального пуска поступает на вход установки в нуль регистра 1. Регистр 1 устанавливается в нулевое состояние, т.е. в нем устанавливается нулевой адрес, по которому выбирается нулевая линейка в блоках 9 и 10, в которой закодирована микрокоманда, выполняемая по этому адресу. В процессе работы микропрограммного устройства управления на выходах блоков 9 и 10 производится последовательное формирование микрокоманд выполняемой микропрограммы. При этом операционная часть каждой микрокоманды поступает по выходам 18 устройства с блока 10 в операционные узлы (не показаны), обеспечивающие выполнение текущей микрокоманды, а адресная часть каждой микрокоманды с блока 9 поступает на вход регистра 2 адреса и по стробирующему сигналу на входе 8 устройства запишется в него (в регистр 2). Далее эта адрес- ная часть поступает на вход регистра 1 адреса. При этом блоки 11 и 12 памяти отключены, так как на их управля- кицих входах отсутствуют сигналы разрешения. Окончание выполняемой и начало новой микрокоманды осуществляется по стробирующему сигналу,, поступакщему на вход 16 устройства .-(управляющий вход регистра 1 адреса) и обеспечивающему смену адреса в регистре 1 адреса, и следовательно, выбор новой линейки в блоках 9 и 10, т.е. выбор новой микрокоманды. При этом блок 5 прстоянно включен, т.е. на его выходе постоянно присутствует информация. При появлении на входах блоков 9 и 10 адреса микрокоманды, обеспечивающей считывание новой команды, на- выходе блока 10 появляется сигнал логической 1, который выключает через элемент НЕ 17 блок 9 и включает блок 11.Код.команды с группы входов 14 поступает на адресный вход блока 11 и на вход в регистр 3 возврата. На выходе блока 11 появляется информация, соответствующая адресу, представленному кодом операции команды и являющемуся адресом первой микрокоманды считываемой команды 911 (микропрограммы). По стробирующему сигналу, поступающему на вход 8 устройства, и следующему стробирующему сигналу по входу 16,содержимое.блока 11 заносится в реггистр 2, а код команды - при наличии сигнала логической 1 на выходе блока 10, поступающего на один из входов элемент И 13 по переднему фронту стробирующе го сигнала на входе 8 устройства, за носится в регистр 3 возврата. Таким образом, на входе регистра 1 появляется адрес первой микрокоманды микропрограммы, а на входах блоков 12 и 5 - код считываемой кома ды, являкяцийся адресом для данных блоков. Блок 12 отключен (на его управлякйцем входе отсутствует сигнал разрешения), а на выходе блока 5 появляется информация, являющаяся кодом пр знака возврата для .данной команды, закодированньм в линейке по адресу выхода регистра 3. Данньй код поступает с выхода бло ка 5 на первую группу входов схемы 6 на вторую группу входов которой пост пает код признака возврата с группы выходов блока 10. Результат сравнени поступает на вход элемента И 7, на второй вход этого элемента поступает управляющий сигнал с выхода блока 10. Выходы блока 10 взаимоисключаю-. щие, поэтому при наличии сигнала на одном выходе включение блока 12 исключено, в этом случае отсутствует сигнал разрешения на его входе с выхода элемента И 7, отключенного в свою очередь сигналом с другого выхода блока 10. Блок 9 отключен сигна лом через элемент НЕ 17, При isTOM состояние выхода элемент И 7 запрещает включение блока 12 и разрешает включение блока 9., который все же не включается, так как сигнал через элемент НЕ 17 запрещает его включение. По стробирукнцему сигналу на входе 8 в регистр 2 из блока 11 переписывается адрес первой микрокоманды микропрограммы, который мо- жет быть при данном схемном решении адресов первой микрокомандой микроподпрограммы, так как в регистр 3 возврата уже занесен адрес возврата (код команды, являкицийся адресом для выбора линейки в блоке 12), в ко тором закодирован адрес возврата из данной микроподпрограммы. 5 Если на выходе блока 10 устанавливается сигнап логического О, О , то он выключает блок 11 и через элемент НЕ 17 по одному из управлякяцих входов разре ает включение блока 9. Если логическая 1 на другом вы-: ходе блока 10 отсутствует, адрес еле-. дующей микрокоманды считывается из блока 9, так как выход элемента И 7 держит в выключенном состоянии блок 12 и разрешает включение блока 9. Следовательно, блОк 9 включен и содержимое его поступает на вход регистра 2, и при наличии стробирующего сигнала на входе 8 записывается в него. Таким образом, при отсутствии сигнала логической 1 на выходах блока 10 осуществляется считывание адре са следующей микрокоманды микропрограммы из блока 9. Переход на микроподпрограмму осуществляют по адресной части микрокоманды из блока 11 (при считывании новой команды, так как код операции команды является только адресом для блока 11 и по этому адресу в блоке 11 может быть предварительно закодирован адрес любой микрокоманды) или из блока 9 памяти адресов последовательности микрокоманд (при перекоде на микроподпрограмму не при считывании новой команды, а с какой-то промежуточной микрО команды микропрограммы)./ При выполнении составной микроподпрограм1«л, на последней (завершающей) микрокоманде каждой из ее составных частей, на выходе блока Ю появляется сигнал логической 1. А на выходе элемента И 7 при несовпадении сравниваемых кодов признака возврата с блока 5 и с группы выходов блока 10 остается сигнал логического О, о.беспечивающий считывание адрес;а новой микрокоманды из блока 9. При совпадении сравниваемых кодовг, свидетельствующем об окончании выполняемой микроподпрограммы, на выходе элемента И 7 появляется сигнал логической 1, который выключает блок 9 и включает блок 12. По выходному состоянию регистра Э возврата, являющемуся адресом для блока 12, в последнем выбирается линейка, в которой закодирован адрес возврата данной команды из «икроподпрограммы. По стробирующему сигналу на входе 8 устройства этот адреЬ переписывается в регистр 2, а по стр,о111бирующему сигналу на входе 16 устрой ства - в регистр 1 адреса, в результа те выбирается первая микрокоманда микропрограммы после окончания микроподпрогра:ммы. Устройство по второму варианту ((фиг. 2) работает следзтощим образом. Запуск устройстваосуществляется по сигналу начального пуска на входе 30 устройства. В процессе работы микропрограммного устройства управления на выходах блока 23 производится последовательвое формирование микрокоманд выполняе мой микропрограммы. Причем операционная часть каждой микрокоманды поступает, по выходам 19 устройства (с блока 23) в операционные узлы Тне показаны) , обеспечивающие выполнение текущей микрокоманды, а адресная часть каждой микрокоманды с второй группы выходов блока 23 поступает на группу входов коммутатора 22. Выбор очередной микрокоманды в бло ке 23 памяти микрокоманд осуществляется по адресу - содержимому выхода регистра 1 в зависимости от состояния выхода элемента И 29; при наличии единичного сигнала на выходе элемента И 29, следовательно, на уп равлякщем входе коммутатора 22, прои ходит считывание в регистр 31 содержимого второй группы выходов блока 23 при наличии нулевого сигнала на вы. ходе элемента И 29 в регистр 31 считывается содержимое регистра 3. Окончание вьшолняемой и начало новой микрокоманды происходит по стр бирующему сигналу на входе 34 устрой ства, осуществляющему запись в регистр 27 адреса новой микрокоманды из регистра 31 и выбор ее на выходах блока 23 памяти микрокоманд. Переход на, микроподпрограмму осущ ствляют также по адресной части теку щей микрокоманды. При этом до перехода на микроподпрограмму необходимо записать в регистр 33 адрес возврата а в регистр 26 - код признака возвра та, по которому будет сформировано управляющее воздействие, обеспечиваю щее возврат из микроподпрограммы. ,Запись адреса возврата в регистр 33 осуществляется по сигналу на вход 25. Этот сигнал обеспечивает запись адреса текущей микрокоманды из регистра 31 в регистр 33. При этом содержимое.регистра 31 заносится в 25 регистр 33, измененное определенным образом за счет монтажного соединения этих блоков, например, третий разряд регистра 31 жестко соединен с седьмым разрядом регистра 33, а седьмой разряд регистра 31 - с третьим разрядом регистра 33 и т.п. Сформированный таким образом адрес |возврата является адресом первой микроманды микропрограммы, выполняемой после завершения микроподпрограммы. Код признака возврата поступает на входы регистра 26 и на одну из 28 сравнения и по разрешакяцему сигналу с выхода блока сигналу 23 содержимое второй группы.выходов этого блока заносится в регистр 26 по стробирующему сигналу на входе 32. Управлякицее воздействие, сформированное на выходе по результатам сравнения сигналов с выхода регистра 26 и выходов блока 23, формирует нулевой сигнал на выходе элемента И-НЕ 21 при наличии сигнала на выходе блока 23, который является сигналом разрешения сравнения кодов признака возврата и кодируется в завершающих микрокомандах шкpoпoдпpoГрамм. Этот сигнал с выхода элемента И-НЕ 21 обеспечивает появление нулевого сигнала на выходе элемента И 29, по которому происходит подключение выходных цепей регистра 33 на входы регистра 31 через коммутатор 22. Если сравниваемые в схеме 28 коды не совпадают, то на выходе элемента И-НЕ 21 управляющее воздействие не формируется. В этом случае выходной сигнал элемента И 29 обеспечивается значением выхода блока 23: при нали-. чии единичного сигнала на выходе блока 23 - происходит считывание адресной части микрокоманды с второй группы выходов блока 23{ при наличии нулевого сигнала на выходе блока 23 происходит запись содержимого регистра 33 через коммутатор 22 в регистр 31. Устройство по третьему варианту работает следующим образом. Запуск устройства осуществляется по сигналу начального пуска на входе 50. В процессе работы микропрограммного устройства управления на выходах блока 23 памяти микрокоманд производится последовательное формирование микрокоманд выполняемой микропрограммы. Причем операционная часть каждой микрокоманды поступает по выходам 43 в операционные узлы (не показаны) , обеспечивающие вьтолнение текущей микрокоманды, а адресная часть каждой микрокоманды с второй, группы выходов блока 44 поступает на входы регистра 45 эталона и коммутатора 49. При этом на правляющий вход коммутатора 49 поступает сигнал с выхода схемы 37. При наличии первого нулевого сигна ла на выходе схемы 37 формированиеад реса следующей микрокоманды осуществляется .по адресной части блока 44 содержимое второй группы выхода бло ка 44 параллельно записывается через коммутатор 22 в счетчик 42 по сигналу на входе 38 при наличии нулевого сиг .нала на выходе блока 44. Окончание выполняемой микрокоманды и начало новой .происходит по стро бирующему сигналу на входе 40. По этому сигналу осуществляется запись в регистр 47 адреса HOBof микрокоман ды из счетчика 42 и выбор ее на выходах блока 44, Переход на микроподпрограмму осуществляют также по адресной части текущей микрокоманды. При этом до перехода на микроподпрограмму необходимо сформировать адрес возврата, а в регистр 45 записать адрес заверщающей микрокоманды микроподпрограмм Запись адреса возврата в регистр 48 осуществляется по управляющему сигналу на входе 41. Этот сигнал ббеспечивает запись адреса текущей микрокоманды из счетчика 42 в регистр 48. При этом содержимое счетчи ка 42 заносится в регистр 48, измене ное определенным образом за счет мон тажного соединения этих блоков, напр мер третий разряд счетчика 42 жестко соединен с седьмым разрядом регистра 48, а седьмой разряд счетчика 42 - с третьим разрядом регистра 48 и т.п. Сформированный таким образом адрес возврата является адресом первой микрокоманды, вьтолн емой после завершения микроподпрограммы. В момент записи адреса завершающей микрокоманды в регистр 45 на выходе блока 44 присутствует единичный сигнал (предварительно закодировано) которыЙ запрещает параллельную запис в счетчик 42, сигнал с выхода блока 44 инвертируется на элементе НЕ 46 и поступает на один из входов элемента И 35 как запрещающий сигнал, поэтому по сигналу на входе 38 устройства запись по группе входов счетчика 42 запрещается, а по входу41 этого счетчика содержимое в нем увеличивается на единицу, таким .образом формируется в этом варианте адрес следующей микрокоманды микропрограммы. По стробирующему сигналу на входе 39 устройства, поступающему на один из входов элемента И 36, и единичному сигналу на втором входе элемента И 36 с выхода блока 44 содержимое второй группы блока 44 заносится в регистр 45 и представляет собой адрес завер-: шающей микрокоманды микроподпрограмг. После записи адреса завершающей микрокоманды в регистр 45 эталона происходит сравнение на каждой микрокоманде содержимого выходов регистра 45 и содержимого выходов регистра 47. При несовпадении сравниваемых кодов переход на следукицую микрокоманду осуществляется по адресной части микрокоманды с выхода блока 44. При совпадении сравниваемых кодов в счетчик 42 заносится содержимое регистра 48. При этом осуществляется возврат из икроподпрограммы, т.е. переход на первую микрокоманду после заверще-. ния микроподпрограммы. Устройство по четвертому варианту (фиг. 4) работает следующим образом. Запуск устройства осуществляется по сигналу начального пуска по вхоДУ 69. В процессе работы микропрограммного устройства управления на выходах блока 63 производится последовательное формирование микрокоманд выполняемой микропрограммы. Причем операционная часть кгикдой микрокоманды поступает по выходам 68 в операционные узлы (не показаны), обеспечивающие вьтолнение текущей микрокоманды микропрограммы, а адресная часть каждой микрокоманды t второй группы выходов блока 63 поступае т на первую группу входов коммутатора 66. Код признака возврата поступает с второй группы выходов блока 63 из группы входов счетчика 58. При этом на вход -1 счетчика 58 по входу 61 устройства постоянно поступают стробирукицие сигналы. Код признака возврата может быть сформирован на любой микрокоманде. микропрограммы до перехода на микроподпрограмму, но удобнее его формиро вать на той микрокоманде, на которой осуществляется переход на микроподпрограмму (так сделано в .предлагаемом устройстве), так как в этом случае число, определяющее код признака возврата (т.е. .количество микр команд до момента окончания микроподпрограммы) , равно количеству микрокоманд микроподпрограммы минус еди ница (т.е. нет необходимости учитывать количество микрокоманд от той микрокоманды, на которой сформирован .код признака возврата, до завершающе микрокоманды микроподпрограммы). При этом до перехода на микроподпрограмму необходимо записать в pe-f гистр 65 адрес возврата. Запись адре са возврата в регистр 65 осуществляется по управляющему сигналу на входе 62, обеспечивающему запись адреса текущей микрокоманды из регистра 70 в регистр 65. При этом содержимое регистра 70 заносится в регистр 65 возврата, измененное определ.енным образом за счет монтажного соединения этих блоков, например третий разряд регистра 70 адреса жестко сое динен с седьмым разрядом регистра 65 а седьмой разряд регистра 70 - с тре тьим разрядом регистра 65 и т.п. ,Сформированный таким образом адре iвозврата является адресом первой микрокоманды микропрограммы, выполняемои после завершения микроподпрограм мы. По сигналу начального пуска (по входу 69 устройства) в регистр 64 установится адрес начальной микрокоманды, по которому в блоке 63 выбирается определенная микрокоманда. Триггер 56 устанавливается сигналом начального пуска на одном из его вхо дов (через элемент И 57) в исходное состояние, которое запрещает прохожд ние сигнала с выхода элемента НЕ 59 на выход элемента И-НЕ 53, при этом триггер 55 устанавливается сигналом начального пуска по входу 69 также в исходное .состояние, при котором на его выходе, а следовательно, на уп равляющем входе коммутатора 66, уста навливается нулевой сигнал. При этом формирование адреса следующей микрокоманды происходит по адресной части микрокоманды с блока 63. Этот адрес через коммутатор 66 записывается по 2516 сигналу на входе 60 в регистр 70. Итак, на вь1ходе блока 63 появляется (так предварительно закодировано в блоке 63) единичный сигнал. Этот сигнал означает необходимость записи кода признака возврата в счетчик 58, По переднему фронту сигнала на входе 67 на выходе элемента 52 появляется нулевой сигнал, обеспечивающий запись в счетчик 58 содержимого второй группы выходов блока 63-. По заднему фронту сигнала на входе 67 на выходе триггера 56 появляется единичный сигнал, разрешающий прохождение сигнала с выхода счетчика 58 через элемент НЕ 59 и элемент И-НЕ 53 a вход триггера 55. После записи кода признака возврата в счетчик 58 состояние в последнем с приходом оче- редного сигнала по входу -1 уменьшается на единицу на каждой микрокоманде. При достижении теперь в счетчике 58 нулевого состояния при выборе предпоследней микрокоманды микроподпрограммы и появлении следую щего сигнала на входе 61 (вход -1 счетчика 58) - переход на последнюю микрокоманду микроподпрограммы - на выходе счетчика 58 появляется нулевой сигнал. Инвертированный этот сиг нал поступает на второй вход элемента И-НЕ 53, на первом входе ко- торого присутствует единичный сигнал с выхода триггера 56. На выходе элемента И-НЕ 53 появляется нулевой сигнал, длительность которого равна длительности стробирующего сигнала по входу 61 устройства. Нулевой сигнал с выхода элемента И-НЕ 53 устанавливает триггер 55 в состояние, при котором на его выходе появляется единичный сигнал, а следовательно, и на управляющем входе коммутатора 66 также.появляется единичный сигнал, по которому через коммутатор 66 содержимое регистра 65 по сигналу 60 записывается в регистр 70. Это содержимое регистра 65, занесенное в него до перехода на микроподпрограмму, является адресом микрокоманды, выполняемой первой после завершения микроподпрограммы, и заносится оно в регистр 70 на завершающей микрокоманде микроподпррграммы. До выполнения завершающей микрокоманды микроподпрограммы и поступлении очередного сигнала на вход 61 устройства, обеспечивающего считывание адреса возврата из регистра 70 в регистр 64, на выходе элемента И-НЕ 54 появляется нулевой сигнал, длительность которого равна длительности сигнала на входе 60 устройства Этот сигнал приводит триггер 56 в исходное состояние (нулевой сигнал

Фиг.1 1125 62518 на его выходе), а задним фронтом этот сигнал приводит в исходное состояние (нулевой сигнал на выходе) триггер 55. Применение изобретения позволяет расширить область его применения.

Фиг. г

0tii.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-23—Публикация

1983-07-15—Подача