1

Изобретение относится к вычислительной технике.

Известно оперативное запоминающее устройство, в котором ячейка памяти проверяется перед обраш,ением к ней, или все ячейки памяти проверяются поочередно в паузах между внешними обращениями к устройству 1. Такой предварительный контроль может быть осуществлен последовательной записью и считыванием какой-либо информации из ячейки памяти и сравнением записанной и считанной информации с помощью блока контроля.

Известно также запоминающее устройство, в котором для целей контроля используется код Хэмминга, позволяющий корректировать одну и обнаруживать две ошибки 2.

Недостатком указанных устройств является отсутствие контроля адресного тракта. Типичными неисправностями адресного тракта, например, полупроводниковых устройств являются неисправности, выражающиеся в том, что информация либо не выбирается, либо выбирается несколько слов, содержимое которых объединяется па выходных шинах по схеме логического ИЛИ.

Наиболее близким техническим решением к данному изобретению является устройство, содержащее регистр адреса, подключенный к дешифратору адреса, выходы которого соединены с адресными входами блока запоминающих матриц, управляющие шины, регистр слова, подключенный к усилителям считываниязаписи, блок контроля информации, соединенный с выходами регистра слова и регистра адреса, и блок выработки сигнала ошибки 3. В нем применен метод контроля адресного тракта устройства с помощью контрольного кода адреса, сопровождающего каждое слово информации в устройстве при хранении, а также защита каждого слова суммарным контрольным кодом слова и адреса, по которому это слово хранится.

Недостатком этого устройства является низкая эффективность контроля адресного тракта, не позволяющая выявлять многократные ошибки, возникающие при отказах элементов адресного тракта, и вследствие этого недостаточная надежность устройства.

Целью изобретения является повышение падежности устройства и эффективности контроля адресного тракта.

Это достигается тем, что устройство содержит блоки вычитания инверсных и прямых кодов адреса, входы которых соединены попарно

и подключены соответственно к одной из управляющих шин и выходам регистра адреса и регистра слова, элементы НЕ, входы которых соединены с выходом блока вычитания инверсных кодов адреса, элементы И, входы которых подключены соответственно к выходам

элементов НЕ и выходам регистра адреса, сумматор, входы которого сЪедннеиы соответственно с выходами элемеит9в И и блока вычитания ирямых кодовг аДрейа, а выход - со входом блока выработки сигнала ошибки, доиолнительный регистр адреса, вход которого подключен к выходу сумматора, а выход соединен со входом регистра адреса.

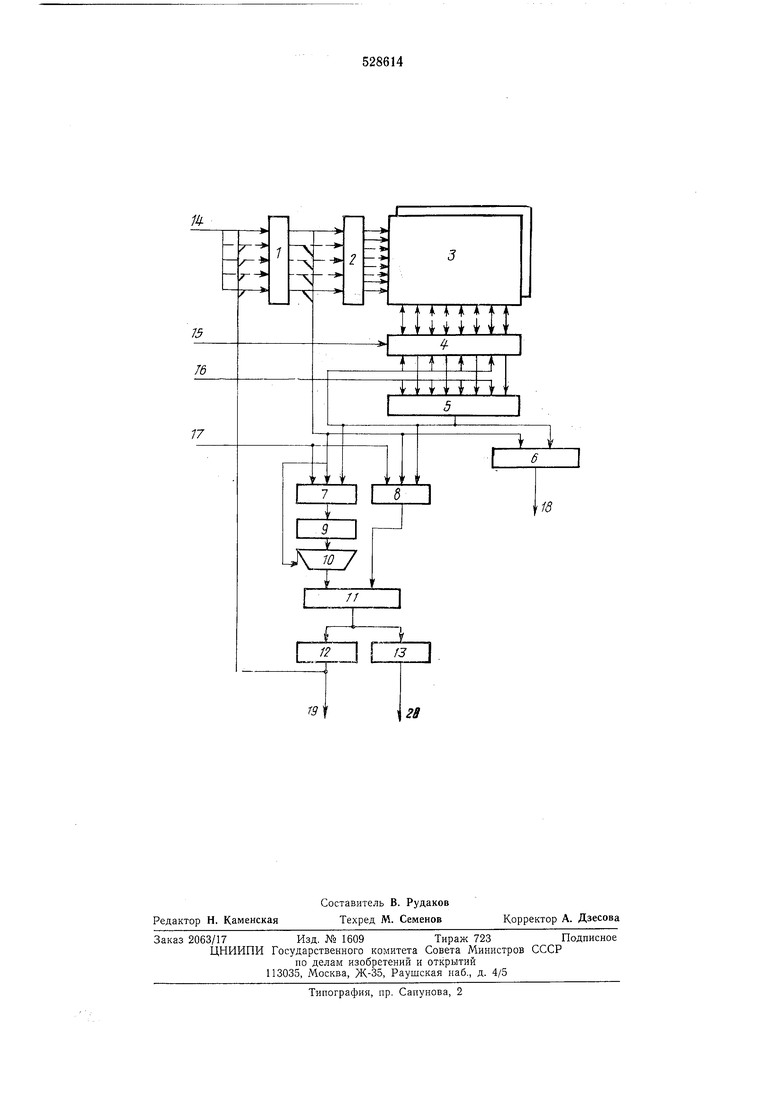

На чертеже приведена структурная схема предлагаемого заноминающего устройства.

Устройство содержит регистр 1 адреса, дешифратор 2 адреса, блок 3 запомннаюш,их матриц, усилители 4 считывания-записи, регистр 5 слова; блок 6 контроля информации, блок 7 вычитания инверсных кодов адреса, блок 8 вычитания прямых кодов адреса, элементы НЕ 9, элементы И 10, сумматор 11, дополнительный регистр 12 адреса, блок 13 выработки сигнала ошибки, определяюндий неисправность адресного тракта устройства.

Оперативное запоминаюш,ее устройство подключается к другим устройствам с номон ью следующих управляюш,их шин: входных шин адреса 14, шины 15 сигнала, управляюш,его переключением входов усилителей считывания записи 4 в зависимости от режима устройства работы, входных шин слова 16, шины 17 сигнала управления в контрольном режиме устройства, шины 18 сигнала ошибки, определяющей неисправность устройства, шины 19 выхода регистра 12, фиксирующего адрес неисправной ячейки памяти, выходной шины 20 сигнала ошибки, определяющей неисправность адресного тракта устройства.

Регистр 1 адреса подключен к дешифратору 2 адреса, выходы которого соединены с адресными входами блока 3 запоминающих матриц, регистр 5 слова подключен к усилителям 4 считывания-записи, блок 6 контроля информации соединен с выходами регистра 5 слова и регистра 1 адреса.

Входы блоков 7 и 8 соединены попарно и подключены соответственно к управляющей шине 17 и выходам регистра 1 адреса и регистра 5 слова, входы элементов НЕ 9 соединены с выходом блока вычитания инверсных кодов адреса, входы элементов И 10 подключены соответственно к выходам элементов НЕ 9 и выходам регистра адреса, входы сумматора 11 соединены соответственно с выходами элементов И 10 и блока вычитания прямых кодов адреса, а выход сумматора 11 - со входом блока выработки сигнала ошибки, вход дополнительного регистра адреса подключен к выходу сумматора 11, а его выход соединен с входом регистра 1 адреса.

Оперативное запоминающее устройство работает в трех режимах: рабочем, контрольном и восстановления информации. В рабочем режиме при записи информации в устройство адрес ячейки с контрольным кодом, находящийся на входных шинах адреса 14, и записываемое слово с контрольным кодом, находящееся ча входных щинах слова 16, фиксируются, соответственно, на регистре 1 адреса и регистре 5 слова.

Далее адрес и слово поступают в блок контроля информации, где производится проверка содержимого регистров адреса и слова на соответствие контрольным разрядам. Через дешифратор адреса выбирается необходимая ячейка оперативной запоминающей секции блока запоминающих матриц и производится

запись содержимого регистра слова в выбранную ячейку памяти. При чтении слова информация с контрольным кодом из адресуемой ячейки оперативной запоминающей секции блока 3 выбирается на регистр 5 слова и затем поступает в блок 6. В случае искажения содержимого регистра 5 блок 6 выдает сигнал ошибки на шину 18, указывающий на неисправность устройства. Для определения места ошибки (в информационном или адресном

тракте) по сигналу на шине 18 происходит переключение устройства в контрольный режим. В контрольном режиме по адресу, сохранившемуся на регистре 1 от предыдущего обращения к устройству в рабочем режиме, через

дешифратор адреса выбирается ячейка постоянной запоминающей части блока 3, из которой на регистр 5 считывается нрямой и инверсный код адреса ячейки памяти. При исправности адресного тракта значения прямого и

инверсного кода адреса на регистре 5 должны соответствовать значениям прямого и инверсного кода адреса на регистре 1. При неисправности адресного тракта обращение производится параллельно в адресуемую ячейку намяти и в ячейку памяти, выбираемую ощибочно из-за отказа дешифратора. Поэтому при чтении информации постоянной запоминающей части блока 3 на регистре 5 происходит наложение содержимого действительно адресуемой ячейки памяти и ложно адресуемой. Определение адреса ложно адресуемой ячейки памяти производится по нижеследующему алгоритму. По управляющему сигналу на шине 17 в блоке 7 производится вычитание из инверсного кода адреса, зафиксированного на регистре 5, инверсного кода того же адреса, хранящегося на регистре 1.

В блоке 8 производится вычитание из прямого кода адреса, зафиксированного на регистре 5, прямого кода адреса, хранящегося на регистре 1. Затем разряды разности инверсных кодов адреса с выхода блока 7 инвертируются элементами НЕ 9, а те разряды, у которых в вычитаемом соответствующие разряды равны нулю, пропускаются элементами И 10 на вход сумматора 11. Инверсная разность инверсных кодов складывается по модулю два в сумматоре 11 с разностью прямых кодов адреса, полученных с выхода блока 8. Результат сложеНИН (адрес ложно адресуемой ячейки намяти) с выхода сумматора И поступает на дополнительный регистр 12 и на вход блока 13 выработки сигнала ошибки. Блок 13 выдает сигнал ошибки на шину 20, определяя неисправность

адресного тракта устройства.

Далее в режиме восстановления информации определяется истинное значение информации но адресу первого обращения.

Для этого адрес ложно адресуемой ячейки намяти с регистра 12 нерепнсывается на регистр 1, содержимое регистра 5 сбрасывается, нроизводится обращение к устройству и в ложно адресуемую ячейку намяти записываются нули. После этого нроизводится повторное считывание информации из действительно адресуемой ячейки памяти. Считанная информация после проверки ее блоком 6 контроля информации является верной.

Формула изобретения

Оперативное запоминающее устройство, содержащее регистр адреса, подключенный к дешифратору адреса, выходы которого соединены с адресными входами блока запоминающих матриц, регистр слова, подключенный к усилителям считывания-записи, блок контроля информации, соединенный с выходами регистра слова и регистра адреса, блок выработки сигнала ощибки и управляющие шины, отличающееся тем, что, с целью повышения надежности устройства н эффективности контроля адресного тракта, оно содержнт блоки вычитания инверсных и прямых кодов адреса, входы которых соединены попарно и подключены соответственно к одной из управляющих шин н выходам регистра адреса и регистра слова, элементы НЕ, входы которых соединены с выходом блока вычитания инверсных кодов адреса, элементы И, входы которых подключены соответственно к выходам элементов НЕ п выходам регистра адреса, сумматор, Б.ходы которого соединены соответственно с вы.ходамн элементов И и блока вычитания прямых кодов адреса, а выход - со входом блока выработки сигнала ошибки, дополнительный регистр адреса, вход которого подключен к выходу сумматора, а выход соединен со входом регистра адреса.

Источники информации, принятые во внимание при экспертизе:

1.Патент Великобритании № 1186416, кл. G 04С, 1970 г.

2.Патент США № 3697949, кл. G 06F 11/12, 1972 г.

3.Авт. св. № 333559, кл. G НС 29/00, 1971 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1976 |

|

SU636678A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Оперативное запоминающее устройство | 1973 |

|

SU528611A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

Авторы

Даты

1976-09-15—Публикация

1974-07-26—Подача