1

Изобретение относится к вычислительной технике.

Известно онеративное запоминающее устройство, содержащее адресные и информационные шины и блоки памяти 1. Старшие разряды кода адреса указывают номер блока устройства, младшие - адрес ячейки внутри блока. Основным недостатком такого устройства является недостаточная надежность, даже в тех случаях, когда информация кодируется корректирующим кодом, некоторые одиночные неисправности блоков памяти могут привести к некорректируемым ошибкам.

Известно также устройство, содержащее регистр числа, регистр адреса и блока памяти, каждый из которых содержит один разряд информации, закодированной кодом, корректирующим одиночные ошибки 2. В этом устройстве корректируются любые ошибки, вызванные одиночнымн неисправностями блоков памяти. Основным недостатком этого устройства является то, что один программно доступHbiii модуль устройства содержит столько блоков памяти, сколько разрядов имеет кодовое слово, что приводит к увеличению стоимости, особенно небольших вычислительных систем.

Наиболее близким но техпической сущности к данному изобретению является оперативное запоминающее устройство, содержащее входной регистр, подключенный к блокам памяти.

выходной регистр, адресный блок 3. В этом устройстве слова разбиваются на равные по величине группы, каждая из которых хранится в одном блоке памяти. Условие равенства

групп накладывает довольно жесткие ограничения на длину слова и допустимые методы кодирования. Это ириводит к снижению надежности устройства и его эффективной емкости.

Целью изобретения является повышение надежности устройства и его эффективной емкости.

Это достигается тем, что устройство содержит дешифраторы и элементы И-ИЛИ по

числу блоков памяти, входы дешифраторов подключены к выходам адресного блока, выходы дешифраторов соединены с одними входами эле.ментов И-ИЛИ, другие входы которых подключены к выходам соответствующих

блоков памяти, а выходы элементов И-ИЛИ соединены со входами выходного регистра.

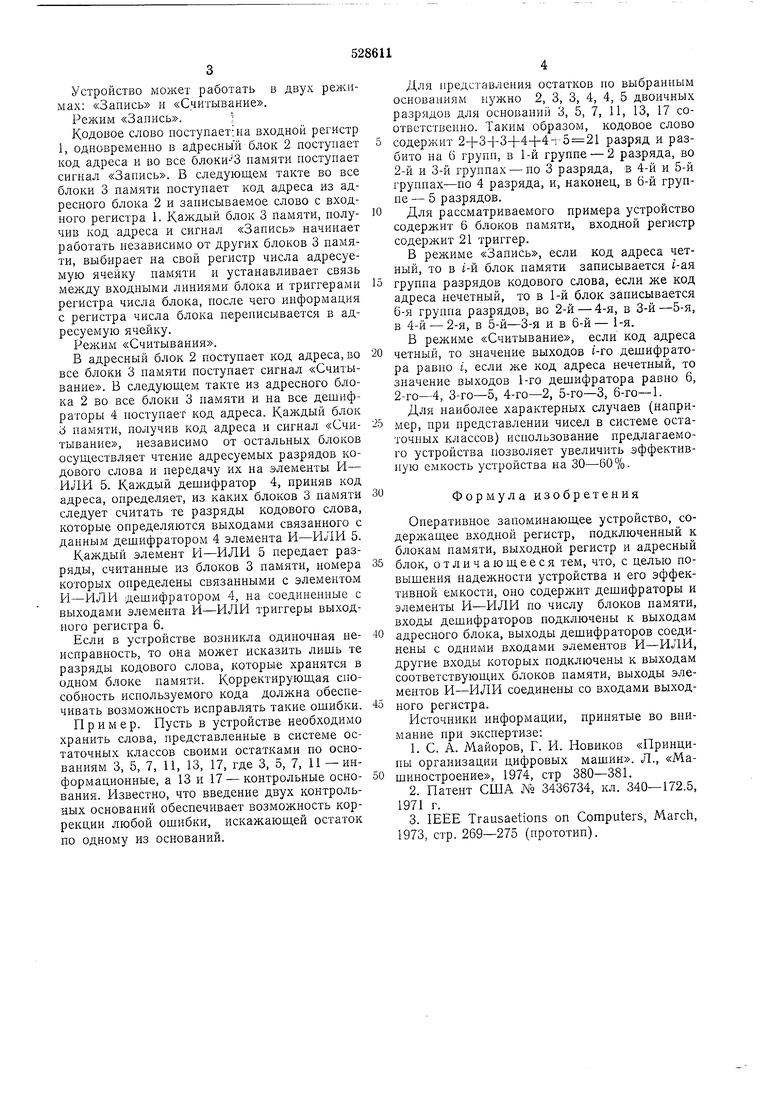

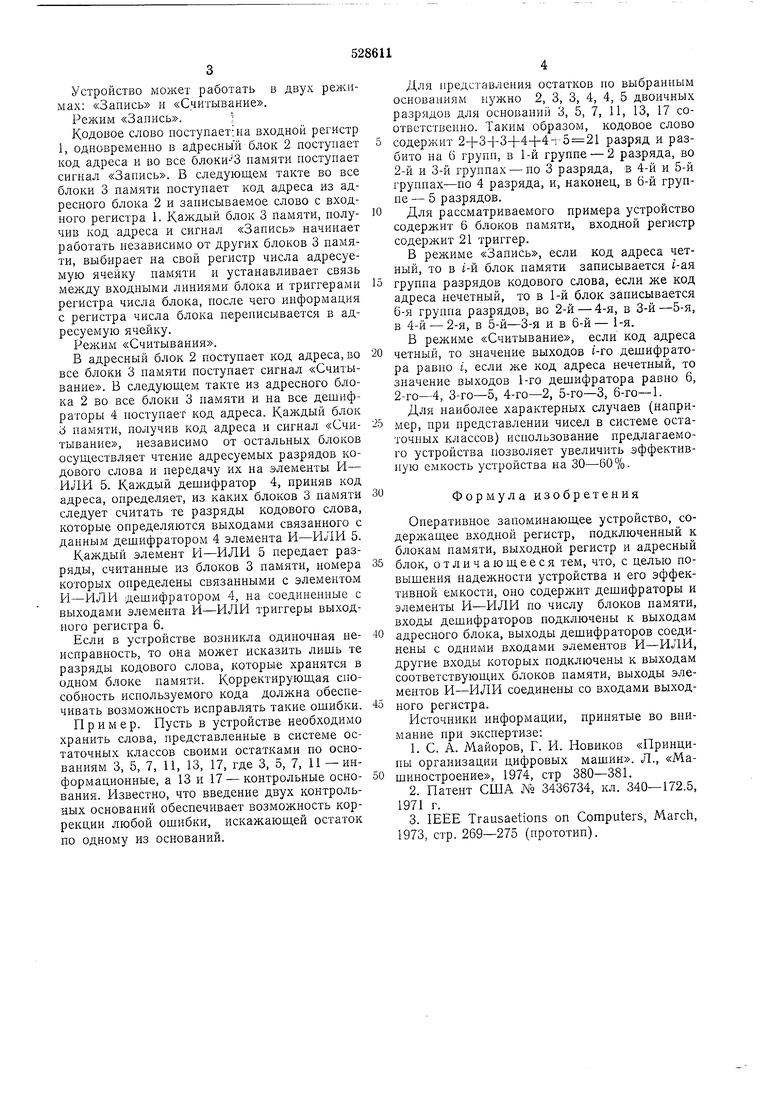

Иа чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит входной регистр 1, адресный блок 2, блоки 3 иамяти, каждый из которых содержит накопитель, адресные и разрядные цепи и т. д. (на чертеже не ноказаны), дешифраторы 4 и элементы И-ИЛИ 5 по

числу блоков памяти, п выходной регистр 6. Устройство может работать в двух режимах: «Запись и «Считывание. Режим «Запись.; Кодовое слово поступает;на входной регистр 1, одновремеино в аДресиый блок 2 поступает код адреса и во все блоки-З памяти поступает сигнал «Запись. В следующем такте во все блоки 3 памяти поступает код адреса из адресиого блока 2 и записываемое слово с входпого регистра 1. Каждый блок 3 памяти, получив код адреса и сигпал «Запись начинает работать иезависимо от других блоков 3 памяти, выбирает па свой регистр числа адресуемую ячейку памяти и устанавливает связь между входными линиями блока и триггерами регистра числа блока, после чего информация с регистра числа блока переписывается в адресуемую ячейку. Режим «Считывания. В адресный блок 2 поступает код адреса, во все блоки 3 памяти поступает сигнал «Считывание. В следующем такте из адресного блока 2 во все блоки 3 памяти и на все дешифраторы 4 поступает код адреса. Каждый блок 3 памяти, получив код адреса и сигнал «Считывание, независимо от остальных блоков осуществляет чтение адресуемых разрядов кодового слова и передачу их на элементы И- ИЛИ 5. Каждый дешифратор 4, приняв код адреса, определяет, из каких блоков 3 памяти следует считать те разряды кодового слова, которые определяются выходами связанного с данным дешифратором 4 элемента И-ИЛИ 5. Каждый элемент И-ИЛИ 5 передает разряды, считанные из блоков 3 памяти, номера которых определены связанными с элементом И-ИЛИ дешифратором 4, на соединенные с выходами элемента И-ИЛИ триггеры выходного регистра 6. Если в устройстве возникла одиночная неисправность, то она может исказить лишь те разряды кодового слова, которые хранятся в одном блоке памяти. Корректирующая способность используемого кода должна обеспечивать возможность исправлять такие ошибки. Пример. Пусть в устройстве необходимо хранить слова, представленные в системе остаточных классов своими остатками по основаниям 3, 5, 7, 11, 13, 17, где 3, 5, 7, 11 -информационные, а 13 и 17 - контрольные основания. Известно, что введение двух контрольных оснований обеспечивает возможность коррекции любой ошибки, искажающей остаток по одному из оснований. Для представления остатков по выбранным основаниям нужно 2, 3, 3, 4, 4, 5 двоичных разрядов для оснований 3, 5, 7, 11, 13, 17 соответственно. Таким образом, кодовое слово содержит 2+3+3+4--|-4-г5-21 разряд и разбито на 6 групп, в 1-й группе - 2 разряда, во 2-й и 3-й группах - по 3 разряда, в 4-й и 5-й группах-по 4 разряда, и, наконец, в 6-й группе - 5 разрядов. Для рассматриваемого примера устройство содержит 6 блоков памяти, входной регистр содержит 21 триггер. В режиме «Запись, если код адреса четный, то в i-й блок памяти записывается t-ая группа разрядов кодового слова, если же код адреса нечетный, то в 1-й блок записывается 6-я группа разрядов, во 2-й-4-я, в 3-й-5-я, в 4-й - 2-я, в 5-й-3-я и в 6-й- 1-я. В режиме «Считывание, если код адреса четный, то значение выходов t-ro дешифратора равио г, если же код адреса нечетный, то значение выходов 1-го дешифратора равно 6, 2-го-4, 3-го-5, 4-го-2, 5-го-3, 6-го-1. Для наиболее характерных случаев (например, при представлении чисел в системе остаточных классов) использование предлагаемого устройства позволяет увеличить эффективную емкость устройства на 30-60%. Формула изобретения Оперативное запоминающее устройство, содержащее входной регистр, подключенный к блокам памяти, выходной регистр и адресный блок, отличающееся тем, что, с целью повышения надежности устройства и его эффективной емкости, оно содержит дешифраторы и элементы И-ИЛИ по числу блоков памяти, входы дешифраторов подключены к выходам адресного блока, выходы дешифраторов соединены с одними входами элементов И-ИЛИ, ругие входы которых подключены к выходам соответствующих блоков памяти, выходы элементов И-ИЛИ соединены со входами выходного регистра. Источники информации, принятые во вниание при экспертизе: 1.С. А. Майоров, Г. И. Новиков «Принциы организации цифровых машин. Л., «Маиностроение, 1974, стр 380-381. 2.Патент США № 3436734, кл. 340-172.5, 1971 г. 3.ШЕЕ Trausaetions on Computers, March, 973, стр. 269-275 (прототип).

4

Г

s

u

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с контролем цепей обнаружения ошибок | 1985 |

|

SU1367046A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

Авторы

Даты

1976-09-15—Публикация

1973-06-01—Подача