1

Данное изобретение относится к цифровой вычислительной технике и является усовершенствованием известного устройства {.

Основное нзобретенне нредставляет собой оперативное запоминающее устройство (ОЗУ), позволяющее разграничить ошибки информационного и адресного тракта, определить адрес неисправной ячейки и исключить потерю информации.

Недостатком указанного устройства является то, что оно не может определить неисправный элемент в адресном тракте, его адрес (местонахождение). За счет этого снижается оперативность поиска неисправности и, в конечном счете, надежность устройства (время восстановления).

- Целью дополнительного изобретения является повышение надежности устройства.

Это достигается тем, что оперативное запоминающее устройство содержит блок сравнения адресов и блок определения ступени дешифратора адреса, входы блока сравнения адресов соединены соответственно с выходами регистра адреса, дополнительного регистра и блока выработки сигнала ошибки, а выход - с дополнительным входом

регистра адреса, вход блока от роделепня ступени дешифратора адреса соеди1 ен с выходом блока срав1 еиия адресов.

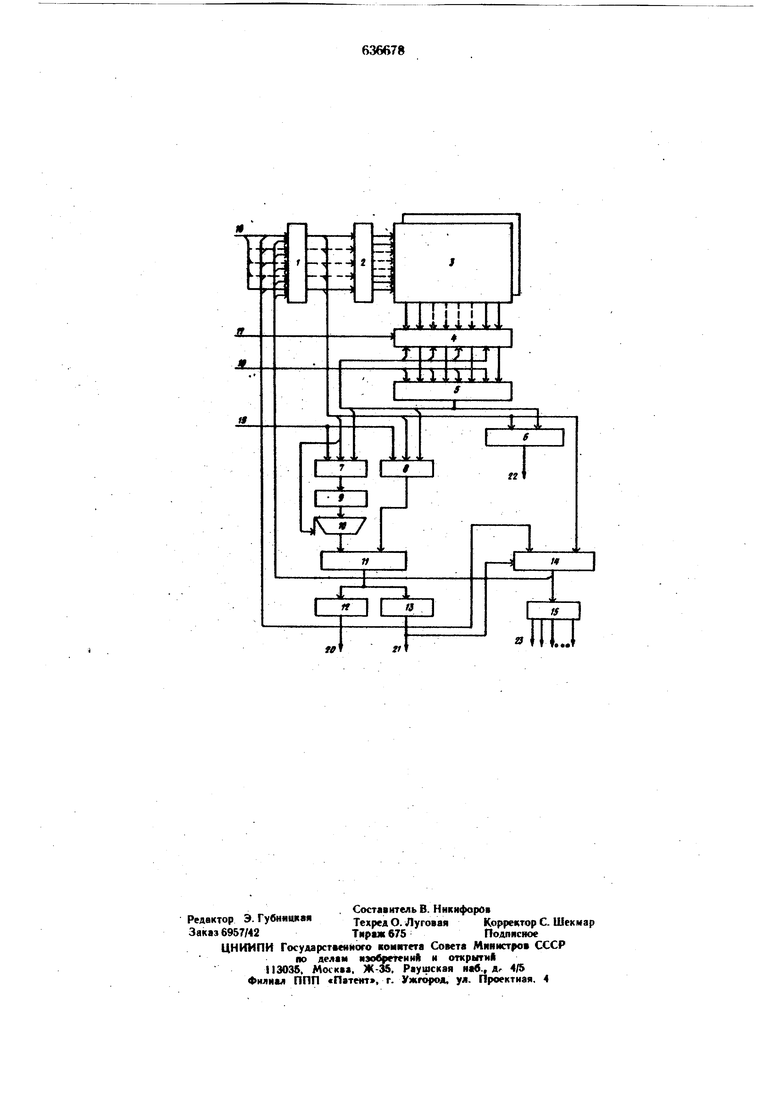

На чертеже приведе 1а структурная схема оперативиого запоминающего устромства.

Устройство содержит регистр адреса 1, дешифратор адреса 2, блок запоминающих матриц 3, усилител считывания -- записи 4, регистр слова 5, блок контроля ин(|1ормации 6, блок вычитания инверсных кодов адреса 7, блок вычитания прямых кодов адреса 8, элементы НЕ 9, элементы И 10, сумматор 11, дополнительный регистр адреса 12, блок выработки сигнала ошибки 3, блок сравнения адресов 14, блок определения ступени дешифратора адреса 15,. шины 16-23.

Регистр адреса i фиксирует адрес и контрольный код адреса. Блок запоминающих матриц 3 состоит из оперативной запоминаю.щей части (ОЗЧ) и постоянной запоминающей части (ПЗЧ) и работает в зависимости

от управляющего сигнала либо в рабочем режиме в качестве оперативного запоминающего блока с возможностью чтения записи информации, либо в контрольном режиме в качестве постоянного запоминающего блока

с возможностью чтения заранее заданных значений прямых и ннверсных кодов адресов ячеек. Усилители считывания - записи 4 имеют возможность переключения входов управляющим сигналом, определяющим режим работы запоминающего устройства. Регистр слова 5 служит для фиксации в рабочем режиме и режиме восстановления слов информации, считанных из блока запоминающих матриц 3, либо предназначенных для записи в блок 3, а в контрольном режиме - значений прямого и инверсного кодов адреса ячейки, в которую произошло обращение при считывании из блока 3.

Блок контроля информации 6 функционирует в рабочем режиме и служит для проверки содержимого регистра слова 5 и регистра адреса I перед записью информации в блок 3 и для проверки информации, прочитанной из блока 3 на регистр 5 и выработки сигнала неисправности ОЗУ в случае искажения прочитанной информации.

Блок вычитания инверсных кодов адреса 7 предназначен для вычитания в контрольном режиме из инверсного кода адреса (а), считанного из постоянной запоминающей части блока 3 на регистр 5, инверсного кода адреса (в), хранящегося на регистре 1. причем, прямое и инверсное значения разности опре/еляются, соответственно формулами Ci aibi и Ci

Блок вычитания прямых кодов адреса 8 служит для вычитания по модулю два в контрольном режиме из прямого адреса, считанного из ПЗЧ блока 3 на регистр 5, прямого кода адреса, хранящегося на регистре I. Элементы И 10 предназначены для клапанирования на вход сумматора 11 только тех инвертированных разрядов разности с выхода блока 7, у которых в вычитае.мом соответствующие разряды равны нулю.

Сумматор 11 позволяет определить в контрольном режиме суммы гю модулю два результата .вычитания прямых кодов с выхода блока вычитания 8 и инвертированного результата вычитания инверсных кодов адреса с выхода блока 7.

Дополнительный регистр адреса 12 фиксирует в контрольном режиме результат суммирования с выхода сумматора И, т.е. адреса неисправной ячейки ОЗУ. Блок выработки сигнала ошибки 13 определяет неисправность адресного тракта ОЗУ.

Оперативное запоминающее устройство может быть подключено к другим устройствам вычислительной системы с помощью внешних щин.

Оперативное запоминающее устройство работает в следующих режимах: рабочем, контрольном, восстановления информации и определения адреса неисправного элемента.

В рабочем режиме при записи информацни в ОЗУ адрес ячейки с контрольным кодом и слово с контрольным кодом, фиксируются соответственно на регистре I ;upeca

И регистре 5 слова, /la.iee адрес и слово поступают в блок контроля 6, где производится проверка содержимого регистров I и 5 на соответствие контрольным разрядам. Через дешифратор 2 a/ipeca выбирается необходимая ячейка оперативной запоминающей части блока 3 запоминающих матриц и производится запись содержимого регистра 5 в выбранную ячейку ОЗУ. При чтении слово с контрольным кодом из адресуемой ячейки ОЗЧ блока 3 выбирается на регистр 5 и затем поступает в блок 6 контроля, где проверяется правильность прочитанной информации. В случае искажения содержимого регистра 5 блок 6 выдает сигнал ощиб| ;и на шину 22, определяя неисправность ОЗУ. Для определения, где произо:цла ощибка (в информационном или адресном тракте) по сигналу на шине 19 происходит переключение ОЗУ в контрольный режим.

В контрольном режиме по адресу, сохраняющемуся на регистре 1 от предыдущего обращения к ОЗУ в рабочем режиме, через дешифратор адреса 2 выбирается ячейка ПЗЧ блока 3, из которой на регистр 5 считывается прямой и инверсный коды адреса ячейки. При исправности адресного тракта значения прямого и инверсного кодов адреса на регистре 5 должны соответствовать значениям прямого и инверсного кодов адреса на регистре I. При неисправности адресного тракта обращение производится параллельно в адресуемую ячейку и в ячейку, выбираемую ошибочно из-за отказа дешифратора. .Поэтому при чтении ииформации из ПЗЧ на регистре 5 происходит наложение содержимого действительно и ложно адресуемых ячеек. Определение адреса ложно адресуемой ячейки производится по нижеследующему алгоритму. По управляющему сигналу на щине 19 в блоке вычитания 7 производится вычитание из инверсного кода адреса, зафиксированного на регистре 5, инверсного кода того же адреса, хранящегося на регистре 1. В блоке вычитания 7 производится вычитание из прямого кода адреса, зафиксированного на регистре 5, прямого кода адреса, хранящегося на регистре 1. Затем разряды разности инверсных кодов адреса с выхода блока 7 инвертируются элементами 9 НЕ, а те разряды, у которых в вычитаемом соответствующие разряды равны нулю, пропускаются элементами 19 И, на вход сумматора 1К Инверсная разность инверсных кодов складывается по модулю два в сумматоре 11 с разностью прямых кодов адреса, полученных с выхода блока 8. Результат сложения (адрес ложно адресуемой ячейки) с выхода сумматора 11 поступает на допсущительный регистр 12 и на вход блока 13 выработки сигнала ощибки. Блок 13 выдает сигнал ошибки, определяя неисправность адресного тракта ОЗУ, при этом выдается адрес ложно адресуемой ячейки.

В режиме восстановления информации определяется истинное значение информации, хранящейся по адресу первого обра-щения. Для этого адрес ложно адресуемой ячейки с регистра 12 переписывается на регистр I, содержимое регистра 5 сбрасывается, производится обращение к ОЗУ и в ложно адресуемую ячейку записываются нули. После чего производится повторное считывание информации из действительно адресуемой ячейки. Считанная информация после проверки ее блоком контроля 6 является верной.

В режим определения адреса неисправного элемента устройство переходит по сигналу с выхода блока 13 после восстановления информации. По этому сигналу в 4 сравнения производится сравнение адреса исправной ячейки, хранящейся в регистре I, и адреса неисправной ячейки, зафикснрованиой на регистре 12. Блок 4 определяет крайние левые несовпадающие разряды, выдавая в виде единицы сигнал на выходе, соответствующем позиции этого разряда. Этот сигнал поступает в блок 15 определения ступени дешифратора и на счетный вход одного из триггеров регистра адреса. Таким образом, если крзйниин левыми несовпадающими разрядами являются К-тые разряды, то инвертируется К-Ь I разряд. Затем производится обращение по полученному адресу к ПЗЧ и после получения неисправного адреса снова происходит сравнение адресов, хранящихся в регистре адреса I и регистре 12. Если в результате сравнения получено, что крайними левыми несовпадающими разрядами снова являются К-тые разряды, то на выходе блока 15 появляется сигнал, показывающий, что неисправный элемент находится в (К-1)-ой ступени дешифратора. Если

же в результате сравнения не соли; Ч-1)-ые |)азряды, то п|)()изн(1дигч) ровапне (К-1-2) разря;1а jicupiUinoi ;i ;, ц.ч-.i и снова ирои:ч(к)ли1ся обргиценио н ПЛЧ. Уклзанньш алгоритм по/ггоряетси Д. с , пока ПС Г(ои:1ойде1 два несовмадо пч очпоинеиных рлз)яIOB. Кч.креглый ,,; и;. гфавного з. опредо.негси iteiiUiiKi:Hbiiif ад), хр пьицимся п pei i/л который определяет цеиь licuciipinuioro я leмента дешифратора, и сигналом с B: Xi;i.; блока 15, укил;; ПйК;И1и KaKdH эделич:; п этой uetiH пеиспроги.м.

Итак, ирсддагаелое oncpariiBir.;- .;;,::;. минаюшес устропсгво лопи.анлтсл1- : ; i iiv; иожкоетям про-отяпа позподяет Им;;м пи чески определить Mecivj liOHcnfTiBihir

S

креткоетью до s.icMeii : де1Нпф И 1рл, улучшает реыоитоеiucoOaocih уиройс} отсюда и его гадел-лсость.

Формул а usofin,; TiiiUi

Э

ОператиЕкое запомниакиное }чтри( по авт.св. № 52§ГИ1, r)rAii;(:oui, it с целью позьпаелич надожиостн оно содержит блок сравнения гзрссов и определеи.чя сту.ге.чн ле1ии(})ато1)а а.:входы блока cpaBHCfiJin адресов согди соответстзенно с выходами регистр; ( дополнительного регистра адреса и О,: выработк): снтнала ошибки, л ны.сод дополннтельньвм в.чодом ретистрЛ адцч вход блока опреде.епия ступени деппгФр;

3

ра адреса соедипеи с выходим олоса срав иеиня адресов.

HcTOMiiUKii HitilOpMaiuiif, прикягьге нс) aiuiмание при экспертизе:

1. А «торс кое свидетельстно СССР 5 Л 52861-1, кл. О II С 29/00, 26.07.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1974 |

|

SU528614A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU930388A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU985830A1 |

| Оперативное запоминающее устройство | 1973 |

|

SU528611A1 |

| Устройство для сопряжения двух электронных вычислительных машин (ЭВМ) | 1983 |

|

SU1265781A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

Авторы

Даты

1978-12-05—Публикация

1976-05-17—Подача