второй группы, одни из входов компаратора соединены с выходами элементов ИЛИ-НЕ.групп и другими входами регистра числа и являются информационными входами устройства, другие выхо- ды регистра числа подключены к другим входам компаратора и являются/информационными выходами устройства, другим управляющим входом и индикаторными выходами которого являются соответственно второй вход второго элемента И, прямой выход триггера, и третий прямой выход счетчика режимов, : с1 контрольными И адресными выходами устройства являют ся соответственно выходы регистра кодов ошибки и прямые выходы второго счетчлка импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

ДИНАМИЧЕСКОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО С САЖЖОНТРОЛЕМ, содержащее, регистр адреса, селекторы, счетчики импульсов, накопитель, дешифратор, генератор TaKTpBisijf сигналов, регистр числа и &лок контроля, причем выходы первого и второго селекторов подключены Соответственно к адресньом входам накопителя и к входам дешифратора, выходы которого соединены с входами выборки накопителя, первые входы селекторов подключены к выходам регистра адреса, вторые входы.первого и второго селекторов соединены соответственно с прямыми выходами первого и второго счеТчиков импульсов, а третьи входы подключены к первому выходу генератора тактовых сигналов, второй и третий выходы которого соединены соответственно с входом стробирован-ия дешифратора и с входом первого счетчика импульсов, информационные входы и выходы накопителя подключены соответственно к одним из выходов и входов регистра числа, управляющий выход которого подключен к входу блока контроля, входы генератора тактовых сигналов являются одними из управляющих входов устройства, отличающееся тем, что, с целью повышения его надежности, в него введены счетчик режимов, котипаратор, триггер, регистр кодов ошибки, группы элементов И, группы элементов ИЛИ-НЕ, элементы Я и элемент ИЛИ, выход которого подключен к входу режимов накопителя, а первый и второй входы соединены соответственно с четвертым выходом генератора тактовых сигналов и с первым прямым выходе счетчика режимов, первый инверсный выход которого подключен к управляющему входу компаратора, выходы которого соединены соответственно с входами регистра кодов ошибки и с установочным входом триггера, причем первые входы первог го и второго элементов И подключены к выходу переноса первого счетчика импульсов, а выходы - соответственно к входу второго счетчика импульсов и к входу сброса триггера, инверс- . ный выход которого соединен с вторым входом первого элемента И, первыевходы элементов И первой и второй групп подключены соответственно кпря1 «лм и к инверснЕШ выходам первого счетчика импульсор, а первые входы элементов и третьей и четвертой ю групп - соответственно к npavsuM и к инверсным выходам второго счетчика импульсов, вторые входы элементов ю ю И первой и третьей групп соединены с вторым инверсным выходом счетчика режимов, второй прямой выход которо4iii го подключен к вторым входам элемен-тов И ВТОРОЙ и четвертой групп, третьи входы элементов И групп соединены с третьим инверсным входом счетчика режимов и первым входом третьего элемента И, второй вход и выход которого подключены соответс гвенно к выходу переноса второго счетчика импульсов и к входу счетчика режимов. выходы элементов и первой и второй групп соединены с входами элементов ИЛИ-HF первой группы, выходы эле 4ентов И третьей и четвертой групп, подключены к входам элементов ИЛИ-НЕ

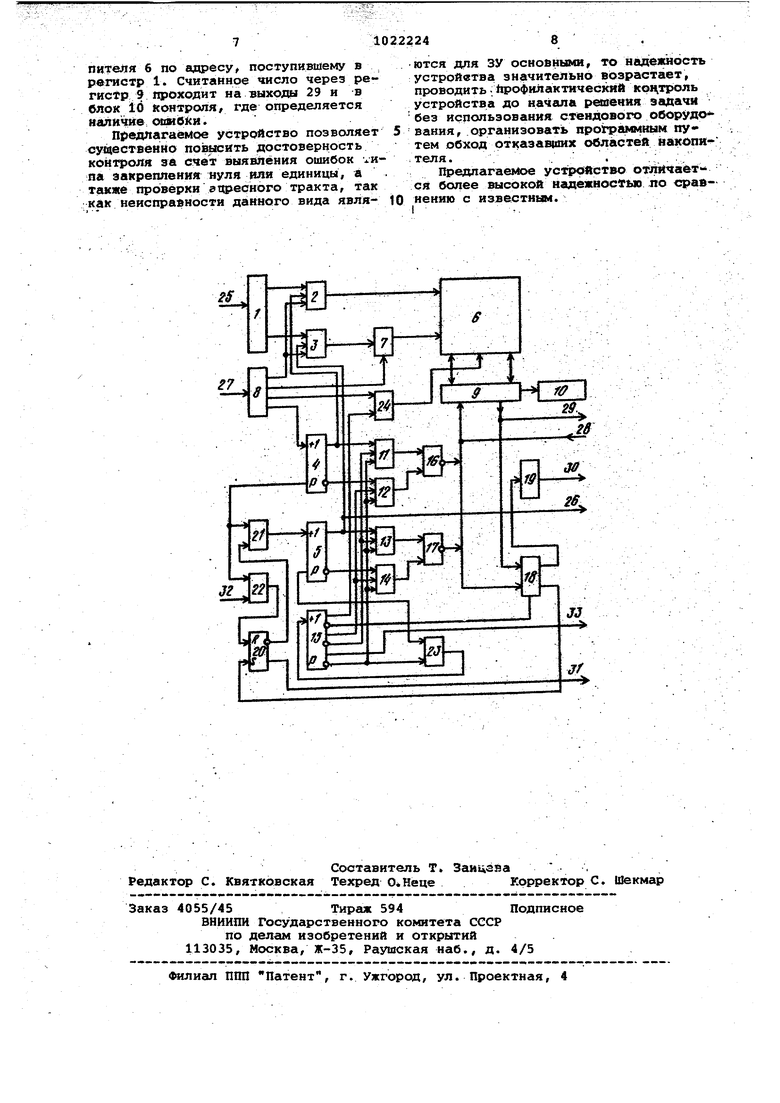

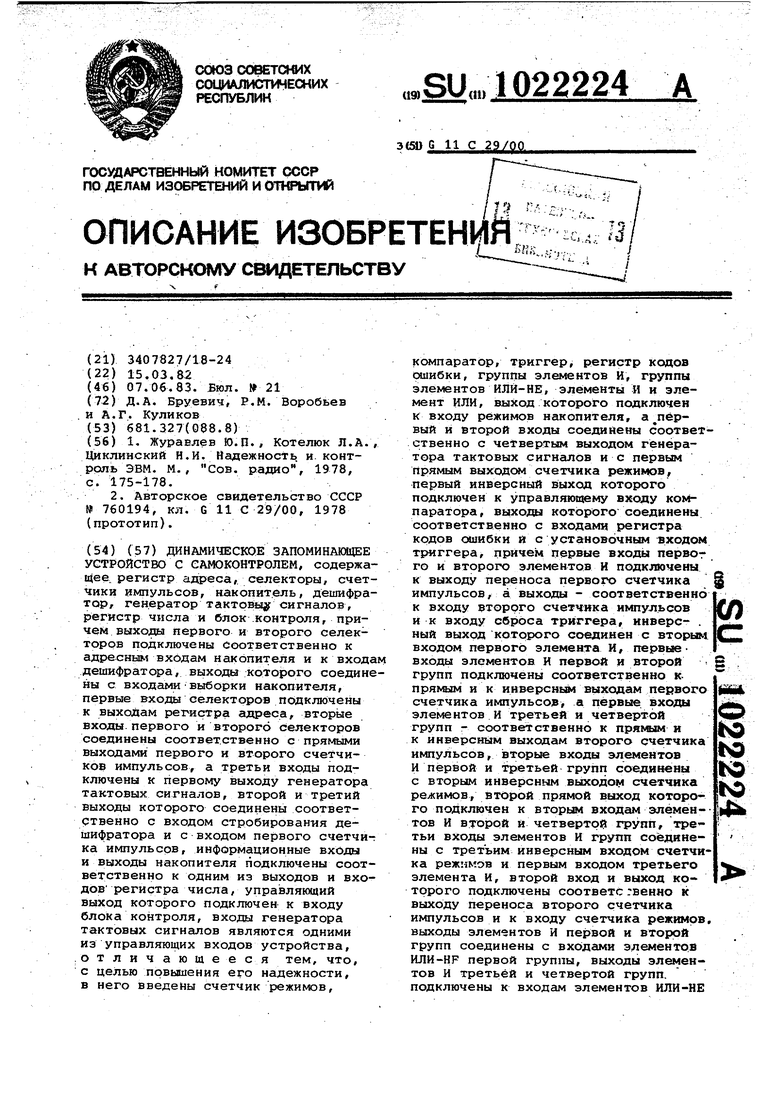

; i Изобре ение относится к вычислительной, технике и может быть исполь зовано для построения высоконадежных динамических запоминакяцих .устройств, снабженных встроенными сред ствами обнаружения отказов. Известно динамическое запоминающее устройство с самоконтролем, содержащее накопитель, первый и второ регистры,-узел неравнозначности и узел переключения режимов С 3 Недостаток указанного устройства - низкое быстродействие. Наиболее близким к предлагаемому является динамическое запоминающее УСТРОЙСТВО с самоконтролем, содержащее нiaкoпитeлй на полупроводниковых элементах памяти, информационны входы и выходы которых через регист числа сЬединены с информационными ишнами и входами блока контроля, эх ды выборки накопителей соединены с выходами дешифратора, входы обращения - регенерации через первый селектор - с выходами первого счетчик и одними выходами регистра адреса, входы которого соединены с адресными шинами, тактовый генератор, первые выходы которого соединены со стробирующим входом дешифратора и входом режима накопителей, вторые с управляющим входом первого селектора и счетным вхоЖом первого счетчика, вход тактового генератора сое динен с входной управляющей шиной, первые входы второго селектс1ра соед нёны с другими выходами регисзфа ад реса, вторые входы - с выходами сче чика, управляющий вход второго селек тора соединен с управлякнцим входом первого селектора, одни выходы - с адресными ьходс1ми накопителей, другие выходы - с входами дешифратора, счетный вход второго счетчика соединен с выходом переноса первого C4et4HKa 2 . Недостатками известного устройст ва являются зависимость обнаружения неисправности от характера записанной информации и невозможность выяв ления отказов адресного тракта, а 2 также то, что это устройство не позволяет обнаружить неисправности до начала решения задачи, что;снижает его надежность. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в динамическое запоминающее устройство с самоконтролем, содержащее регистр адреса, селекторы, счетчики импульсов, накопитель, дешифратор, генератор тактовых сигналов, регистр числа и блок контроля, причем выходы первого и второго селекторов подключены соответственно к адресным входам накопителя и к входам дешифг ритора, выходы которого соединены с входами выборки накопителя, первые входы селекторов подключены к выходам регистра адреса, вторые входы первого и второго селекторов соединены соответственно, с прямыми выходами первого и второго счетчиков импульсов, а третьи входы подключены к первому выходу генератора тактовых сигналов, второй и третий выходы которого соеинены соответственно с входом стробирования дешифратора и с входом первого счетчика импульсов, информационные входы и выходы накопителя подключены соответственно к одним из выходов и входов регистра числа, управляющий выход которого подключен к входу блока контроля, входы генератора тактовых сигналов являются одними из управляющих входов устройства, введены счетчик режимов, компаратор, триггер, регистр кодов ошибки, группы элементов и, группы элементов ИЛИ-НЕ, элементы И и элемент ИЛИ, выход которого подключен к входу режимов накопителя, а первый и второй входы соединены соответственно с четвертым выходом генератора тактовых сигналов и первым прямым выходом счетчика режимов, первый инверсный выход которохо подключен к управляющему входу | компаратора, выходы которого соединены соответственно с входами регистра кодов ошибки и с установочным входом триггера, причем первые входы первого и второго элементов И подключены к выходу переноса первого счетчика импульсов, а выходы - соответственно к входу второго счетчика импульсов и к входу сброса триггера, инверсный выход которого соединен с вторым входом первого элемента И, первые входы элементов И первой и второй групп подключены соответственно к прямым и к инверсньам выходам первого счетчика импульсов,а первые входы элементов И третьей и четвертой групп - соответственно к. пряьФлм и к инверсным выходам второго, счетчика импульсов, вторые вход : лементов И первой и третьей групп соединены с вторым инверсным выходом счетчика режимов, второй прямой выход которого подключен к вторым входам элементов И второй и четвертой групп, третьи входы -элементов И групп соединены с третьим инверсным входом счетчика режимов и первым вхо дом третьего элемента И, второй вход и выход которого подключены соответственно к выходу переноса второго счетчика импульсов и к входу счетчика режимов, вь1ходы элементов И первой, и второй групп соединены с входами элементов ИЛИ-НЁ первой группы выходы элементов И третьей и четвертой 37рупп подключены к входам элементов ИЛИ-.НЕ второй труппы, одни и входов компаратора соединены с выходами элементов ИЛИ-НЕ групп и другими входами регистра числа и являются информационными входами устройства, другие выходы регистра числа подключены к другим входам компаратора и являются информационными выходами ус ройства, другим управллощим входом и индикаторными выходами которого явля ются -соответственно второй вход второго элемента И, прямой выход триггера и третий прямой выход счетчика режимов, а контрольными и адресньвда выходами устройства являются соответ ственно выходы регистра кодов ошибки и прямые выходы второго счетчика импульсов. На чертеже представлена функциональная схема предлагаемого устройст ва. Устройство содержит регистр 1 ад реса, первый и второй селекторы 2 и 3, первый и второй счетчики 4 и 5 импульсов, накопитель б, выполнен.ный на полупроводниковых элементах памяти, дешифратор 7, генератор 8 тактовых сигналов, регистр 9 числа, блок 10 контроля, первую. 11, вторую 12, третью 13 и четвертую 14 группы элементов И, счетчик 15 режимов, первую 16 и вторую 17 группы элементов ИЛИ-НЕ, компаратор 18, регистр 19 кодов ошибки, триггер 20 первый 21, второй 22 и третий 23 элементы И и элемент ИЛИ 24. На чертеже обозна:чены адресные. входы 25, адресные выходы 26, один. из управляюйщх вх,одов 27, информа- ционные входы 28 и выходы 29, контрольные выходы 30, один из индикаторных выходов 31, другой управляющий вход 32, предназначенный для ввода признака продолжения контроля, и другой индикаторный выход 33 устройства.. Устройство работает следующим образом. Контрольному считыванию - регенераций прелоиествует тестирование накопителя 6 с noMoinbij встроенных средств и обратным. адресным кодом, что существенно повышает достоверность контроля. После подачи на устройство сигнала предварительной установки.(не показан) счетчики 4, 5 и 15, регийтры 1, 9 и 19 и триггер 20 приходят в исходное нулевое состояние.. На входах 28 и выходах 29 присутствуют высокие: уровни напряжения, а на всех остальных входах и выходах низкие. На вторых входах групп 11 и 13 элементов И и на третьих входах групп 11-14 элементов И находятся высокие потенциалы и информация с прямых выходов счетчиков 4 и 5 поступает на входы регистра 9. На входах и выходе элемента ИЛИ 24 присутствуют низкие уровни напряжения, что соответствует режиму записи в накопитель 6. Через время t 4 - .1 ja ( где Т р период регенерация) генератор 8 начинает цикл регенерации. Содержимое счетчика 4 через селектор 2 поступает на адресные входы накопителя б, а содержимое счетчика 5 через селектор 3 - на входы дешифратора 7. Динамические запоминающие микросхемы требуют для записи или чтения информации подачи двух синхронизирующих сигналов, первый из которых поступает с генератора 8 непосредственно на входы всех запоминающих микросхем накопителя 6, а второй - на стробирующий вход дешифратора 7. Таким образом, сигналом с выхода дааИфратора 7 производится выбор в иакопителе 6 определенного ряда из п микросхем памяти (где п - длина кодового слова) . В результате в первом цикле регенерации нулевое число с входов 28 через регистр 9 поступает иа Входы накопителя б и записывается в его нулевую ячейку, а в остальных ячейках с нулевым номером строки происходит восстановление инфор-ации. По окончании цикла в счетчиК 4 с выхода генератора 8 добавится единица, которая затем появится в младшем разряде входов 28 (на информационных входа:: 28 и выходах 29 единица соответствует нулевому потенциалу), Во втором цикле регенерации это число запишется в первую ячейку накопите ля б и т.д.. Данный режим работы устройства (запись в прямом ещресном коде) пр текает Лри .нулевом состоянии :Счетч ка 15 (000) , которое сохранится до импульса переноса со счетчи ка 5. Этот импульс через элемент И 23 поступит на счетный вход счет чика 15 и изменит его состояние на 001. В результате на входе элемейта ИЛИ 24 окажется высокий уровень напряжения, на его выходе также высокий уровень, и устройство перей дет в режим считывания. Одновременн разрешается работа комапаратора 18 путем подачи низкого потенциала на его управляющий вход. Таким образом в следующем цикле регенерации произойдет считывание нулевой ячейки накопителя ,б, содержимое которой через регистр 9 поступает на входы компаратора 18, а на другие входы подается истинное значение содержи мого нулевой ячейки со счетчиков 4 и 5. Комапаратор 18 производит поразрядное сравнение информации и если сялибки нет,, сигналы на его выходах отсутствуют. Затем происходит считывание всех остальных ячеек накопи.теля б довыдачи импульса переноса со счетчика 5, после чего состояние счетчика 15 010. Так как п его первом разряде снова появится нуль, то устройс.тво возвратится в режим записи, однако выйокий уровень напряжения поступит теперь на вторые входы групп 12 и 14 элементов И, сл довательно, информация на входы 28 регистра 9 будет проходит с инверсных выходов счетчиков 4 и 5. В результате в накопителе б запишется инверсный адресный код. Когда состояние счетчика 15 станет 011, начнется считывание этого кода по завершении которого в счетчике 15 окажется число 100. Единица с ег третьего прямого выхода поступит на выход 33 как признак конца контроля , сообщая внешним устройствам о готовности .запоминающего устройст ва к решению згшачи. ОдноЕ еменно запрещается вьвдача содержимого счет чиков 4 и 5 на входы 28 регистра 9 путем установки низкого потенциала на третьих входах групп 14-14 элементов И. Р дальнейшем в режиме регенерации с генератора 8 на вход элемента ИЛИ 24 будет выдаваться высокий уровень напряжения, обеспечивая последовательное считывание ячеек накопителя 6 и проверку их со держимого в блоке 10 контроля. Рассмотрим pai6oTy устройства при об наружении компаратором 18 ошибки в считанном слове. а этом случае отличная от нуля информация с выходов поразрядного сравненияКомпаратора 18 записываэтся в регистр 19, а затем поступает на выходы 30. Одновременно при , несовпадении хотя бы в одном разряде с другого выхода компаратора 18 выдаётся положительный имдульс, переводящий триггер 20 в единичное состояние. На прямом выходе триггера 0 возникает высокий потенциал, который поступает на выход 31 устройства как признак ошибки, а низкий уровень напряжения с его инверсного выхода запрещает прохождение импульсов переноса счетчика 4 через элемент И 21 на вход счетчика 5. Таким образом, на выходах 26 фиксируется код, соответствующий сщресу отказавшего ряда запоминающих микросхем накопителя б, который совместно с кодом на выходах 30 позволяет локализовать неисправность с точностью до одной микросхемы накопителя б. Получив сигнал с выхода 31, внешний процессор считывает информацию с выходов 26 и 30 и выставляет высокий потенциал на вход 32 как признак продолжения контроля. После прихода очередного импульса переноса счетчика 4 элемент И 22 открывается и возвращает триггер 20 в исходное состояние, на втором входе элемента И 21 оказывается высокий уровень напряжения и в счетчик 5 прибавляется единица. ЗАтем начинается считывание из следующего ряда запоминающих микросхем накопителя б. Получив признак конца контроля по выходу 33, внешний процессор либо подключает резервное запоминающее устройство (при значительном числе неисправностей), либо обходит при решении задачи отказавшие области памяти накопителя б, что нетрудно осуществить, так как они определяются старшими разрядами адреса на выходе 26. Для возобновления контроля устройства по рассмотренному алгоритму необходимо подать на него сигнал предварительной установки. После появления единицы на выходе 33 как признака конца контроля внешние устройства системы могут начать обмен с накопителем 6. В режиме записи адрес выбранной ячейки по входам 25 поступает в регистр 1, а признак записи по входам 27 - в генератор 8. Последний стробирует селекторы 2 и 3, разрешая прохождение гщреса с регистра 1, и обеспечивает режим записи в. накопитель 6 установкой низкого потенциала на входе элемента ИЛИ 24. Записываемое число поступает на входы 28 и через регистр 9 на входы накопителя 6. В режиме считывания на вход элемента ИЛИ 24 с генератора 8 выдается высокий потенциал, обеспечивая чтение ячейки накопителя б по адресу поступившему в регистр 1. Считанное число через регистр 9 проходит на выходы 29 и в блок 10 контроля, где определяется наличие ошбки.

Предпагаёмое устройство позволяет существенно повысить .достоверность контроля за счет выявления ошибок VHпа эакреппения нуля (ши единицы, а также проверки адресного тракта, так как неиспрайности данного вида явля4tf

о

ются для ЗУ ocHoBHUNm, то надежность устройвтва значительно возрастает, проводить -профилактический крл троль

устройства до начала решения задачи без использования стендового оборудо вания, организовать прогргммным путем обход отказавцшх облгостей накопи

теля. . .: - ,.: : -

Предлагаемое устройство OTJtrt4ai&T ся более высокой надежность по сравнению с .

MZHJ

.28

ш

Зв

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Журавлев Ю.П., Котелюк Л.А., 1Ыклинский И.И | |||

| Надежность и | |||

| контроль ЭВМ | |||

| М., Сов | |||

| радио, 1978, с | |||

| Ручной прибор для загибания кромок листового металла | 1921 |

|

SU175A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 760194, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-06-07—Публикация

1982-03-15—Подача