1

Изобретение относится к области автоматики и вычислительной техники.

Известен распределитель импульсов, выполненный на элементах И-ИЛИ-НЕ по кольцевой схеме. Недостатками такого распределения являются слол-сность схемы и низкая надежность 1.

Известен также распределитель импульсов, содержащий триггеры на элементах И-НЕ в каждом из п каналов, соединенных в кольцо, и шины двухтактного запуска 2. НедостатKOiM такого распределителя является то, что он содержит потенциальные логические элементы И-ИЛИ-НЕ, которые по сложности схемы и количеству ее элементов превосходят логические элементы И-НЕ.

Цель изобретения - упрощение схемы распределителя импульсов.

Это достигается тем, что выход первого плеча каждого п-го триггера соединен с одним из входов первого плеча всех последзющих триггеров, кроме предшествующего, причем шина первого такта запуска соединена со входами второго плеча всех четных, а шина второго такта запуска - со входами второго плеча всех нечетных триггеров.

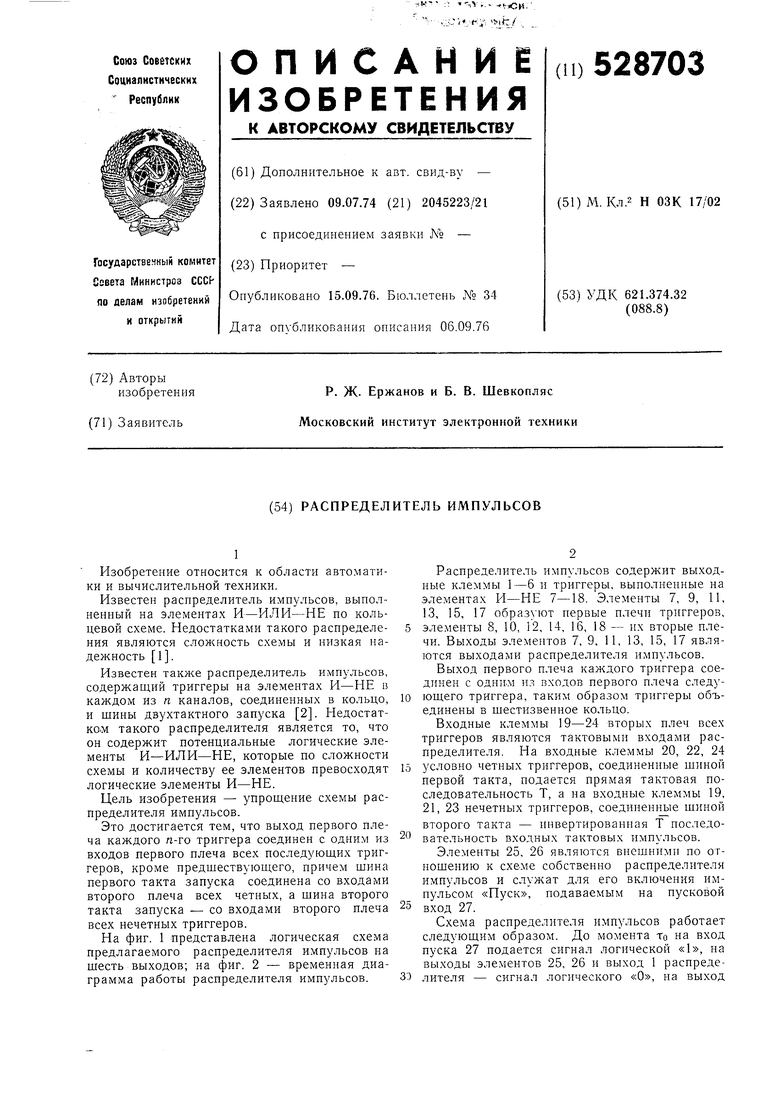

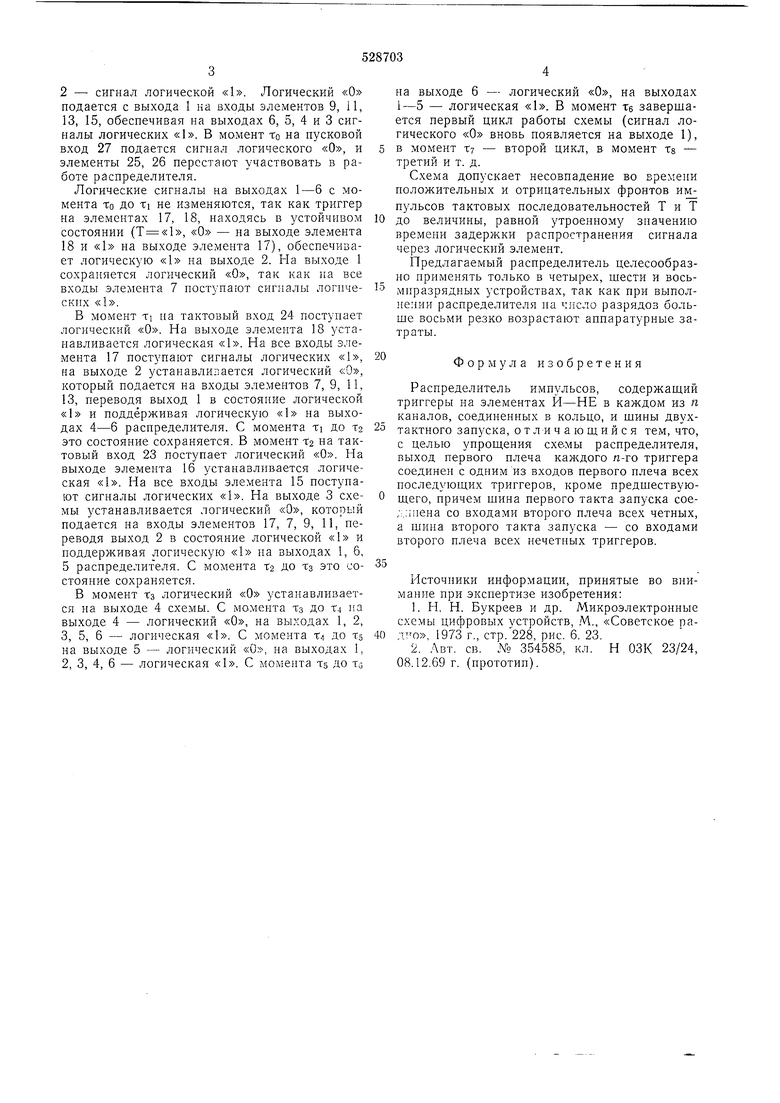

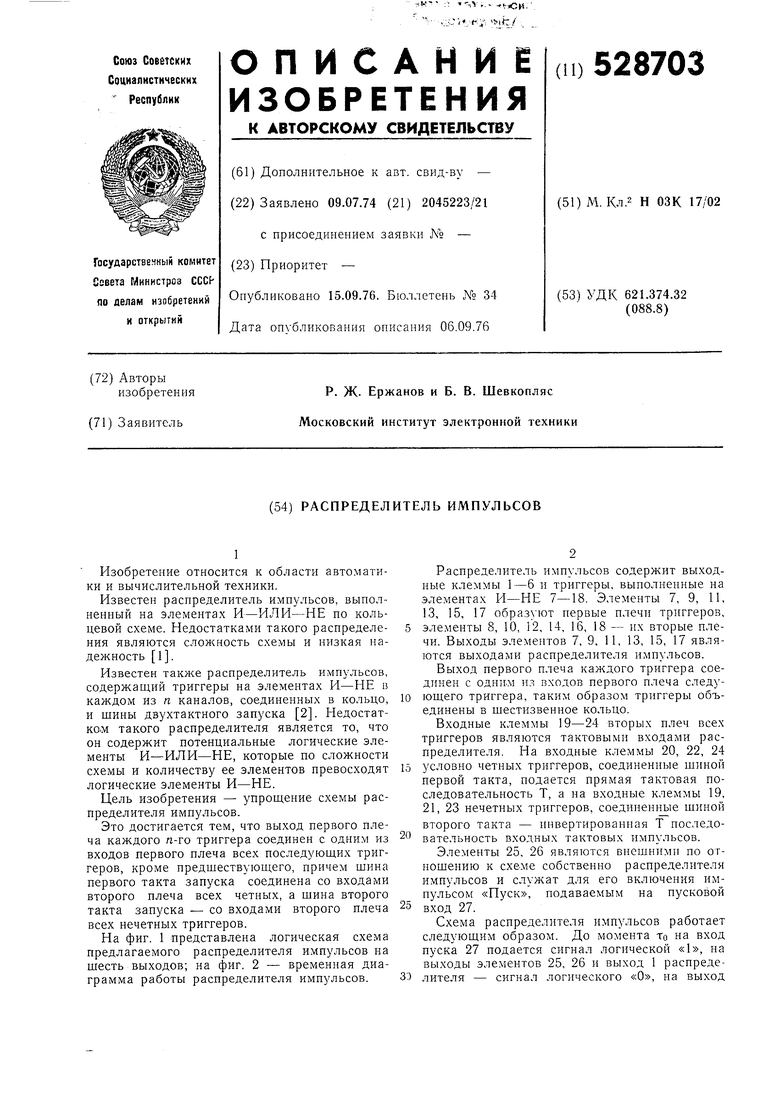

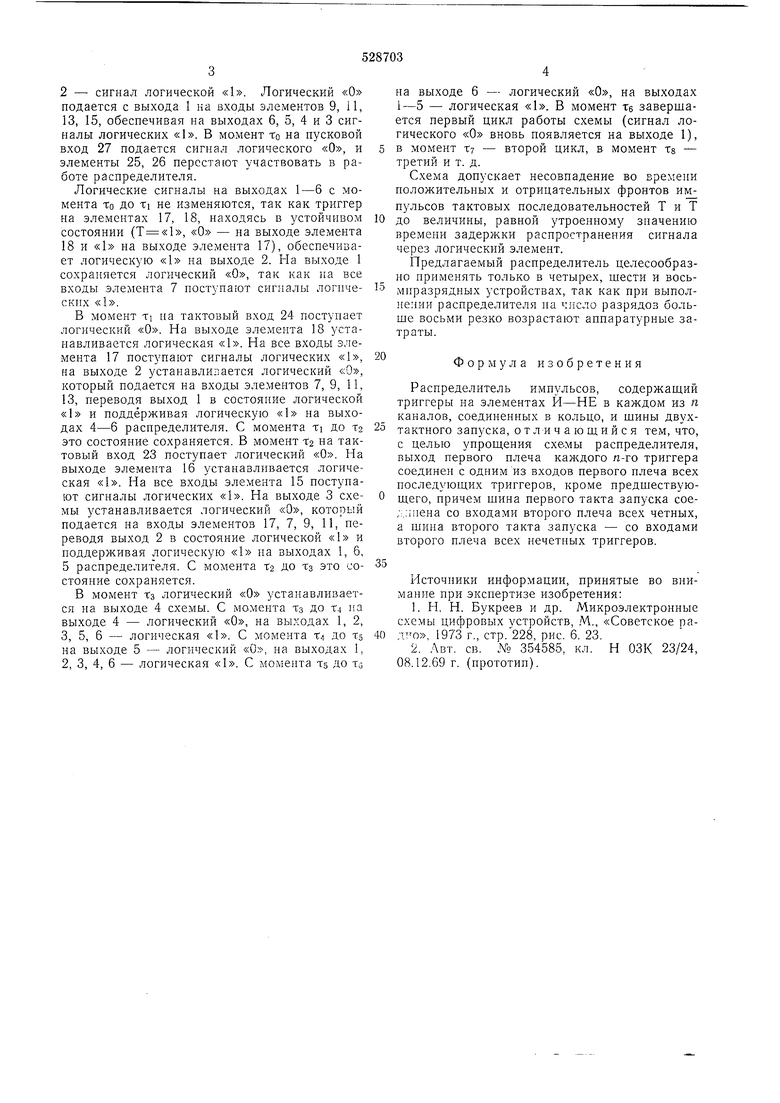

На фиг. 1 представлена логическая схема предлагаемого распределителя импульсов на шесть выходов; на фиг. 2 - временная диаграмма работы распределителя импульсов.

Распределитель импульсов содержит выходные клеммы 1-6 и триггеры, выполненные на элементах И-НЕ 7-18. Элементы 7, 9, 11, 13, 15, 17 образуют первые плечи триггеров, элементы 8, 10, 12, 14, 16, 18 - их вторые плечи. Выходы элементов 7, 9, 11, 13, 15, 17 являются выходами распределителя импульсов.

Выход первого плеча каждого триггера соединен с одни.м из входов первого плеча следующего триггера, таким образом триггеры объединены в шестизвенное кольцо.

Входные клеммы 19-24 вторых плеч всех триггеров являются тактовыми входами распределителя. На входные клеммы 20, 22, 24 условно четных триггеров, соединенные шиной первой такта, подается прямая тактовая последовательность Т, а на входные клеммы 19, 21, 23 нечетных триггеров, соединение шиной

второго такта - инвертированная Т носледовательность входных тактовых импульсов.

Элементы 25, 26 являются внешними по отношению к схеме собственно распределителя импульсов и служат для его включения импульсом «Нуск, подаваемым на пусковой

вход 27.

Схема распределителя импульсов работает следующим образом. До момента TO на вход пуска 27 подается сигнал логической «1, на выходы элементов 25, 26 и выход 1 распределителя - сигнал логического «О, на выход

2 - сигнал логической «1. Логический «О иодается с выхода 1 ка входы элементов 9, И, 13, 15, обеспечивая на выходах 6, 5, 4 и 3 сигналы логических «1. В момеит to иа иусковой вход 27 подается сигнал логического «О, и элементы 25, 26 перестают участвовать в работе распределителя.

Логические сигналы на выходах 1-6 с момента То до TI не изменяются, так как триггер на элементах 17, 18, находясь в устойчивом состоянии (, «О - на выходе элемента 18 и «1 иа выходе элемента 17), обеспечивает логическую «1 на выходе 2. На выходе 1 сохраняется логический «О, так как на все входы элемента 7 поступают сигналы логических «1.

В момент T на тактовый вход 24 поступает логический «О. На выходе элемента 18 устанавливается логическая «1. На все входы элемента 17 поступают сигналы логических «1, на выходе 2 устанавливается логический «О, который подается на входы элементов 7, 9, 11, 13, переводя выход 1 в состояние логической «1 и поддерживая логическую «1 на выходах 4-6 расиределителя. С момента TI до тг это состояние сохраняется. В момеит Т2 на тактовый вход 23 поступает логический «О. На выходе элемента 16 устанавливается логическая «1. На все входы элемента 15 поступают сигналы логических «1. На выходе 3 схемы устанавливается логический «О, который подается на входы элементов 17, 7, 9, 11, переводя выход 2 в состояние логической «1 и поддерживая логическую «1 на выходах 1, 6, 5 распределителя. С момента Т2 до тз это состояние сохраняется.

В момент Гз логический «О устанавливается на выходе 4 схемы. С мо.мента Тз до Т4 на выходе 4 - логический «О, иа выходах 1, 2, 3, 5, 6 - логическая «1. С момента Т4 до TS на выходе 5 - логический «О, на выходах 1, 2, 3, 4, 6 - логическая «1. С момента TS до TG

на выходе 6 - логический «О, иа выходах 1-5 - логическая «1. В момент те завершается первый цикл работы схемы (сигнал логического «О вновь появляется на выходе 1), в момент Ту - второй цикл, в момеит тв - третий и т. д.

Схема доцускает несовпадение во вре.мени положительиых и отрицательных фронтов импульсов тактовых последовательностей Т и Т до величины, равной утроенному значению времени задержки распространения сигнала через логический элемент.

Нредлагаемый распределитель целесообразио применять только в четырех, шести и восьмиразрядных устройствах, так как при выполнении распределителя иа число разрядов больше восьми резко возрастают аппаратуриые затраты.

Формула изобретения

Распределитель импульсов, содержаш,ий триггеры на элементах И-НЕ в каждом из п каналов, соединенных в кольцо, и шины двухтактного запуска, отличающийся тем, что, с целью уирощения схемы распределителя, выход первого плеча каждого /г-го триггера соединен с одним из входов первого плеча всех последуюших триггеров, кроме предшествующего, причем шина первого такта запуска сое;:.:п1ена со входами второго плеча всех четных, а шина второго такта запуска - со входами второго плеча всех нечетных триггеров.

Источники ииформации, прииятые во виимание при экспертизе изобретения:

1.Н. Н. Букреев и др. Микроэлектронные схемы цифровых устройств, М., «Советское ра;uo, 1973 г., стр.228, рис. 6. 23.

2.Авт. св. № 354585. кл. Н ОЗК 23/24, 08.12,69 г. (ирототип).

uS.l

IP T-j Т2 Zs

. 2

Ту

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный распределитель | 1983 |

|

SU1109903A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU957404A2 |

| Распределитель тактовых импульсов | 1986 |

|

SU1411966A1 |

| Регистр сдвига | 1978 |

|

SU771724A1 |

| Распределитель импульсов | 1985 |

|

SU1298887A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1981 |

|

SU964951A1 |

| Распределитель импульсов | 1988 |

|

SU1529204A1 |

| Триггерное устройство | 1980 |

|

SU930684A2 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1970 |

|

SU277841A1 |

| Распределитель | 1979 |

|

SU822368A1 |

Авторы

Даты

1976-09-15—Публикация

1974-07-09—Подача