1

Изобретение относится к импульсной технике и предназначено для формирования распределенных во времени импульсов.

Известен .распределитель, содержащий в каждом разряде-триггер с раздельными входами на логических элементах И-НЕ (ИЛИ-НЕ). Выход каждого из логических элементов, осуществляющих сдвиг единицы в триггерах, соединен с нулевым входом триггера данного разряда, с единичным входом смежного с ним трих-гера с той стороны, в которую нербходимо осуществить сдвиг единицы, и со входом логического элемента, другой вхо которого соединен с нулевым плечом триггера данного разряда, а выход - .со входом данного логического элемента l .

Недостатком этого распределителя является относительно низкая дос-. товерность функционирования.

Известен также распределитель, сдержащий разрядные триггеры, инверсный выход каждого из которых соединен с входом установки следующего разрядного триггера, элемент И-НЕ и блок формирования тактовых сигналов вход которого соединен с тактовым

входом распределителя, вход сброса которого соединен со входами сброса всех разрядных триггеров, кроме первого, первый выход блока формирования тактовых сигналов соединен с входами установки нуля нечетных разрядных триггеров, входы установки нуля четных разрядных триггеров соединены с вторым выходом блока формирования тактовых сигналов 2.

Недостатком этого распределителя является относительно низкая достоверность функционирования.

Цель изобретения - повышение дос5товерности функционирования.

Поставленная цель достигается тем, что в распределитель., содержа дий разрядные триггеры, инверсный выход каждого из которых соединен с

0 входом установки следующего разрядного триггера, элемент И-НЕ и блок формирования-тактовых сигналов, вход которого соединен с тактовым входом распределителя, вход сброса которо5го соединен с входами сброса всех разрядных триггеров, кроме первого, первый выход блока формирования тактовых сигналов соединен с входами установки нуля нечетных разрядных

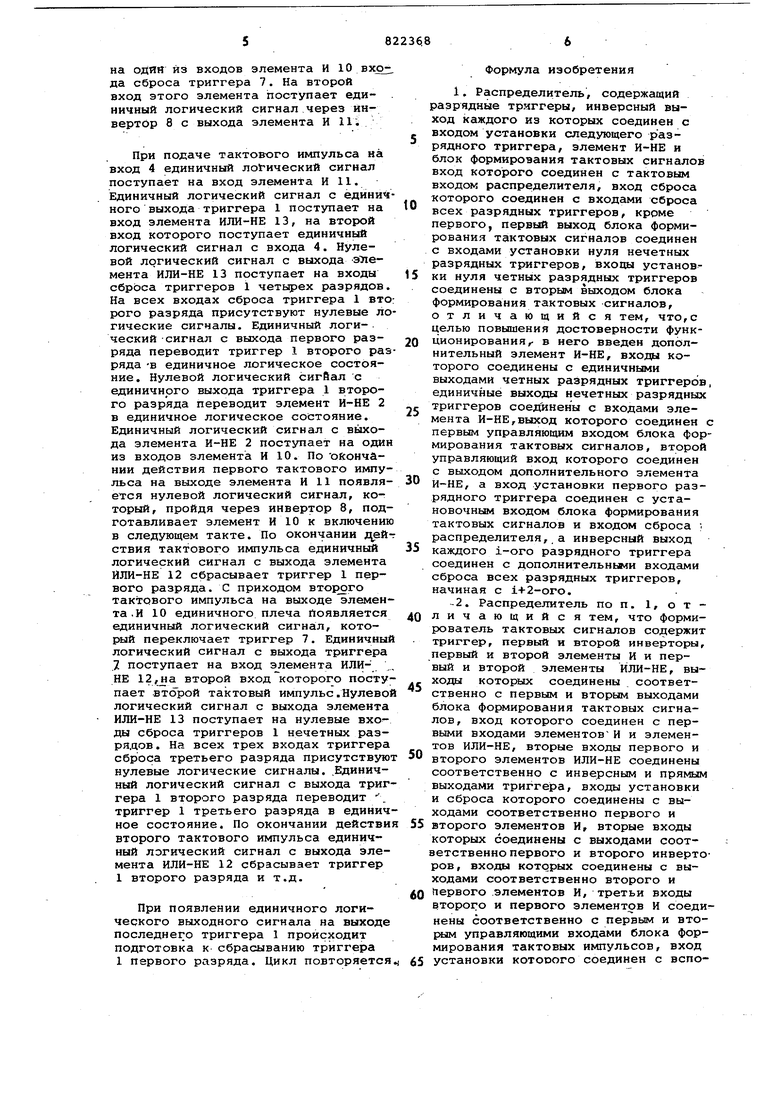

0 триггеров, входы установки нуля четных разрядных триггеров соединен с вторым выходом блока формирования тактовых сигналов, введен дополнительный элемент И-НЕ, входы которог соединены с единичными выходами чет ных разрядных триггеров, единичные выходы нечетных разрядных триггеров соединены с входами элемента И-НЕ, выход которого соединен с первым уп равляющим входом блока формирования тактовых сигналов, второй управляющий вход которого соединен с выходом дополнительного элемента И-НЕ, а вход установки первого разрядного триггера соединен с установочным вх дом блока формирования тактовых сигналов и входом сброса распредели теля, а инверсный выход каждого i-oro разрядного триггера соединен с дополнительными входами сброса всех разрядных триггеров, начиная с 14-2-ого. Формирователь тактовых сигналов содержит триггер, первый и второй инверторы, первый и второй элементы И и первый и .второй элементы ИЛИ-НЕ, выходы которых соединены соответственно с первым и вторым выходами блока формирования тактовых сигналов, вход которого соединен с первыми входами элементов И и элементов ИЛИ-НЕ, вторые вх ды первого и второго элементов ИЛИНЕ соединены соответственно с инвер ным и прямым выходами триггера, вхо ды установки и сброса которого соединены с выходами соответственно ne вого и второго элементов И вторые входы которых соединены с выходами соответственно первого и второго ин верторов, входы которых соединены с выходами соответственно второго и первого элементов И, третьи входы второго и первого элементов И соеди иены соответственно с первым и вторым управляющими входами блока формирования тактовых импульсов, вход установки которого соединен с вспом гательным установочным входом триггера. На чертеже дана структурная схем предлагаемого распределителя. Распределитель содержит разрядны триггеры 1, инверсный выход каждого из.которых соединен с входом установки следующего разрядного триггера,, элемент И-НЕ 2, блок 3 формиров Hf -тактовых сигналов, вход которого соединен с тактовым входом 4 рас пределителя, вход 5 сброса которого соединен с входами сброса всех разрядных триггеров 1, кроме первого, первый выход блока 3 формирования тактовых сигналов соединен с входам установки нуля нечетных разрядных триггеров 1, входы установки нуля четных разрядных триггеров 1 соединены с вторым выходом блока 3 формирования тактовых сигналов, дополнительный элемент И-НЕ 6, входы которого соединены с единичными выходами четных разрядных триггеров 1, единичные выходы нечетных разрядных триггеров 1 соединены с входами элемента И-НЕ 2, выход которого соединен с первым управляющим входом блока 3 формирования тактовых сигналов , второй управляющий вход которого соединен с выходом дополнительного элемента И-НЕ б, а вход установки первого разрядного триггера - с установочным входом блока 3 формирования тактовых сигналов и входом 5 сброса распределителя. Инверсный выход каждого 1-ого разрядного триггера соединен с дополнительными входами сброса всех разрядных триггеров, начиная с i+2-ого. Формирователь 3 тактовых сигналов содержит триггер 7, первый 8 и второй 9 инверторы, первый 10 и второй 11 элементы И, первый 12 и второй 13 элементы ИЛИНЕ, выходы которых соединены соответственно с первым и вторым выходами блока 3 формирования тактовых сигналов, вход которого соединен с первыми входами э.лементов И 10 и 11 и элементов ИЛИ-НЕ 12 и 13, вторые входы первого 12 и второго 13 элементов ИЛИ-НЕ соединены соответственно с инверсным и прямым выходами триггера 7, входы установки и сброса которого соединены с выходами соответственно первого 10 и второго 11 элементов И, вторые входы которых соединены с выходами соответственно первого 8 и второго 9 инверторов, входы которых соединены с выходами соответственно второго 11 и первого 10 элементов И, третьи входы второго 11 и первого 10 элементов И соединены соответственно с первым и вторым управляющими входами блока 3 формирования тактовых сигналов, вход установки которого соединен с вспомогательным установочным входом триггера 7. Распределитель работает следующим . образом. При появлении единичного логичес-кого сигнала установки нуля, по входу 5 на нулевом выходе триггера 7 появляется единичный логический сигнал, который поступает на один из входов элемента ИЛИ-НЕ 13.Нулевой логический сигнал,появляющийся на выходе элемента ИЛИ-НЕ 13,поступает на нулевой вход первого разрядного триггера, разрешая тем самым единичному логическому сигналу установки нуля по входу 5 на установочном входе триггера перевести его в состояние логической единицы.Нулевой логический сигнал с единичного выхода триггера первого разряда переводит элемент И-НЕ 2 нечетных разрядов в состояние логиеской единицы, единичный логический сигнал с которого поступает на одЯй из входов элемента И 10 входа сброса триггера 7. На второй вход этого элемента поступает единичный логический сигнал через инвертор 8 с выхода элемента И 11. При подаче тактового импульса на вход 4 единичный логический сигнал поступает на вход элемента И 11. Единичный логический сигнал с единич ного выхода триггера 1 поступает на вход элемента ИЛИ-НЕ 13, на второй вход которого поступает единичный логический сигнал с входа 4. Нулевой логический сигнал с выхода элемента ИЛИ-НЕ 13 поступает на входы сброса триггеров 1 четырех раэрядов. На всех входах сброса триггера 1 вто рого разряда присутствуют нулевые ло гические сигналы. Единичный логи- ческий -сигнал с выхода первого разряда переводит триггер 1 второго раз ряда -в единичное логическое состояние. Нулевой логический сигйал с единичного выхода триггера 1 второго разряда переводит элемент И-НЕ 2 в единичное логическое состояние. Единичный логический сигнал с выхода элемента И-НЕ 2 поступает на один из входов элемента И 10. По окончании действия первого тактового импульса на выходе элемента И 11 появляется нулевой логический сигнал, который, пройдя через инвертор 8, подготавливает элемент И 10 к включению в следующем такте. По окончании ствия тактового импульса единичный логический сигнал с выхода элемента ИЛИ-НЕ 12 сбрасывает триггер 1 первого разряда. С приходом второго тактового импульса на выходе элемента .И 10 единичного плеча Появляется единичный логический сигна л, который переключает триггер 7. Единичный логический сигнал с выхода триггера 1 поступает на вход э лемента ИЛИ- , НЕ 12,на второй вход которого посту пает второй тактовый импульс.Нулево логический сигнал с выхода элемента ИЛИ-НЕ 13 поступает на нулевые вхо ды сброса триггеров 1 нечетных раэрядов. На всех трех входах триггера сброса третьего разряда присутствую нулевые логические сигналы. .Единичный логический сигнал с выхода триг гера 1 второго разряда переводит , триггер 1 третьего разряда в единич ное состояние. По окончании действи второго тактового импульса единичный логический сигнал с выхода элемента ИЛИ-НЕ 12 сбрасывает триггер 1 второго разряда и т.д. При появлении единичного логического выходного сигнала на выходе последнего триггера 1 происходит подготовка к сбрасыванию триггера 1 первого разряда. Цикл повторяется Формула изобретения 1. Распределитель, содержащий разрядные триггеры, инверсный выход каждого из которых соединен с входом установки следующего разрядного триггера, элемент И-НЕ и блок формирования тактовых сигналов вход которого соединен с тактовым входом распределителя, вход сброса которого соединен с входами сброса всех разрядных триггеров, кроме первого, первый выход блока формирования тактовых сигналов соединен с входами установки нуля нечетных разрядных триггеров, входы установки нуля четных разрядных триггеров соединены с вторым выходом блока формирования тактовых сигналов, отличающийся тем, что,с целью повышения достоверности функционнрования,- в него введен допол- ннтельный элемент И-НЕ, входы которого соединены с единичными выходами четных разрядных триггеров, единичные выходы нечетных разрядных триггеров соединены с входами элемента И-НЕ,выход которого соединен с первым управляющим входом блока формирования тактовых сигналов, второй управляющий вход которого соединен с выходом дополнительного элемента И-НЕ, а вход установки первого разрядного триггера соединен с установочным входом блока формирования тактовых сигналов и входом сброса ; распределителя,.а инверсный выход каждого i-oro раэрядного триггера соединен с дополнительными входс1ми сброса всех разрядных триггеров, начиная с i+2-ого. -2. Распределитель по п. 1, отличающийся тем, что формирователь тактовых сигналов содержит триггер, первый и второй инверторы, первый и второй элементы И и первый н второй элементы ЙЛИ-НЕ, выходы которых соединены соответственно с первьм и вторым выходами блока формирования тактовых сигналов, вход которого соединен с первыми входами элементовИ и элементов ИЛИ-НЕ, вторые входы первого и второго элементов ИЛИ-НЕ соединены соответственно с инверсным и прямым выходами триггера, входы установки и сброса которого соединены с выходами соответственно первого и второго элементов И, вторые входы которых соединены с выходами соответственно первого и второго инверторов, входы которых соединены с выходами соответственно второго и Первого элементов И, третьи входы второго и первого элементов И соединены соответственно с первым и вторым управляющими входами блока формирования тактовых импульсов, вход установки КОТОРОГО соединен с вспомогательньвл установочным входом триггера .

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 350179, кл. Н 03 К 23/02, .

2.Авторское свидетельство СССР

364109,кл. Н 03 К 23/02,1973 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для контроля распределителя | 1983 |

|

SU1128260A2 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Распределитель импульсов | 1981 |

|

SU1003357A2 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

Авторы

Даты

1981-04-15—Публикация

1979-06-27—Подача