Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных резервированных распределителей тактовых импульсов.

Целью изобретения является повышение надежности за счет взаимной синхронизации разрядов.

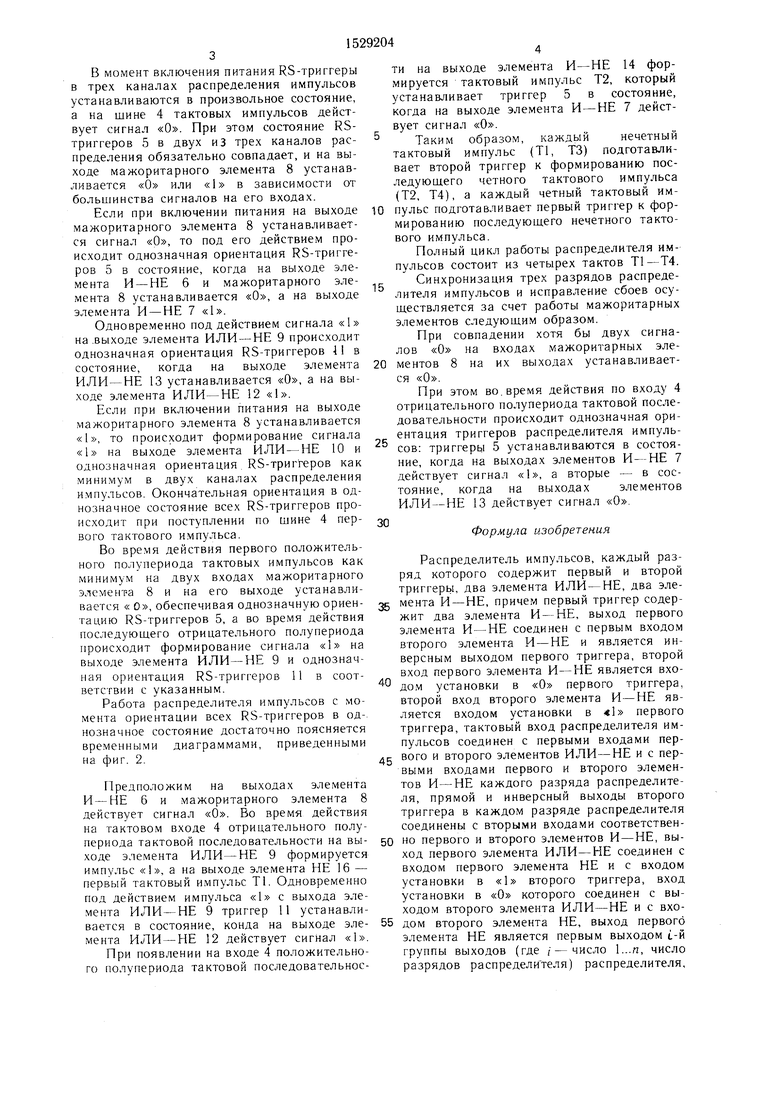

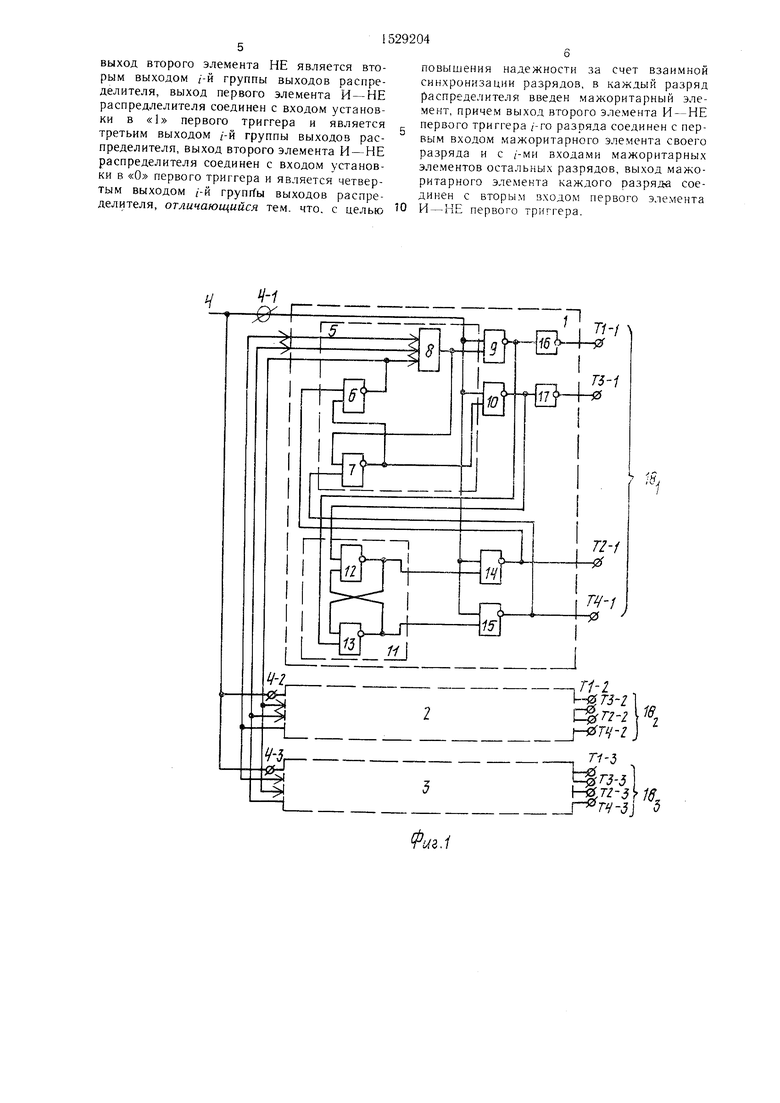

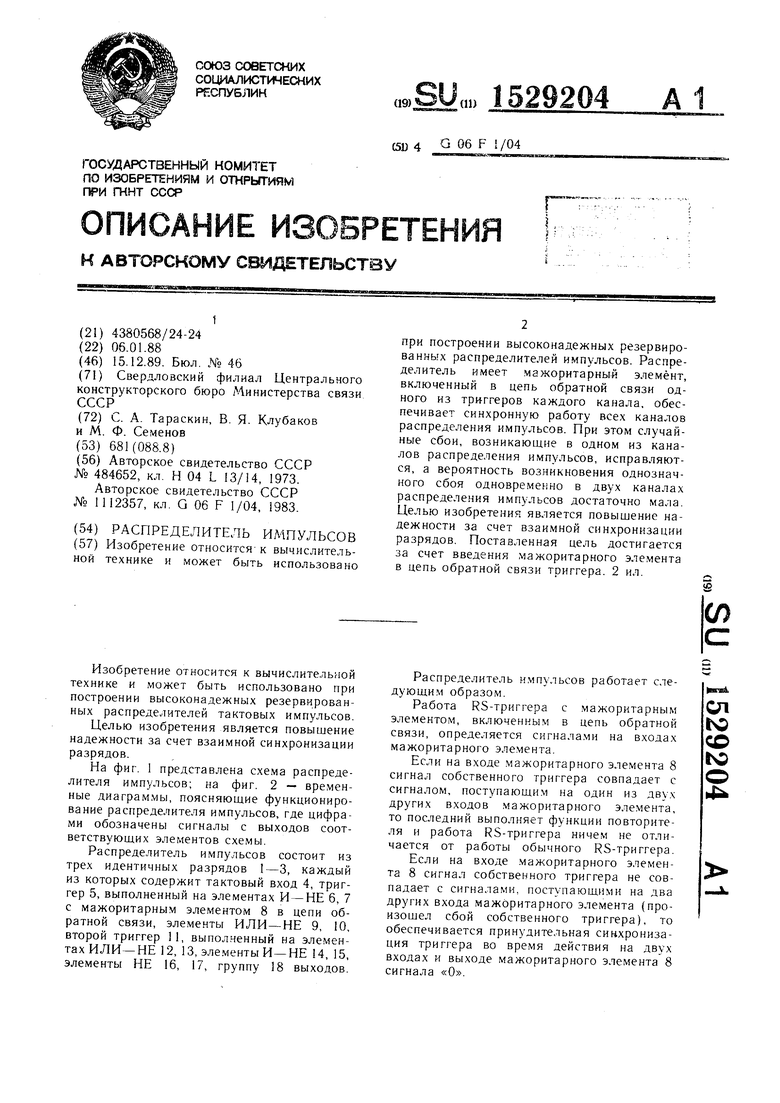

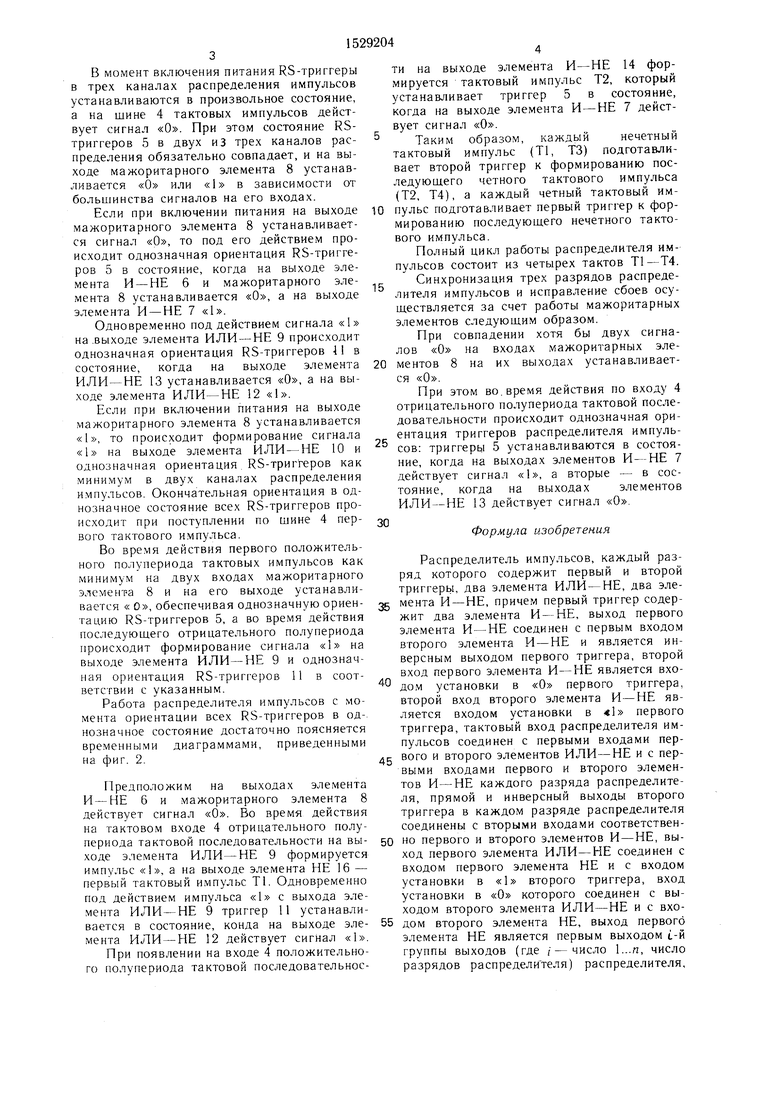

На фиг. 1 представлена схема распределителя импульсов; на фиг. 2 - временные диаграммы, поясняющие функционирование распределителя импульсов, где цифрами обозначены сигналы с выходов соответствующих элементов схемы.

Распределитель импульсов состоит из трех идентичных разрядов I-3, каждый из которых содержит тактовый вход 4, триггер 5, выполненный на элементах И-НЕ 6, 7 с мажоритарным элементом 8 в цепи обратной связи, элементы ИЛИ-НЕ 9, 10, второй триггер 11, выполненный на эле.мен- тахИЛИ-НЕ 12, 13, элементы И-НЕ 14, 15, элементы НЕ 16, 17, группу 18 выходов.

Распределитель импульсов работает следующим образом.

Работа RS-триггера с мажоритарным элементо.м, включенным в цепь обратной связи, определяется сигнала.ми на входах мажоритарного элемента.

Если на входе мажоритарного элемента 8 сигнал собственного триггера совпадает с сигналом, поступающим на один из двух других входов мажоритарного элемента, то последний выполняет функции повторителя и работа RS-триггера ничем не отличается от работы обычного RS-триггера.

Если на входе .мажоритарного элемента 8 сигнал собственного триггера не совпадает с сигналами, поступающими на два других входа мажоритарного элемента (произошел сбой собственного триггера), то обеспечивается принудительная синхронизация триггера во время действия на двух входах и выходе мажоритарного элемента 8 сигнала «О.

и™1

СП to

со

N)

Е5 момент включения питания RS-триггеры в трех каналах распределения импульсов устанавливаются в произвольное состояние, а на шине 4 тактовых импульсов действует сигнал «О. При этом состояние RS- триггеров 5 в двух из трех каналов распределения обязательно совпадает, и на выходе мажоритарного элемента 8 устанавливается «О или «1 в зависимости от большинства сигналов на его входах.

Если при включении питания на выходе мажоритарного элемента 8 устанавливается сигнал «О, то под его действием происходит однозначная ориентация RS-тригге- ров 5 в состояние, когда на выходе элемента И - НЕ 6 и мажоритарного элемента 8 устанавливается «О, а на выходе элемента И - НЕ 7 «1.

Одновременно под действием сигнала «1 на .выходе элемента ИЛИ - НЕ 9 происходит однозначная ориентация RS-триггеров 1 в состояние, когда на выходе элемента ИЛИ-НЕ 13 устанавливается «О, а на выходе элемента ИЛИ-НЕ 12 «.

Если при включении питания на выходе мажоритарного элемента 8 устанавливается «1, то происходит формирование сигнала «1 на выходе элемента ИЛИ - НЕ 10 и однозначная ориентация . RS-триггеров как минимум в двух каналах распределения импульсов. Окончательная ориентация в однозначное состояние всех RS-триггеров происходит при поступлении по шине 4 первого тактового импульса.

Во время действия первого положительного полупериода тактовых импульсов как минимум на двух входах мажоритарного элемента 8 и на его выходе устанавливается « О, обеспечивая однозначную ориентацию RS-триггеров 5, а во время действия последуюшего отрицательного полупериода происходит формирование сигнала «1 на выходе элемента ИЛИ-НЕ 9 и однозначная ориентация RS-триггеров 11 в соответствии с указанным.

Работа распределителя импульсов с момента ориентации всех RS-триггеров в од-, нозначное состояние достаточно поясняется временными диаграммами, приведенными на фиг. 2.

Предположим на выходах элемента И - НЕ 6 и мажоритарного элемента 8 действует сигнал «О. Во время действия на тактовом входе 4 отрицательного полупериода тактовой последовательности на выходе элемента ИЛИ-НЕ 9 формируется импульс «, а на выходе элемента НЕ 16 - первый тактовый импульс Т1. Одновременно под действием импульса «1 с выхода элемента ИЛИ-НЕ 9 триггер 11 устанавлити на выходе элемента И-НЕ 14 формируется тактовый импульс Т2, который устанавливает триггер 5 в состояние, когда на выходе элемента И-НЕ 7 действует сигнал «О.

Таким образом, каждый нечетный

тактовый импульс (Т1, ТЗ) подготавливает второй триггер к формированию последующего четного тактового импульса (Т2, Т4), а каждый четный тактовый им- 10 пульс подготавливает первый триггер к формированию последуюшего нечетного тактового импульса.

Полный цикл работы распределителя импульсов состоит из четырех тактов Т1-Т4.

Синхронизация трех разрядов распределителя импульсов и исправление сбоев осу- шествляется за счет работы мажоритарных элементов следуюш.им образом.

При совпадении хотя бы двух сигналов «О на входах мажоритарных элементов 8 на их выходах устанавливается «О.

При этом во. время действия по входу 4 отрицательного полупериода тактовой последовательности происходит однозначная ориентация триггеров распределителя импуль- сов: триггеры 5 устанавливаются в состояние, когда на выходах элементов И-НЕ 7 действует сигнал «1, а вторые - в состояние, когда на выходах элементов ИЛИ-НЕ 13 действует сигнал «О.

15

20

30

40

Формула изобретения

Распределитель импульсов, каждый разряд которого содержит первый и второй триггеры, два элемента ИЛИ-НЕ, два эле мента И-НЕ, причем первый триггер содержит два элемента И - НЕ, выход первого элемента И-НЕ соединен с первым входом второго элемента И - НЕ и является инверсным выходом первого триггера, второй вход первого элемента И-НЕ является входом установки в «О первого триггера, второй вход второго элемента И-НЕ является входом установки в «1 первого триггера, тактовый вход распределителя импульсов соединен с первыми входами пер45 вого и второго элементов ИЛИ-НЕ и с первыми входами первого и второго элементов И-НЕ каждого разряда распределителя, прямой и инверсный выходы второго триггера в каждом разряде распределителя соединены с вторыми входами соответствен50 но первого и второго элементов И - НЕ, выход первого элемента ИЛИ-НЕ соединен с входом первого элемента НЕ и с входом установки в «1 второго триггера, вход установки в «О которого соединен с выходом второго элемента ИЛИ-НЕ и с вховается в состояние, конда на выходе эле- 55 дом второго элемента НЕ, выход первогб

мента ИЛИ-НЕ 12 действует сигнал «i. При появлении на входе 4 положительного полупериода тактовой последовательносэлемента НЕ является первым выходом t-й группы выходов (где /-число 1...П, число разрядов распредели теля) распределителя.

ти на выходе элемента И-НЕ 14 формируется тактовый импульс Т2, который устанавливает триггер 5 в состояние, когда на выходе элемента И-НЕ 7 действует сигнал «О.

Таким образом, каждый нечетный

тактовый импульс (Т1, ТЗ) подготавливает второй триггер к формированию последующего четного тактового импульса (Т2, Т4), а каждый четный тактовый им- 0 пульс подготавливает первый триггер к формированию последуюшего нечетного тактового импульса.

Полный цикл работы распределителя импульсов состоит из четырех тактов Т1-Т4.

Синхронизация трех разрядов распределителя импульсов и исправление сбоев осу- шествляется за счет работы мажоритарных элементов следуюш.им образом.

При совпадении хотя бы двух сигналов «О на входах мажоритарных элементов 8 на их выходах устанавливается «О.

При этом во. время действия по входу 4 отрицательного полупериода тактовой последовательности происходит однозначная ориентация триггеров распределителя импуль- сов: триггеры 5 устанавливаются в состояние, когда на выходах элементов И-НЕ 7 действует сигнал «1, а вторые - в состояние, когда на выходах элементов ИЛИ-НЕ 13 действует сигнал «О.

0

30

Формула изобретения

Распределитель импульсов, каждый разряд которого содержит первый и второй триггеры, два элемента ИЛИ-НЕ, два элемента И-НЕ, причем первый триггер содержит два элемента И - НЕ, выход первого элемента И-НЕ соединен с первым входом второго элемента И - НЕ и является инверсным выходом первого триггера, второй вход первого элемента И-НЕ является входом установки в «О первого триггера, второй вход второго элемента И-НЕ является входом установки в «1 первого триггера, тактовый вход распределителя импульсов соединен с первыми входами первого и второго элементов ИЛИ-НЕ и с первыми входами первого и второго элементов И-НЕ каждого разряда распределителя, прямой и инверсный выходы второго триггера в каждом разряде распределителя соединены с вторыми входами соответственно первого и второго элементов И - НЕ, выход первого элемента ИЛИ-НЕ соединен с входом первого элемента НЕ и с входом установки в «1 второго триггера, вход установки в «О которого соединен с выходом второго элемента ИЛИ-НЕ и с входом второго элемента НЕ, выход первогб

дом второго элемента НЕ, выход первогб

элемента НЕ является первым выходом t-й группы выходов (где /-число 1...П, число разрядов распредели теля) распределителя.

выход второго элемента НЕ является вторым выходом /-Й группы выходов распределителя, выход первого элемента И - НЕ распредлелителя соединен с входом установки в «1 первого триггера и является третьим выходом /-и группы выходов распределителя, выход второго элемента И-НЕ распределителя соединен с входом установки в «О первого триггера и является четвертым выходом /-Й групгТы выходов распределителя, отличающийся тем. что. с целью

повышения надежности за счет взаимной синхронизации разрядов, в каждый разряд распределителя введен мажоритарный элемент, причем выход второго элемента И - НЕ первого триггера /-го разряда соединен с первым входом мажоритарного элемента своего разряда и с /-ми входами мажоритарных элементов остальных разрядов, выход мажоритарного элемента каждого разряда соединен с BTOpbiM входом первого элемента И - НЕ первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регенерации телеграфных посылок | 1985 |

|

SU1338080A2 |

| Устройство для регистрации телеграфных посылок | 1983 |

|

SU1234977A1 |

| Распределитель импульсов с обнаружением ошибок | 1980 |

|

SU955074A1 |

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Резервированный счетчик импульсов | 1986 |

|

SU1370778A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных резервированных распределителей импульсов. Распределитель имеет мажоритарный элемент, включенный в цепь обратной связи одного из триггеров каждого канала, обеспечивает синхронную работу всех трех каналов распределения импульсов. При этом случайные сбои, возникающие в одном из каналов распределения импульсов, исправляются, а вероятность возникновения однозначного сбоя одновременно в двух каналах рапределения импульсов достаточно мала. Целью изобретения является повышение надежности за счет взаимной синхронизации разрядов. Поставленная цель достигается за счет введения мажоритарного элемента в цепь обратной связи триггера. 2 ил.

Л

:g4liLbj

7 -Н / I V

77-/

-0

Т1-1

Т2-2 S,

™ Т1-д

ГЗ-5 37-/-J /я

„r rv-Jj Ь

| Распределитель импульсов | 1973 |

|

SU484652A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Распределитель импульсов | 1983 |

|

SU1112357A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1988-01-06—Подача