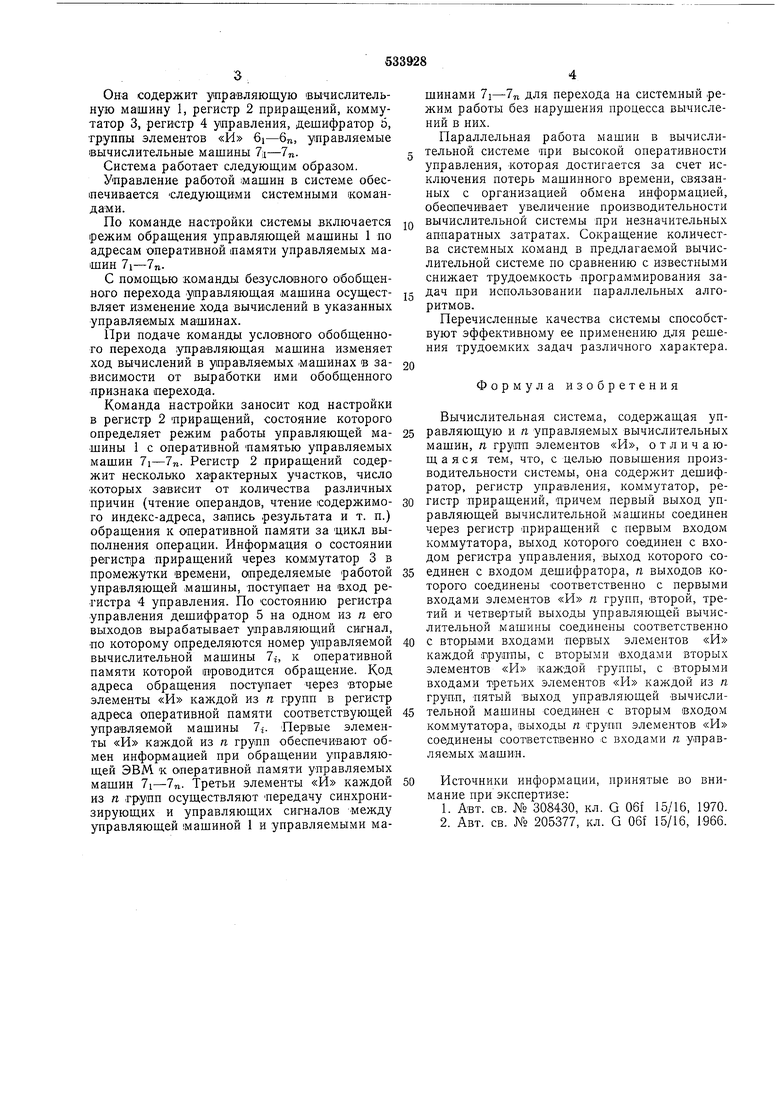

Она содержит управляющую вычислительную машину 1, регистр 2 приращений, коммутатор 3, регистр 4 управления, дешифратор 6, группы элементов «И 6i-6„, управляемые вычислительные машины 7ii-7„.

Система работает следующим образом.

Управление работой машин в системе обеспечивается Следующими системными командами.

По команде настройки системы включается режим обращения управляющей машины 1 по адресам оперативной ламяти управляемых машин -7п.

С помощью команды безусловного обобщенного перехода управляющая 1машина осуществляет изменение хода вычислений в указанных управляемых машинах.

При подаче команды условного обобщенного перехода управляющая машина изменяет ход вычислений в управляемых машинах в зависимости от выработки ими обобщенного признака перехода.

Команда настройки заносит код настройки в регистр 2 приращений, состояние которого определяет режим работы управляющей машины 1 с оперативной памятью управляемых машин -7п. Регистр 2 приращений содержит несколько характерных участков, число которых Зависит от количества различных причин (чтение операндов, чтение «одержимого индекс-адреса, запись результата и т. п.) обращения к оперативной памяти за цикл выполнения операции. Информация о состоянии ретиспра приращений через коммутатор 3 в промежутки времени, определяемые работой управляющей машины, поступает на вход регистра 4 управления. По состоянию регистра управления дешифратор 5 на одном из п его выходов вырабатывает управляющий сигнал, по которому определяются номер управляемой вычислительной машины 7j, к оперативной памяти которой проводится обращение. Код адреса обращения поступает через вторые элементы «И каждой из п групп в регистр адреса оперативной памяти соответствующей управляемой машины 7,. Первые элементы «И каждой из п групп обеспечивают обмен информацией при обращении управляющей ЭВМ к оперативной памяти управляемых машин 7i-7п- Третьи элементы «И каждой из п групп осуществляют передачу синхронизирующих и управляющих сигналов между управляющей машиной 1 и управляемыми машинами для перехода на системный режим работы без нарушения процесса вычислений в них.

Параллельная работа машин в вычислительной системе при высокой оперативности управления, которая достигается за счет исключения потерь машинного времени, связанных с организацией обмена информацией, обеспечивает увеличение производительности вычислительной системы при незначительных аппаратных затратах. Сокращение количества системных команд в предлагаемой вычислительной системе по сравнению с известными снижает трудоемкость программирования задач при использовании параллельных алгоритмов.

Перечисленные качества системы способствуют эффективному ее применению для решения трудоемких задач различного характера.

Формула изобретения

Вычислительная система, содержащая управляющую и п управляемых вычислительных машин, п групп элементов «И, отличающаяся тем, что, с целью повышения производительности системы, она содержит дешифратор, регистр управления, коммутатор, регистр приращений, причем первый выход управляющей вычислительной машины соединен через регистр приращений с первым входом коммутатора, выход которого соединен с входом регистра управления, выход которого соединен с входом дешифратора, п выходов которого соединены соответственно с первыми входами элементов «И л групп, второй, третий и четвертый выходы управляющей вычислительной машины соединены соответственно с вторыми входами первых элементов «И каждой :лруппы, с вторыми входами вторых элементов «И каждой группы, с вторыми входами третьих элементов «И каждой из п групп, пятый выход управляющей вычислительной машины соединен с вторым входом коммутатора, выходы п групп элементов «И соединены соответственно с входами л управляемых машин.

Источники информации, принятые во внимание при экспертизе:

1.Авт. св. № 308430, кл. G 06f 15/16, 1970.

2.Авт. св. № 205377, кл. G 06f 15/16, 1966.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство диспетчеризации вычислительной системы | 1980 |

|

SU951316A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Вычислительная система | 1979 |

|

SU809194A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения однородной вычислительной системы | 1978 |

|

SU769523A1 |

| СПОСОБ ФИЛЬТРАЦИИ МЕЖПРОЦЕССОРНЫХ ЗАПРОСОВ В МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2189630C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения вычислительных машин и управляющей вычислительной машины | 1984 |

|

SU1257654A1 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

Авторы

Даты

1976-10-30—Публикация

1975-01-07—Подача