Изобретение относится к вычислительной технике и может быть использовано при построении устройств диспетчеризации высокопроизводительных многомашинных вычислительных систем.

Известны устройства диспетчеризации, содержащие регистр приращений, хоммутатор, регистр управления, дешифратор, по числу управляемых вычислительных машин в системе группы элементов И 1.

Недостатком известного устройства является отсутствие возможности обеспечения оперативного обмена информацпел по инициативе управляемых вычислительных машин, из-за чего в .системе могут возникать потери машинного времени.

Наиболее близким по технической сущности к- изобретению является устройство, содержащее регистр приращений, регистр управления, первый дешифратор, первый элемент ИЛИ, группу элементов ИЛИ и N узлов |op шpoвaния сигнгшов состояния (N - число управляемых вычислительных машин), содержащих триггер запроса, регистр состояния, регистр приоритета, схему сравнения и группу элементов И, причем вход регистра приращений подключен к входу кода настройки устройства, выход регистра приращений соединен с информационным входом коммутатора, управляющий вход которого подключен к стробирующему входу устройства, выход коммутатора соединен с информационным входом регистра управления, управляющий вход которого под10к.пючен к управляющему, входу устройства, выход регистра управления соединен с входом первого дешифратора, выход которого является первым выходом устройства, входы регистров

15 состояния соединены с первой группой кодовых входов устройства, единичт ные входы триггеров запросов являются устаковочными входами устройства, нулевые входы триггеров запросов

20 соединены с выходами йоответствующих схем сравнения, входы регистров приоритета являются второй группой кодовых входов устройства, выходы регистров приоритета соединены с

25 первыми входами схем сравнения и первыми-.входами элементов И групп, вторые и управляющие входы которых соединены соответственно с выходами регистров состояния и выходами схем

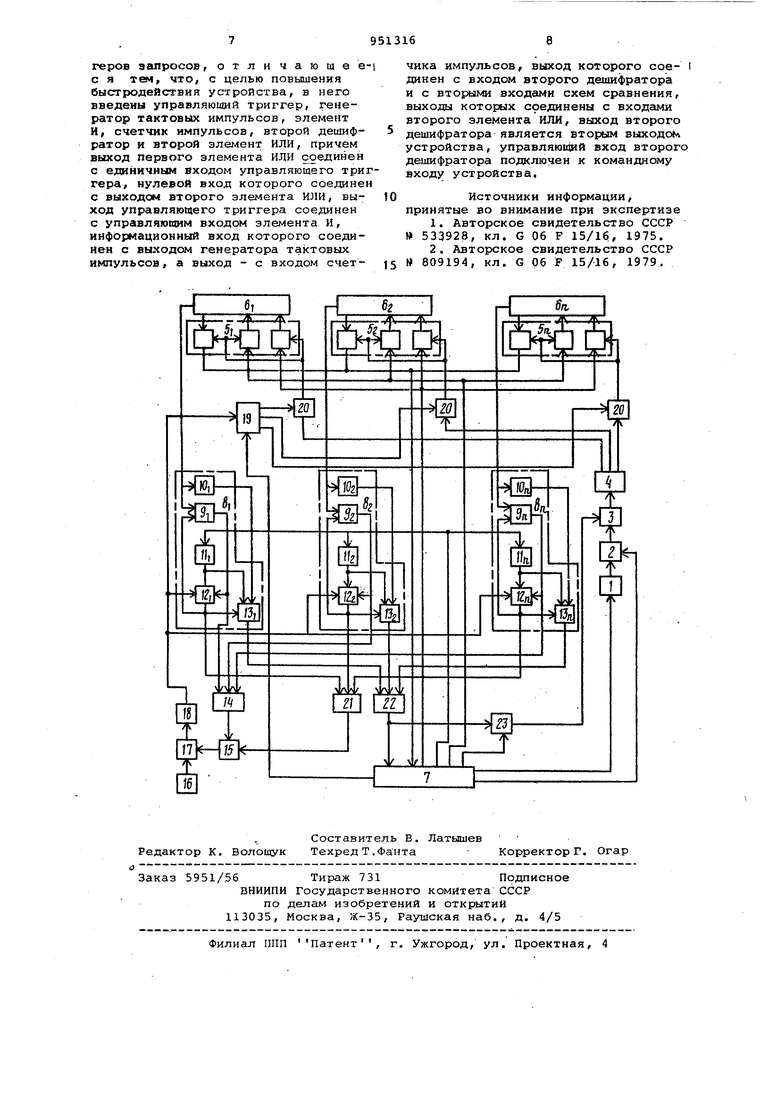

30 сравнения, а выходы - с входами элементов ИЛИ группы, выходы которалх подключены к группе управляю1дих выходов устройства, выходы триггер запросов соединены с yпpaвляющи ш входами схем сравнения, входы перво го элемента ИЛИ соединены с выходам (Триггеров запросов 2. Недостаток этого устройства сос тоит в том,что для идентификации вычислительной машины - инициатора запроса на обмен информацией - необходимо Машинное время управляющей вычислительной машины, что в свою очередь ведет к снижению эффективного быстродействия вычислительной системы. Цель изобретения - расширение функциональных возможностей устройства за счет исключения временных потерь в вычислительной системе на идентификацию вычислительной машины - инициатора обмена информацией Поставленная цель достигается тем, что в устройство введены управ ляющий триггер, генератор тактовых импульсов, элемент И, счетчик импульсов, второй дешифратор и второй элемент ИЛИ, причем выход первого элемента ИЛИ соединен с единичным входом управляющего триггера, нулев вход которого соединен с выходом второго элемента ИЛИ, выход управляющего триггера соединен с управляющим входом элемента И, информационный вход которого соединен с выходом генерато1 а тактовых импульсов , а выход - с входом счетчика им пульсов, выход которого соединен с входом второго дешифратора и с втор ми входами схем сравнения, выходы которых соединены с входами второго элемента ИЛИ, выход второго дешифратора является вторым выходом устройства, управляющий вход второго дешифратора подключен к командному входу устройства. Введение дополнительных узлов позволяет расширить функциональные возможности устройства за счет исключения потерь времени управляющей вычислительной машины, связанных с идентификацией вычислительной машины - инициатора обмена информацией, что в свою очередь существенно повышает эффективное быстродейст вие вычислительной системы. На чертеже приведена структурная схема устройства диспетчеризации вычислительной системы. Устройство содержит регистр приращений 1, коммутатор 2, регистр уп равл,ения 3, первый дешифратор 4, N узлов 8 формирования сигналов сое тояния, каждый из которых включает триггер запроса 9, регистр состояни 10, регистр 11 приоритета 11, схему сравнения 12 и группу элементов И первый элемент ИЛИ 14, управляющий триггер 15, генератор тактовых импульсов 16, элемент И 17, счетчик импульсов 18, второй дешифратор 19, второй элемент ИЛИ 21, группу элементов ИЛИ 22 и группу элементов И 23. Кроме того на схеме показаны N групп элементов И 5 (индексы обозначают номера управляемых вычислительных машин 6), управляющая ВМ 7, элементы ИЛИ 20. Работа устройства диспетчеризации вычислительной системы происходит следующим образом, В исходном положении триггеры 9 и 15, триггеры регистра 10 и счетчика 13 находятся в нулевом состоянии, что свидетельствует об отсутствии запросов на обмен информацией со стороны управляемых ВМ, На регистрах 11 находятся коды номеров ВМ, эти коды указывают на приоритетность ВМ, причем при функционировании вычислительной системы приоритетность ВМ может меняться. Обмен информацией между управляющей ВМ 7 и управляемыми ВМ 6 поинициативе управляющей ВМ 7 осуществляется путем занесения команд настройки в регистр приращений 1. Состояние регистра 1 определяет режим работы УВМ 7 по обращению к оперативной памяти ВМ б. Регистр 1 содержит несколько характерных участков, число которых зависит от количества различных причин обращения к памяти: чтение операндов, запись результатов и других обращений к оперативной памяти ВМ 6, Информация о состоянии регистра 1 через коммутатор 2 в промежутки времени, определяемые работой УВМ 7, поступает на вход регистра 3, По состоянию регистра 3 дешифратор 4 на одном из своих выходов вырабатывает управляющий сигнал, который подается на управляемые входы элементов 5 соответствующей ВМ - 6 . Код адреса обращения через вторые элементы И 5 поступает в регистр адреса оперативной памяти соответствующей ВМ 6, Первые элементы И 5 обеспечивают обмен информацией при обращении УВМ 7 к оперативной памяти ВМ 6, а третьи элементы И 5 осуществляют передачу синхронизирующих и управЛЯЮ1ЦИХ сигналов между УВМ 7 и ВМ 6 для перехода на системный режим работы без нарушения процесса вычислений в них. Обмен информацией по инициативе одной из ВМ 6 с УВМ 7 осуществляется следующим образом. При окончании решения очередной задачи или при другом виде запроса на обмен информацией сигнал о необходимости такого обмена посылается ВМ б на единичный вход триггера 9, который устанавливается в единичное состояние. Кроме того, на регистр 10, от этой же вм поступает код операции обмена: рейена очередная задача, требование ввода-вывода информации, сигналы от системы контроля ВМ и др. Далее сиг нал о наличии запроса с выхода триг гера 9 поступает на управляющий вхо схемы сравнения 12 и через элемент ИЛИ 14 на единичный вход триггера 1 Переход триггера 15 в единичное состояние обеспечивает появление .высокого потенциала на управляющем входе элемента 17, после чего импул сы с выхода генератора 16.тактовых импульсов поступают через элемент 1 на вход счетчика 18. Код с выхода счетчика поступает на вход дешифратора 19 и первые входы схем сравнения 12, на вторые входы которых поступают коды с регистров 11 приоритета (например, порядковый номер ВМ в вычислительной системе). При наличии запроса на обмен с данной ВМ 6 и при достижении на выходе счетчика 18 соответствующего кода на выходе одной из схем сравнения 12 появляется высокий потенциал, который поступает на нулевой вход триггера 9 и Через элемент ИЛИ 21 на нулевой вход триггера 15, а такж на управляющий вход группы элементов и 13, в результате чего через элементы 13 и 22 информация с выход регистров 11 приоритета и регистра состояния 10 поступает на вход упра ляющей ВМ 7. Одновременно с переходом триггера 15 в нулевое состояние прекращается подача счетных импульсов с выхода генератора 16 через элемент 17 на вход счетчика 18. УВМ 7 анализирует принятую информацию и принимает решение об изменении программы работы вычислительной системы, записанной в регистре 1. Для этого УВМ 7 подает разрешающий сигнал на управляющий вход дешифратора 19 (в случае немедленной реакции на требование обмена информацией со стороны ВМ 6) в результате чего обеспечивается оперативная связь ВМ 6 и УВМ 7 чере элементы И 5. в том случае, если немедленный обмен информацией между УВМ 7 и ВМ 6 .по инициативе ВМ 6 нецелесообразен, УВМ 7 подает управ ляющий сигнал на элемент 23, в результате чего информация с выхода элемента 22 через элемент 23 записывается на регистр управления 3. По этому коду в дальнейшем обеспечивается обмен информацией между ВМ 6 и УВМ 7 по инициативе ВМ 6. По ле обслуживания запроса на обмен информацией по инициативе ВМ 6 управляющая вычислительная машина 7 сбрасывает в нулевое (исходное), сос тояние счетчик импульсов 18. Таким образом, устройство диспетчеризации обеспечивает параллельную работу ВМ 6 при гибкой оперативной организации управления, которая достигается за счет исключения потерь машинного времени, связанного с организацией двухстороннего обмена информацией. При этом устройство обеспечивает повышение эффективного быстродействия ЕС при незначительных дополнительных аппаратурных затратах. Указанные качества устройства диспетчеризации вычислительной системы способствуют эффективному его применению при решении совокупности задач управления объектами и технологическими процессами. Формула изобретения Устройство диспетчеризации вычислительной системы, содержащее регистр приращений, коммутатор, регистр управления, первый дешифратор, первый элемент ИЛИ, группу, элементов ИЛИ и N узлов формирования сигналов состояния (N - число управляемых вычислительных машин), содержащих триггер запроса, регистр состояния, регистр приоритета, схему сравнения и группу элементов И, причем вход регистра приращений подключен к входу кода настройки устройства, выход регистра приращений соединен с информационным входом коммутатора, управляющий вход которого подключен к стробирующему входу устройства,выход коммутатора соединен с информационным входом регистра управления, управляющий вход которого подключен к управляющему входу устройства, выход регистра управления соединен со входом первого дешифратора, выход которого является первым выходом устройства, входы регистров состояния соединены с первой группой кодовых входов устройства, единичные входы триггеров запросов являются установочными входами устройства, нулевые входы триггеров запросов соединены с выходами соответствующих схем сравнения, входы регистров iприоритета являются второй группой кодовых входов устройства, выходы регистров приоритета соединены с первыми входами схем сравнения и первыми входами элементов И групп, вторые и управляющие входы которых соединены соответственно с выходами регистров состояния и выходами схем сравнения, а выходы - со входами элементов ИЛИ группы, выходы которых подключены к группе управляющих выходов устройства, выходы триггеров запросов соединены с управляющими входами схем сравнения, входы первого.элемента ИЛИ соединены с выходами триг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство диспетчеризации вычислительной системы | 1982 |

|

SU1068944A1 |

| Вычислительная система | 1979 |

|

SU809194A2 |

| Устройство для сопряжения вычислительных машин и управляющей вычислительной машины | 1984 |

|

SU1257654A1 |

| Устройство для сопряжения управляющей и управляемых вычислительных машин | 1988 |

|

SU1517033A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения к абонентов с М вычислительными машинами | 1987 |

|

SU1411758A1 |

| Устройство для сопряжения | 1982 |

|

SU1038933A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Устройство для обмена информацией | 1978 |

|

SU723560A1 |

Авторы

Даты

1982-08-15—Публикация

1980-03-10—Подача