(54)

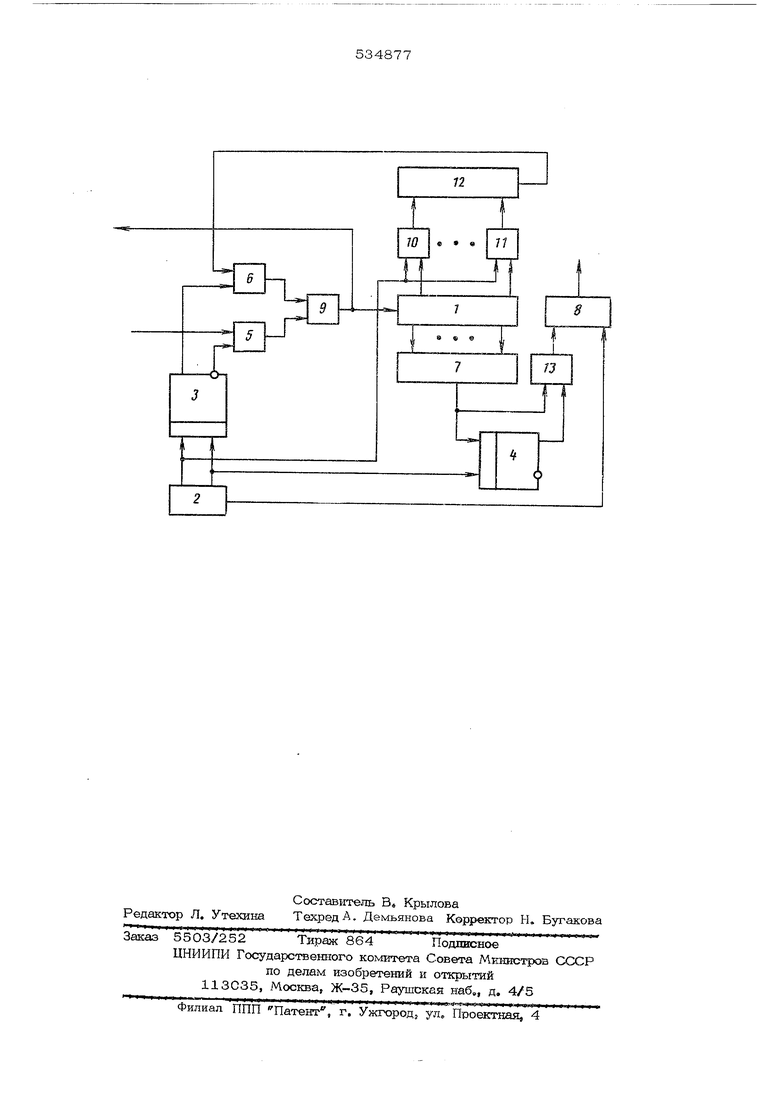

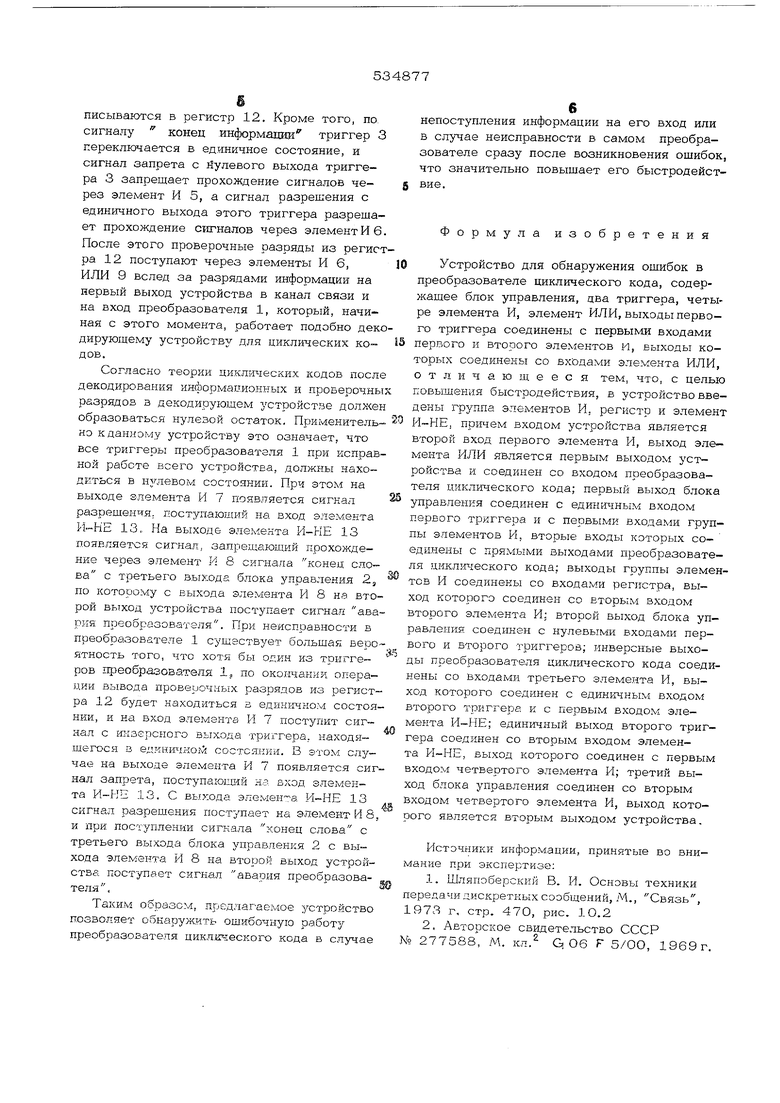

УСТРОЙСТВО для ОБНАРУЖЕНИЯ ОШИБОК В ПРЕОБРАЗОВАТЕЛЕ ИтЛИЧЕСКОГО КОДА вателя циклического кода. Выходы группы элементов И соединены со входами регистра, выход которого соединен со вторым входом второго элемента И, Второй выход блока управления соединен с нулевыми входами первого и второго триггеров. Инверсные вы ходы преобразователя циклического кода со единены со входами третьего элемента И, выход которого соединен с единичным входом второго триггера и с первым входом элемента И-НЕ. Единичный выход второго триггера соединен со вторым входом элемента И-НЕ, выход которого соединен с пе вым входом четвертого элемента И. Третий выход блока управления соединен со вторым входом четвертого элемента И, выход которого является вторым выходом устройства. На чертеже изображена блок-схема устройства для обнаружения ошибок в преобразователе циклического кода. Устройство содержит преобразователь циклического кода 1, блок управления 2, триггеры 3 и 4, элементы И 5-8 и элемент ИЛИ 9. Выходы триггера 3 соединены с первыми входами элементов И 5,6, выходы которых соединены со входами элемен та ИЛИ 9. Кроме того, устройство содержит группу элементов И (на чертеже изображены пер1вый 1О и последний 11 элементы И групы), регистр 12 и элемент И-НЕ 13. Вход устройства (информация от абонента) соединен со вторым входом элемента И 5. Вы ход элемента ИЛИ 9 соединен с первым вы ходом устройства { информация в канал связи) и со входом преобразователя 1, пер вый выход блока управления 2 (конец информации) соединен с единичным входом триггера 3 и с первыми входами группы элементов И, вторые входы которых соединены с прямыми выходами триггеров преобразователя 1. Выходы группы элементов И соедишены со входами регистра 12, выход которого соединен со вторым входом элемента И 6. Второй выход блока управления (начало слова) соединен с нулевыми входами триггеров 3 и 4. Инверсные выходы триггеров преобразователя 1 соединены со входами элемента И 7, выход которого соединен с единичным входом триггера 4 и с первым входом элемента И-НЕ 13. Единичный выход триггера 4 соединен со вторым входом элемента И-НЕ 13, выход кот рого соединен с первым входом элемента И 8. Третий выход блока управления 2 (конец слова) соединен со вторым входом элемента И 8, выход которого соединен со вторым выходом устройства (авария преобразователя). Устройство работает следующим образом. В исходном состоянии триггеры преобразователя 1 и регистра 12 находятся в нулевом состоянии, а триггеры 3,4 - в единичном. Перед поступлением информации от абонента по сигналу начало слова со второго выхода блока управления 2 триггеры 3 и 4 устанавливаются в нулевое состояние. При этом сигнал разрешения с нулевого выхода триггера 3 поступает на элемент И 5, сигнал запрета с единичного выхода триггера 3 - на элемент И 6, а сигнал запрета с единичного выхода триггера 4 - на элемент И-НЕ 13, с выхода которого сигнал разрешения поступает на элемент И 8. Таким образом, состояние устройства после сигнала начало слова таково, что при появлении на входе элемента И 8 сигнала конец слова с третьего выхода блока управления 2 на выходе элемента И 8 сформировался бы сигнал авария преобразователя, поступаюш:ий на второй выход устройства. Но при отсутствии неисправностей во входных цепях и в преобразователе на преобразователь 1 после сигнала начало слова через элементы И 5, ИЛИ 9 начинает поступать информация, которая, кроме того, с выхода элемента ИЛИ 9 аьщается на первый выход устройства в канал связи. При поступлении в преобразователь xo-i тя бы одной единицы информации нулевое состояние по крайней мере двух триггеров преобразователя изменяется на единичное, и на выходе элемента И 7 появляется сигнал, по которому триггер 4- устанавливается в единичное состояние (на чертеже показаны первый и последний входы элемента И 7). С единичного выхода триггера 4 на элемент И-НЕ 13 поступает сигнал разрешения, что является признаком отсутствия неисправности во входных цепях и служит одним из условий для определения исправности преобразователя. В соответствии с теорией циклических кодов после окончания обработки информации в триггерах преобразователя 1 образуются проверочные разряды, при этом с первых прямых выходов триггеров, находящихся в единичном состоянии, на соответствующие входы группы элементов И поступают сигналы разрешения. Число триггеров в преобразователе 1, регистре 12 и число элементов И в группе зависят от степени образующего полинома кода. По сигналу конец информации с первого выхода блока управления 2 проверочные разряды параллельным кодом через соответствующие элементы И группы пере-, писываются в регистр 12, Кроме того, по, сигналу конец .информации триггер 3 переключается в единичное состояние, и сигнал запрета с йулевого выхода триггера 3 запрещает прохождение сигналов через элемент И 5, а сигнал разрешения с единичного выхода этого триггера разрешает прохождение сигналов через элемент И 6 После этого проверочные разряды из регист ра 12 поступают через элементы И 6, ИЛИ 9 вслед за разрядами информации на первый выход устройства в канал связи и на вход преобразователя 1, который, начиная с этого момента, работает подобно деко дирующему устройству для циклических кодов. Согласно теории циклических кодов после декодирования информационных и проверочны разрядов в декодирующем устройстзе должен образоваться нулевой остаток, Применительно к данному устройству это означает, что все триггеры преобразователя 1 при исправ ной работе всего устройства, должны находиться в нулевом состоянии. При этом на выходе элемента И 7 появляется сигнал разрещеняя. лоступаюший на вход элемента 13 „ На выходе элемента И-НЕ 13 появляется сигнал, запрещающий лрохож,цение через элемент Л 8 сигнала конея слова с третьего выхода блока управления 2, по которому с выхода элемента И 8 на вто рой выход устройства поступает сигнал ава рия преобразователя. При неисправности в преобразователе 1 существует большая веро ятность того, что хотя бы один из триггеров преобразователя 1, по окончаний, операции вывода проверочных разрядов из регист ра 12 будет находиться в единично состоя нии, и на вход элемента И 7 поступит сигнал с икаерсного выхода триггера, находящегося в едт ничкогА состоянии. В этом случае на выходе элемента И 7 появляется сиг нал запрета, поступающий на вход элемента И-НЕ 13. С выхода элемен-а И-НЕ 13 сигнал разрещения поступает на элемент И 8 и при поступлении сигнала конец слова с третьего выхода блока управления 2 с выхо,ца элемента И 8 на второй выход устройства поступает сигнал авария преобразователя, Таким образом, предлагаемое устройство позволяет обнаружить ошибочную работу преобразовате,ля циклического кода в случае непоступления информации на его вход или в случае неисправности в самом преобразователе сразу после возникновения ошибок, что значительно повышает его быстродействие. Формула изобретения Устройство для обнаружения ошибок в преобразователе циклического кода, содержащее блок управления, два триггера, четыре элемента И, элемент ИЛИ, выходы первого триггера соединены с первыми входами первого и второго элементов и, выходы которых соединены со входами элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены группа элементов И. регистр и элемент . пргмем входом устройства является второй вход первого элемента И, выход элемента ИЛИ является первым выходом устро,йства и соединен со входом преобразователя циклического кода; первый выход блока управления соединен с единичным входом первого триггера и с первыми входами группы элементов И. вторые входы которых соединены с прЯлМ,ыми выходами преобразователя циклического кода; выходы группы элементов И соединены со входами регистра, выход которого соединен со вторым входом второго элемента И; второй выход блока управления соединен с нулевыми входами первого и второго триггеров; инверсные выходы преобразователя циклического кода соединены со входами третьего элеме,нта И, выход которого соединен с единичным входом второго триггера и с первым входом элемента единичный выход второго триггера соединен со вторым входом элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И; третий выход блока управления соединен со вторым входом четвертого элемента И, выход которого является вторым выходом устройства, Источники информации, принятые во внимание при экспертизе: 1.Шляпоберский В. И. Основы техники передачи д,искретных сообщений. Л., Связь, 1973 г, стр. 470, рис. 1О.2 2.Авторское свидетельство СССР № 277588, М. кл. Q Об Г 5/ОО, 1969г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство кодирования блоков информации | 1984 |

|

SU1302439A1 |

| Устройство для приема информации | 1988 |

|

SU1550562A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Преобразователь напряжения в код | 1979 |

|

SU824433A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для декодирования с исправлением ошибок | 1986 |

|

SU1411981A1 |

Авторы

Даты

1976-11-05—Публикация

1974-12-26—Подача