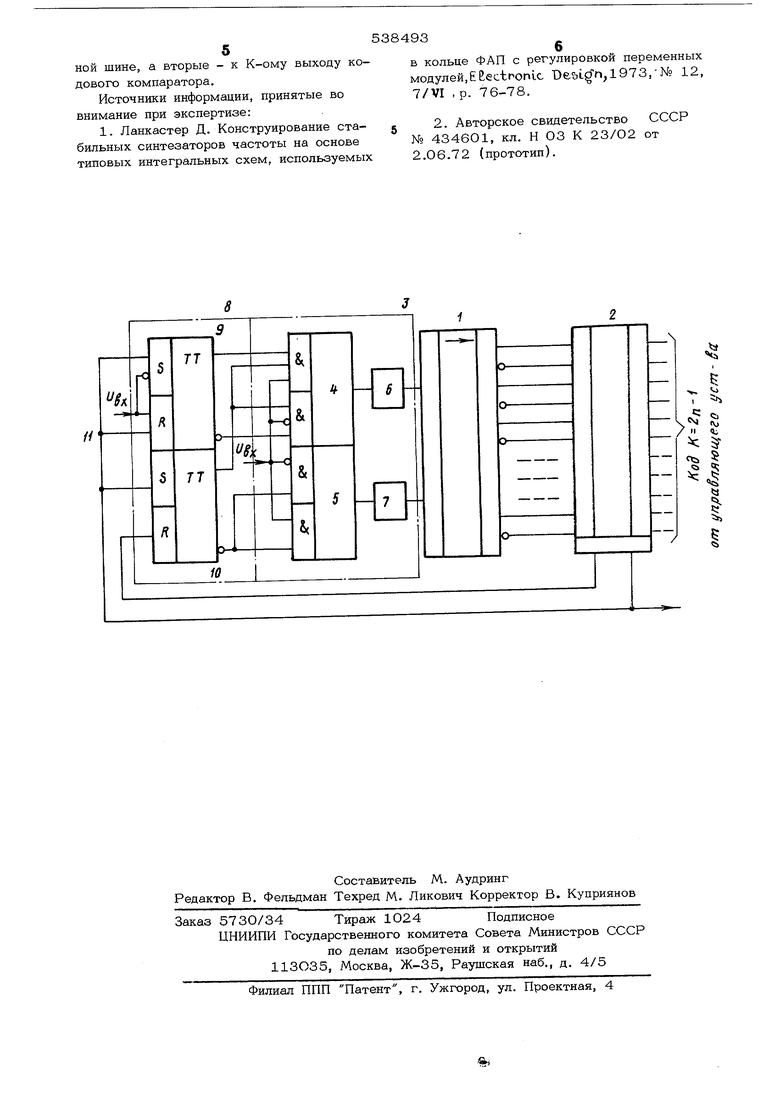

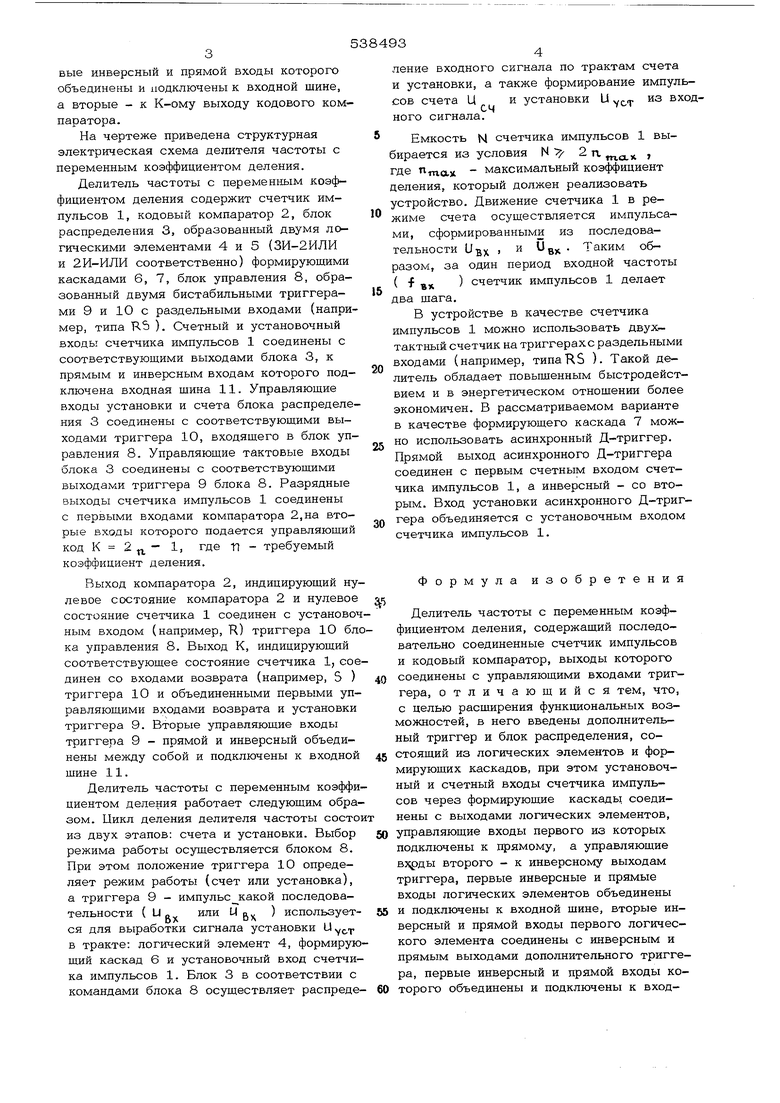

вые инверсный и прямой входы которого объединены и подключены к входной шине, а вторые - к К-ому выходу кодового компаратора. На чертеже приведена структурная электрическая схема делителя частоты с переменным коэффициентом деления. Делитель частоты с переменным коэффициентом деления содержит счетчик импульсов 1, кодовый компаратор 2, блок распределения 3, образованный двумя логическими элементами 4 и 5 (ЗИ-2ИЛИ и 2И-ИЛИ соответственно) формирующими каскадами 6, 7, блок управления 8, образованный двумя бистабильными триггерами 9 и 10 с раздельными входами (например, типа RS ). Счетный и установочный входы счетчика импульсов 1 соединены с соответствующими выходами блока 3, к прямым и инверсным входам которого подключена входная шина 11. Управляюшие входы установки и счета блока распределения 3 соединены с соответствующими выходами триггера 10, входящего в блок управления 8. Управляюшие тактовые входы блока 3 соединены с соответствующими выходами триггера 9 блока 8. Разрядные выходы счетчика импульсов 1 соединены с первыми входами компаратора 2,на вторые входы которого подается управляющий код К 2 - 1, где п - требуемый коэффициент деления. Выход компаратора 2, индипируюший ну левое состояние компаратора 2 и нулевое состояние счетчика 1 соединен с установоч ным входом (например, R) триггера 10 бл ка управления 8. Выход К, индицирующий соответствующее состояние счетчика 1, сое динен со входами возврата (например, 5 ) триггера 10 и объединенными первыми управляющими входами возврата и установки триггера 9. Вторые управляющие входы триггера 9 - прямой и инверсный объединены между собой и подключены к входной щине 11. Делитель частоты с переменным коэффи циентом деления работает следующим образом. Цикл деления делителя частоты состо из двух этапов: счета и установки. Выбор режима работы осуществляется блоком 8. При этом положение триггера 10 определяет режим работы (счет или установка), а триггера 9 - импульс какой последовательности ( U „ или М g ) используется для выработки сигнала установки U в тракте: логический элемент 4, формирую щий каскад 6 и установочный вход счетчика импульсов 1. Блок 3 в соответствии с командами блока 8 осуществляет распреде ление входного сигнала по трактам счета и установки, а также формирование импульи установки И сов счета Ц из входного сигнала. Емкость N счетчика импульсов бирается из условия N 2 тг где Ttniajt - максимальный коэ4)фициент деления, который должен реализовать устройство. Движение счетчика 1 в режиме счета осуществляется импульсами, сформированными из последовательности и, , и OBH Таким образом, за один период входной частоты ( f д ) счетчик импульсов 1 делает два шага. В устройстве в качестве счетчика импульсов 1 можно использовать двухтактный счетчик на триггерахс раздельными входами (например, типаКЗ ). Такой делитель обладает повышенным быстродействием и в энергетическом отношении более экономичен. В рассматриваемом варианте в качестве формирующего каскада 7 можно использовать асинхронный Д-триггер. Прямой выход асинхронного Д-триггера соединен с первым счетным входом счетчика импульсов 1, а инверсный - со вторым. Вход установки асинхронного Д-триггера объединяется с установочным входом счетчика импульсов 1. Формула изобретения Делитель частоты с переменным коэффициентом деления, содержащий последовательно соединенные счетчик импульсов и кодовый компаратор, выходы которого соединены с управляющими входами триггера, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дополнительный триггер и блок распределения, состоящий из логических элементов и формирующих каскадов, при этом установочный и счетный входы счетчика импульсов через формирующие каскады соединены с выходами логических элементов, управляющие входы первого из которых подключены к прямому, а управляющие второго - к инверсному выходам триггера, первые инверсные и прямые входы логических элементов объединены и подключены к входной шине, вторые инверсный и прямой входы первого логического элемента соединены с инверсным и прямым выходами дополнительного триггера, первые инверсный и прямой входы которого объединены и подключены к входной шине, а вторые - к К-ому выходу кодового компаратора.

Источники информации, принятые во внимание при экспертизе:

1. Ланкастер Д. Конструирование стабильных синтезаторов частоты на основе типовых интегральных схем, используемых

в кольце ФАП с регулировкой переменных модулей,Е&ес-Ьгоп1с De&Lgn,1973,-№ 12, 7/VI ,р. 76-78.

2. Авторское свидетельство СССР № 434601, кл. Н 03 К 23/02 от 2.06.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1975 |

|

SU660262A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2093387C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Управляемый умножитель частоты следования импульсов | 1982 |

|

SU1034145A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

Авторы

Даты

1976-12-05—Публикация

1975-11-17—Подача