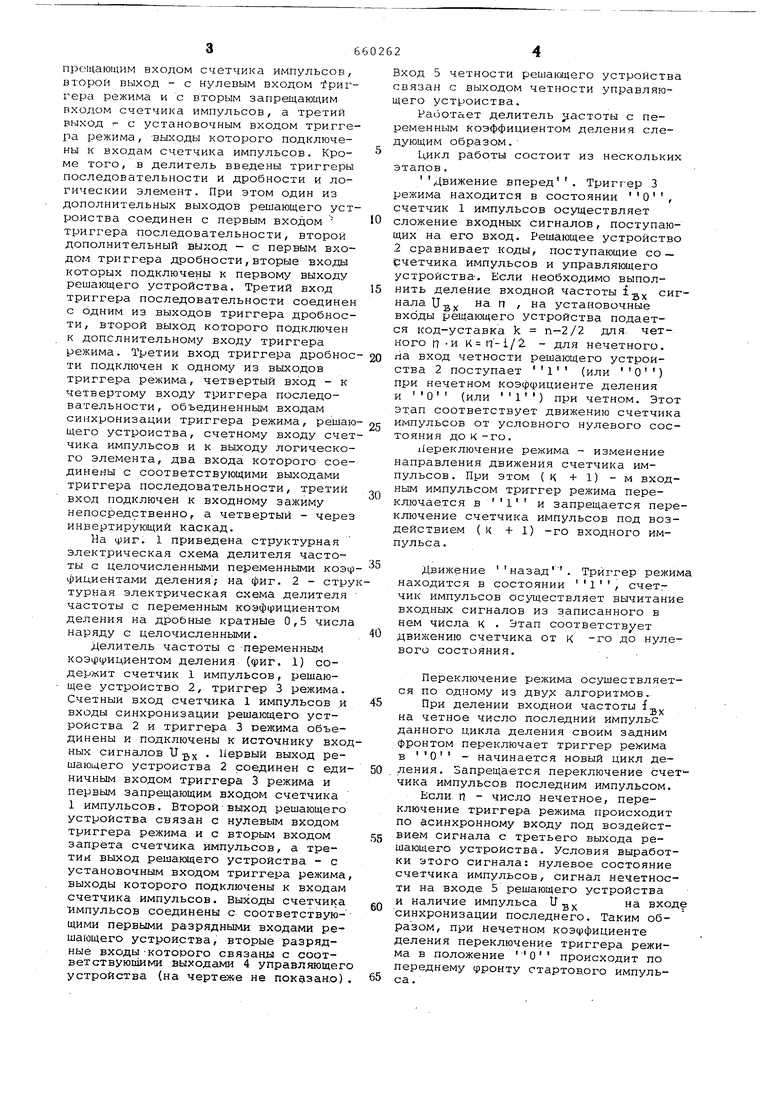

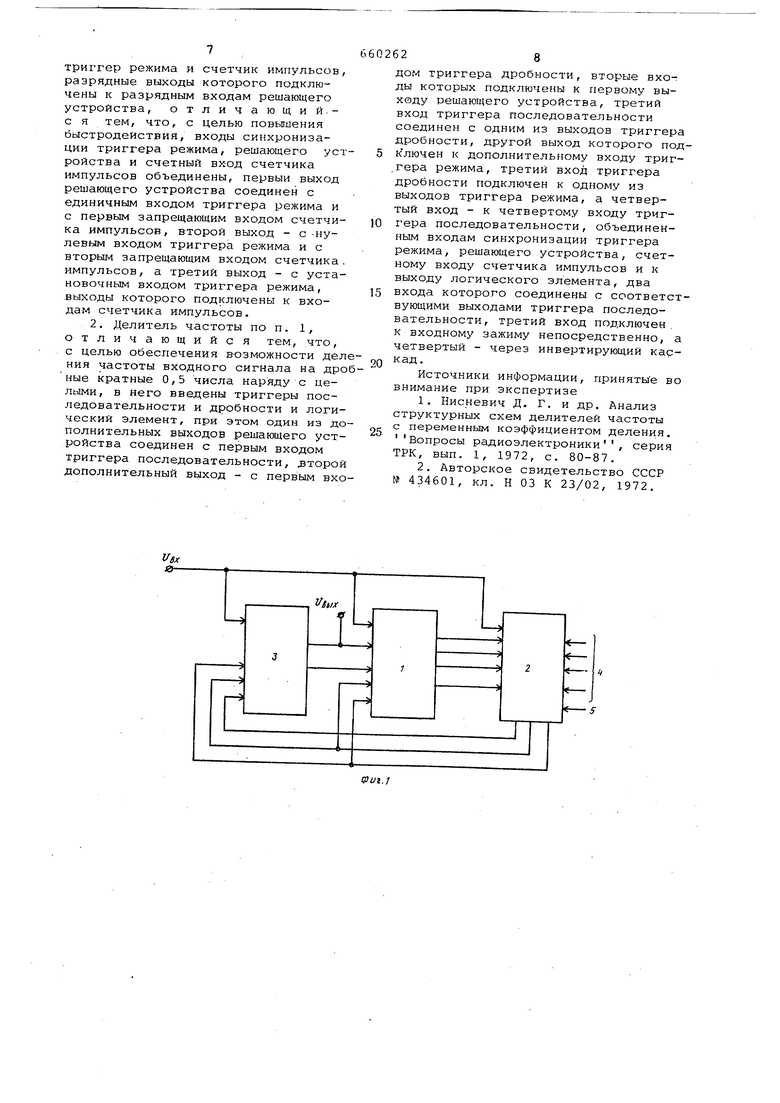

продающим входом счетчика импульсов, второй выход - с нулевым входом триггере режима и с вторым запрещающим входом счетчика импульсов, а третий выход - с установочным входом тригге ра режима, выходы которого подключены к входам счетчика импульсов. Кроме того, в делитель введены триггеры последовательности и дробности и логический элемент. При этом один из дополнительных выходов решающего уст ройства соединен с первым входом триггера -последовательности, второй дополнительный выход - с первым входом триггера дробности,вторые входы которых подключены к первому выходу решающего устройства. Третий вход триггера последовательности соединен с одним из выходов триггера дробности, второй выход которого подключен к дополнительному входу триггера режима. Третий вход триггера дробнос ти подключен к одному из выходов триггера режима, четвертый вх;од - к четвертому входу триггера последовательности, объединенным входам синхронизации триггера режима, решаю щего устройства, счетному входу счет чика импульсов и к выходу логического элемента, два входа которого сое динены с соответствующими выходами триггера последовательности, третий вход подключен к входному зажиму непосредственно, а четвертый - чере инвертирующий каскад. На ч)иг. 1 приведена структурная электрическая схема делителя частоты с целочисленными переменными коэ фициентами деления; на фиг. 2 - стр турная электрическая схема делителя частоты с переменным коэффициентом деления на дробные кратные 0,5 числ наряду с целочисленными. Делитель частоты с переменным коэффициентом деления (фиг. 1) содержит счетчик 1 импульсов, решающее устройство 2, триггер 3 режима. Счетный вход счетчика 1 импульсов и входы синхронизации решающего уст роиства 2 и триггера 3 режима объединены и подключены к источнику вхо ных сигналов U;g,x Первый выгсод решающего устройства 2 соединен с еди ничным входом триггера 3 режима и первым запрещающим входом счетчика 1 импульсов. Второйвыход решающего устройства связан с нулевым входом триггера режима и с вторым входом запрета счетчика импульсов, а третий выход решающего устройства - с установочным входом триггера режима выходы которого подключены к входам счетчика импульсов. Выходы счетчика импульсов соединены с соответствующими первыми разрядными входами решающего устройства, вторые разрядные входы КОТОРОГО связаны с соответствующими выходами 4 управляющег устройства (на чертеже не показано) ход 5 четности решающего устройства вязан с выходом четности управляюего устройства. Раоотьет делитель у.аст:О1ы с пееменным коэффициентом деления слеующим образом. Цикл работы состоит из нескольких тапов. Движение вперед . Триггер 3 ежима находится в состоянии четчик 1 импульсов осуществляет ложение входных сигналов, поступаюих на его вход. Решающее устройство сравнивает коды, поступающие со - :четчика импульсов и управляющего устройства . Если необходимо выполнить деление входной частоты i-g, сигнала Ugj на п , на установочные входы рещающего устройства подается код-уставка k п-2/2 для, четного п-иК п-1/2 - для нечетного. ria вход четности решающего устройства 2 поступает (или О) при нечетном коэффициенте деления и О (или ) при четном. Этот этап соответствует движению счетчика импульсов от условного нулевого состояния до К-го. х ереключение режима - изменение направления движения счетчика импульсов. При этом (К +1) - м входным импульсом триггер режима переключается в и запрещается переключение счетчика импульсов под воздействием (к +1) -го входного импульса. Движение назад . Триггер режима находится в состоянии , счетчик импульсов осуществляет вычитание входных сигналов из записанного в нем числа к . Этап соответствует движению счетчика от к -го до нулевого состояния. Переключение режима осуществляется по одному из двух алгоритмов. При делении входной частоты i. на четное число последний импульс данного цикла деления своим задним фронтом переключает триггер режима в О - начинается новый цикл деления. Запрещается переключение счетчика импульсов последним импульсом. Если, п - число нечетное, переключение триггера режима происходит по асинхронному входу под воздействием сигнала с третьего выхода решающего устройства. Условия выработки этого сигнала: нулевое состояние счетчика импульсов, сигнал нечетности на входе 5 решающего устройства и наличие импульса вход синхронизации последнего. Таким образом, при нечетном коэффициенте деления переключение триггера режима в положение О происходит по переднему фронту стартов.ого импульса. Отличие делителя частоты с перем ным коэффициентом деления, схема ко торого представлена на фиг. 2, от устройства на фиг. 1 заключается в том, что в него дополнительно введены триггеры последовательности 6 и дробности 7, логический элемент 8 и инвертирующий каскад 9. Счетный вход счетчика 1 импульсов и входы синхронизации решающего устройства 2, триггеров режима 3, последователь ности 6 и дробнос ги / объединены и подключены к выходу логического элемента 8. Два входа логического элемента 8 соединены с соответствую щими выходами триггера последовател ности, третий вход подключен к вход ному зажиму непосредственно, а четвертый - через инвертирующий каскад 9. Один из дополнительных выходов решающего устройства 2 соединен с п вым входом триггера 6 последователь ности, второй дополнительный выход с первым входом триггера 7 дробности, вторые входы которых подключены к первому выходу решающего устройства 2. Третий вход триггера пос ледовательности подсоединен к одному из выходов триггера дробности, другой выход которого подключен к дополнительному входу триггера режима. Третий вход триггера дробности подсоединен к одному из выхсздов триггера режима, а четвертый вход - к четвертому входу триггера последовательности, объединенным входам синхронизации триггера режима, рещающего устройства, счетному входу счетчика импульсов и к выходу логического элемента 8. К дополнительному входу 10 (входу дробности) решающего устройства 2 подключен выход признака дробности упр ляющего устройства. Делитель частоты с переменным коэффициентом деления работает следующим образом. Для целочисленных п сигналов со второго дополнительного выхода решагацего устройства триггеры последо вательности 6 и дробности 7 блокируются в состоянии, при котором они не оказывают влияния на работу устр ства в целом. Цикл работы делителя состоит из тех же четырех тактов, которые описаны при рассмотрении схемы фиг. 1. При делений частоты на дробное число с четной целой частью на вхо ды четности 5 и дробности 10 решающего устройства 2 подаются соответс вующие сигналы. Асинхронные входы триггеров последовательности 6 и дробности 7 не возбуждаются. Управление триггерами осуществляется до синхронным входам. При этом триггер 6 последовательности переключается в противоположное состояние при уст новке счетчика 1 импульсов в условное нулевое состояние и состояние О триггера 7 дробности. Триггер дробности устанавливается в i при нулевом состоянии счетчика импульсов при нулевом состоянии триггера режима. Триггер режима устанавлипри одних и тех же вается в условиях для произвольных п под действием (к +1) -го входного импульса. Запрещается переключение счетчика импульсов под воздействием (К + 1)-го входного импульса. Переключение триггера режима в происходит при единичном состоянии триггера дробности и нулевом состоянии счетчика импульсов. В зависимости от состояния триггера 6 последовательности на вход синхронизации поступает либо последовательность, находящаяся в фазе с Ugx последовательность iJ , находящаяся в противофазе к U-g .Триггер последовательности переключается один раз за цикл деления. Благодаря этому после каждого цикла деления происходи смена последовательности U-gj БХ (или наоборот), т. е. сдвиг на половину периода момента переключения в О триггера режима. Такой порядок переключениях,.и необходим для деления частоты f сигнала U-зх на дробное число, кратное 0,5 с четной целой частью. При делении входной частоты на дробные числа с нечетной целой частью возбуждается выход асинхронной установки триггера дробности, блокируя его, триггеры режима и последовательности работают в синхронном режиме. При этом триггер последовательности переключается в противоположное положение, а триггер режима устанавливается в О при установке в счетчика импульсов, Триггер 1 после режима переключается в установки в К -е состояние счетчика импульсов. Как и в предыдущем случае в схеме, после каждого цикла деления происходит смена последовательности II 5х ЪК. наоборот) . Быстродействие описанных устройств повышается благодаря отсутствию в них принудительной установки в исходное состояние счетчика импульсов в конце каждого цикла деления. Кроме того, делитель частоты, изображенный на фиг. 2, обладает повышенными функциональными характеристиками, которые заключаются в реализации в одном устройстве возможности деления частоты как на целые числа, так и на дробные кратные 0,5 при регулярном характере выходного колебания. Формула изобретения 1. .Делитель частоты с переменным коэффициентом деления, содержащий

7

триггер режима и счетчик импульсов, разрядные выходы которого подключены к разрядным входам решающего устройства, отличающий-с я тем, что, с целью повыиения быстродействия, входы синхронизации триггера режима, решающего устройства и счетный вход счетчика импульсов объединены, первый выход решающего устройства соединен с единичным входом триггера режима и с первым запрещающим входом счетчика импульсов, второй выход - с -нулевым входом триггера режима и с вторым запрещающим входом счетчика . импульсов, а третий выход - с установочным входом триггера режима, выходы которого подключены к входам счетчика импульсов,

2. Делитель частоты по п. 1, отличающийся тем, что, с целью обеспечения возможности делния частоты входного сигнала на дроные кратные 0,5 числа наряду с целыми, в него введены триггеры последовательности и дробности и логический элемент, при этом один из дополнительных выходов решающего устройства соединен с первым входом триггера последовательности, дзторой дополнительный выход - с первым вхо02628

дом триггера дробности, вторые входы которых подключены к первому выходу решающего устройства, третий вход триггера последовательности соединен с одним из выходов триггера дробности, другой выход которого под5 ключен к дополнительному входу триггера режима, третий вход триггера дробности подключен к одному из выходов триггера режима, а четвертый вход - к четвертому входу триггера последовательности, объединенным входам синхронизации триггера режима, решающего устройства, счетному входу счетчика импульсов и к выходу логического элемента, два входа которого соединены с соответствующими выходами триггера последовательности, третий вход подключен, к входному зажиму непосредственно, а четвертый - через инвертирующий каскад.

Источники информации, принятые во внимание при экспертизе

1. Нисневич Д. Г. и др. Анализ структурных схем делителей частоты с переменным коэффициентом деления.

Вопросы радиоэлектроники

серия

ТРК, вып. 1, 1972, с. 80-87.

2. Авторское свидетельство СССР № 434601, кл. Н 03 К 23/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1669079A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Управляемый делитель частоты | 1981 |

|

SU982200A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Измеритель динамических характеристик | 1987 |

|

SU1532901A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

Авторы

Даты

1979-04-30—Публикация

1975-12-15—Подача