(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ

первый йыход - го вторым управляющим входом ключа, а второй выход через первый коммутатор - со вторым входом делителя опорной частоты и через дополнительный запоминающий регистр и второй коммутатор, которые соединены последовательно с сигнальным входом ключа, при этом вторые входы коммутаторов объединены и под ;лючбны к выходу дополнительного делителя опорной частоты, подключенного к вьшодам источника шорной .частоты, а установочный вход дополнительного запоминающего регистра соединен со вторым выходом блока управления.

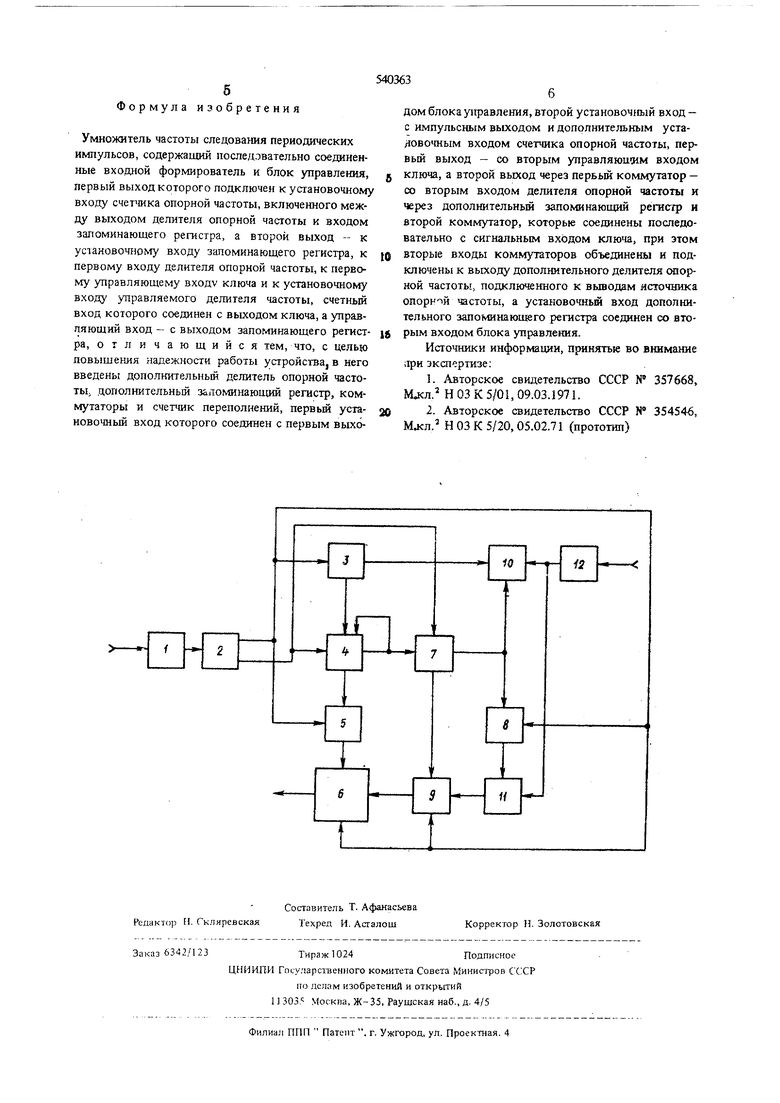

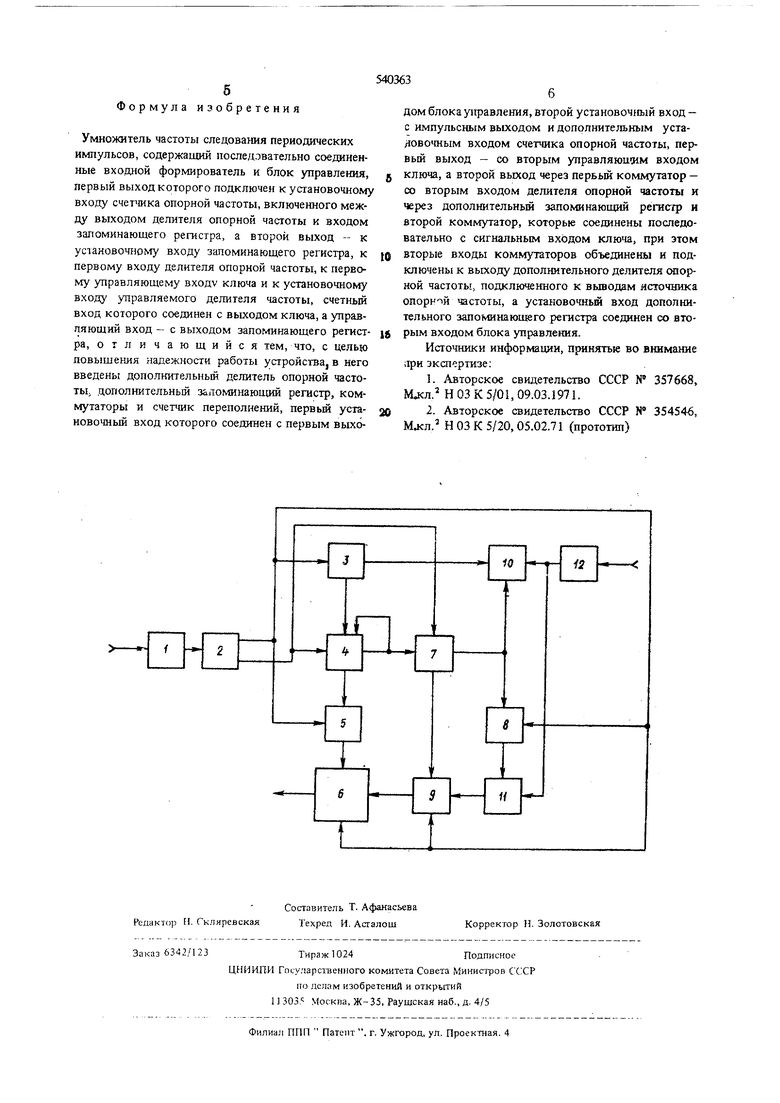

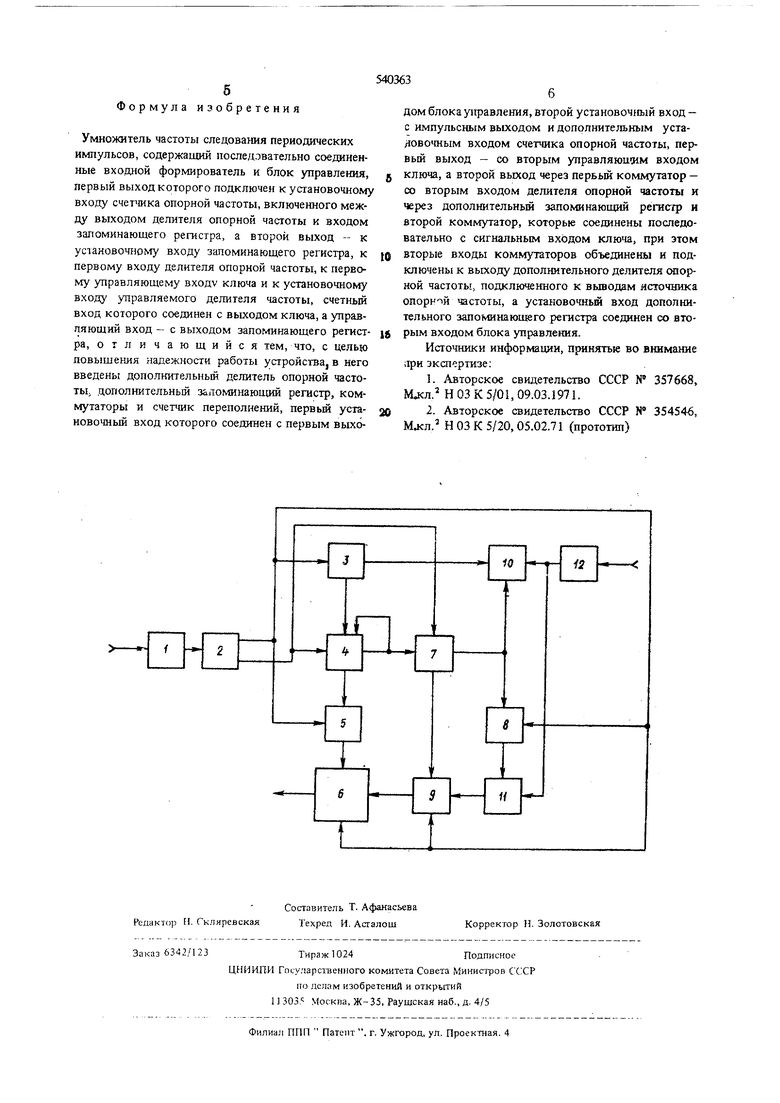

На чертеже представлена структурная электри ческая схема умножителя частоты следования периодических импульсов.

Устройство содержит входной формирователь 1, блок 2 управления, делитель 3 опорной частоты с коэффициентом деления, равным коэффициенту умножения К. счетчик 4 импульсов опорной частоты, запоминающий регистр 5, управляемый делитель 6 счетно-импульсного типа, счетчик 7 шсла переполнений, дополнительный запоминающий регистр 8 числа переполнений, ключ 9, коммутаторы 10 и 11 опорных частот, дополнительный делитель 12 опорной частоты fo с п выходами, связанными с соответствующими п одноименными входами каждого из коммутаторов 10 и 11. Последние управляются счетчиком 7 л запоминающим регистром 8 так, что при числе переполнений на выходы коммутаторов 10 и 11 поступает частота fot при р 1в а раз меньщая частота, при р 2-частота fo/a и т. д. Емкости счетчика 7 и заполшнающего регистра 8 равны соответственно п--1, а емкость N счетчика 4 равна fo/K-f ax, где fmax -максимальное значение умножаемой частоты. Управляемый делитель 6 может быть вьтопнен, например, на базе счетчика со схемой сравнения кодов, на базе вычи тающего счетчика или в виде любого другого известного делителя, управляемого кодом так, что его коэффициент деления равен числу передаваемого зтим кодом. Ключ 9 представляет собой клапан, управляемый триггером, нулевой и единичный входы которого представляют собой управляющие входы ключа.

Устройство работает следующим образом.

Предположим, что число, зафиксированное в счетчике 7 и в запоминающем регистре 8 равно нулю. Импульсы опорной частоты fo с выхода коммутатора 10 поступают на вход делителя 3, коэффициент деления которого равен заданному коэффициенту умножения к, а с выхода коммутатора 11 на сигнальный вход ключа 9. Выходаые импульсы делителя 3, частота которых равна fo/K, подаются на вход счетчика 4. Если значение входной частоты f больше f max/a, то счетчик 4 не переполияется и перед приходом очередного импульса умножаемой частоты в нем фиксируется число т, равное fo/Kf. С приходом очередного импульса умножаемой частоты, поступающего на входной формирователь 1 и далее в блок 2, F нулевое положение

устанавливаются делитель 3, управляемый делитель 6, ключ 9 разблокируется в запоминающш регистр 5 записывается число т, зафиксированное в счетчике 4, а в запоминающий регистр 8-число , зафиксированное в счетчике 7. Затем счетчики 4 и 7 устанавливаются в исходное нулевое состояние.

Импульсы опорной частоты fo с выхода коммутатора 11 через разблокированный ключ 9 поступают на счетный вход управляемого делителя 6, коэффициент деления которого равен числу т, написанному в запоминающий регистр 5. Следовательно, чистота ммпульсов на выходе управляемого делителя 6 равнаf

, - zKf

I-Bbl

Допустим теперь, что значение умножаемой истоты лежит в пределах f max/a max/a Тогда ещ до прихода очередного импульса умножаемой частоты счетчик 4 переполнится. В момент йереполнения импульс с выхода счетчика 4 поступает на его дополнительный установочнй вход, и в счетчике 4 фиксируется число, равное N/a. Одновременно этот же импульс постзшает в счетчик 7 и в последнем будет зафиксировано число . Соответственно коду счетчика 7 коммутатор 10 переключается и на его выход поступает в а раз меньщее значение опорной частоты, т.е. начиная с момента переполнения счетчика 4, на его вход поступает также ч а раз меньщая опорная частота, равная fo/K-a. Перед приходом очередного импульса умножа мой частоты в счетчике 4 фиксируется число т, равное af. Аналогично описанному выше с приходом очередного импульса умножаемой частоты в запоминаюйцга регистр 5 запишется число т, равное fo/K «af, а в запоминающий регистр 8 - число, равное единице. Соответственно коду запоминающего регистра 8 коммутатор 11 переключается и на его выход поступает также в а раз меньше значение опорной частоты (fo/a). В результате частота импульсов на выходе управляемого делителя 6 равна

ВЧ1Х

К-

В общем случае при значениях умножаемой частоты frnax f fmax/ac4eT4HK 4 переполняется р раз, а частота импульсов на выходе управляемого делителя b равня±

- Kf

вых

При нулевом значе ши параметра входной частоты счетчик 7 после прихода на его вход с выхода счетчика 4 п-го импульса переполнения сформирует на своем выходе импульс.Этот импульс ггос.утшет па второй управляющий вход ключа 9 и блокирует последний, в результате чего нрекращаегся вы)Х1ботка импульсов Bbixo/.yjopi шсюты. Таким оПразом, при iiy;reDOM значении параметра )дной частоты величина выходной частоть также равна нулю.

Формула изобретения

Умножитель частоты следования периодических импульсов, содержащий последовательно соединенные входной формирователь и блок управления, первый выход которого подключен к установочному входу счетчика опорной частоты, включенного между выходом делителя опорной частоты и входом запоминающего регастра, а второй выход к установочному входу запоминающего регистра, к первому входу делителя опорной частоты, к первому управляющему входу ключа и к установочному входу управляемого делителя частоты, счетный вход которого соединен с выходом ключа, а управляющий вход - с выходом запоминающего регистра, отличающийся тем, что, с целью повыщения надежности работы устройства, в него введены дополнительньш делитель опорной тастоТЫ; дополнительный заломинающий регистр, коммутаторы и счетчик переполнений, первый установочный вход которого соединен с первым выходом блока управления, второй установоч{1ый вход - с импульсным выходом и дополнительным уста/1ОВОЧНЫМ входом счетчика опорной частоты, первый выход - со вторым управляюи им входом

ключа, а второй выход через первый коммутатор со вторым входом делителя опорной частоты и через дополнительный запоминающий регисгр и второй коммутатор, которые соединены последовательно с сигнальным входом ключа, при этом

вторые входы коммутаторов объединены и подключены к выходу дополнительного делителя сшорной частоты, подключенного к выводам источника опорной частоты, а установочный вход дополнительного запоминакяцего регистра соединен со вторым входом блока управления.

Источники информации, принятые во внимание ;1ри экспертизе:

. Авторское свидетельство СССР № 357668, Нз:л. Н 03 К 5/01, 09.03.1971.

2. Авторское свидетельство СССР N 354546,

Мжл. Н 03 К 5/20,05.02.71 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1980 |

|

SU945962A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Умножитель частоты следования им-пульСОВ | 1979 |

|

SU839031A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1072755A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| Цифровой термометр | 1987 |

|

SU1673879A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

Авторы

Даты

1976-12-25—Публикация

1976-01-06—Подача