1

Изобретение относится к импульсной технике и предназначено для технической диагностики машин, в част-. ности для формирования фазовых отметок при измерении фазовых характеристик различных процессов, сопровождающих работу объекта диагностирования.

Для квантования цикла работы объекта фазовыми отметками может быть .использован умножитель частоты, еели на вход последнего подать сигнал с периодом, равным или кратным циклу (например, сигнал с датчика частоты вращения). Особенностью таких объектов диагностирования, как двига тёль внутреннего сгорания, является неравномерность вращения коленчатого вала (по углу поворота которого, относительно опорного момента отсчитываются фазовые параметры), которая достигает 2% и более в зависимости от нагрузки. Возникающая при этом флуктуация частоты импульсов на выходе датчика частоты вращения является источником погрешности формирования фазовых отметок и/ следовательно, увеличивает погрешность измерения фазовых характеристик процессов. В связи с этим воэникае задача обеспечения постоянстзва текущего знача-.

ния коэффициента умножения (количества импульсов выходной частоты на данном периоде входной) умножителя при наличии флуктуации частоты на его входе.

Известно устройство умножения частоты следования периодических импульсов, содержащее два счетчика, источник импульсов опорной частоты, запоминающий регистр, сравнивающее устройство, делитель опорной частоты, формирователь, триггер, клапан, дополнительное сравнивающее устройство и блок управления l.

Недостатком этого устройства является изменение текущего значения коэффициента умножения при флуктуации умножаемой частоты.

. Известен умножитель частоты следования импульсов,- содержащий делитель опорной частоты с коэффициентом деления, равным коэффициенту умножения, счетчик импульсов, счетчик импульсов опорной частоты, входной и выходной формирователи, запоми.нающий регистр и блок управления L2JНедостатком данного устройства также является изменение текущего значения коэффициента умножения при флуктуации умножаемой частоты.

Наиболее близким по технической сущности к изобретению является умножитель частоты следования импульсов, содержащий делитель опорной частоты, два счетчика импульсов, входной и выходной формирователи импульсов, запоминающий регистр, сравнивающее устройство и блок управления, причем вход устройства соединен с входом входного формирователя, выход которого подключен к входу блока управления, выход блока управления соединен со вторым входом первого счетчика импульсов, первый вход которого соединен с выходом делителя опорной частоты, а выход - с первым входом запоминающего регистра, выход запоминающего регистра подключен к первому входу сравнивающего устрой.ства, второй вход которого соединен с выходом второго счетчика импульсов, а выход - с. входом выходного формирователя, выход выходного формирователя подключен к выходу устройства и к третьему входу второго счетчика, импульсов, первый. вход второго счетчика импульса соединен с первь1М входом делителя опорной частоты, второй выход блока управления соединен со вторыми входами делителя опорной частоты, запоминающего регистра и второго счетчика импульсов з.

Однако данное устройство также характеризуется изменением текущего значения коэффициента умножения при флуктуации умножаемой частоты.

Цель изобретения - обеспечение постоянства значения коэффициента умножения умножителя при флуктуации умножаемой частоты,

.Поставленная цель достигается тем, что в умножитель, содержащий делитель опорной частоты, два счетчика импульсов, входной и выходной . формировате/1и импульсов, запоминающий регистр, блок сравнения и блок управления, причем вход устройства соединен с входом входного формирователя импульсов, выход которого подключенк входу блока управления, первый выход которого соединен с первым входом первого счетчика импульсов, второй вход которого соединен с выходом делителя опорной частоты, а выход - с первым входом запоминающего регистра, выход запоминающего регистра подключен к первому входу блока сравнения, второй вход которого соединен с выходом второго счетчика импульсов, а выход с входом выходного формирователя импульсов, первый вход второго счетчика импульсов соединен с первым входом делителя опорной частоты, второй выход блока управления соединен со вторыми входами делителя опорной частоты и запоминающего регистра, введены вычитающий счетчик

импульсов, регистр, два элемента И, ва элемента ИЛИ, третий счетчик импульсов .и дополнительный формирователь импульсов, при этом первый вход вычитающего счетчика импульсов соединен с выходом делителя опорной частоты, второй вход - с выходом первого счетчика импульсов, третий вход - с вторым выходом блока управления и первым входом первого элемента ИЛИ, второй вход которого подключен к выходу выходного формирователя импульсов и первому входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, а выход первого элемента ИЛИ подключен к второму входу второго счетчика импульсов, третий вход которого соединен с выходом регистра, первый вход которого подключен к выходу вычитающего счетчика импульсов, а. второй - к третьему выходу блока управления, второй вход второго элемента ИЛИ подключен к выходу второго элемента И, первый вход которого соединен с первым входом делителя опорной частоты, а второй с четвертым выходом блока управления, выход второго элемента ИЛИ подключен к выходу умножителя и к первому, входу третьего счетчика импульсов, второй вход которого соединен с выходом входного формирователя импульсов, а выход через дополнительный формирователь импульсов подключен к второму входу блока управления, пятый выход которого соединен с вторым Входом первого элемента И.

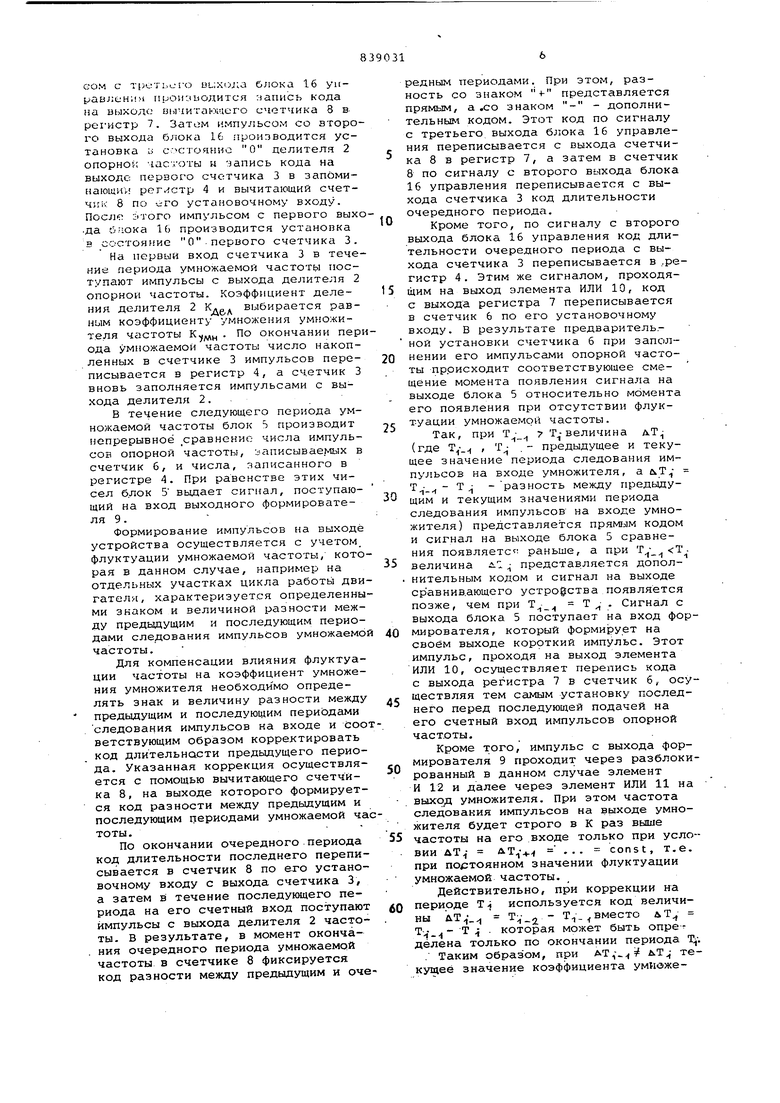

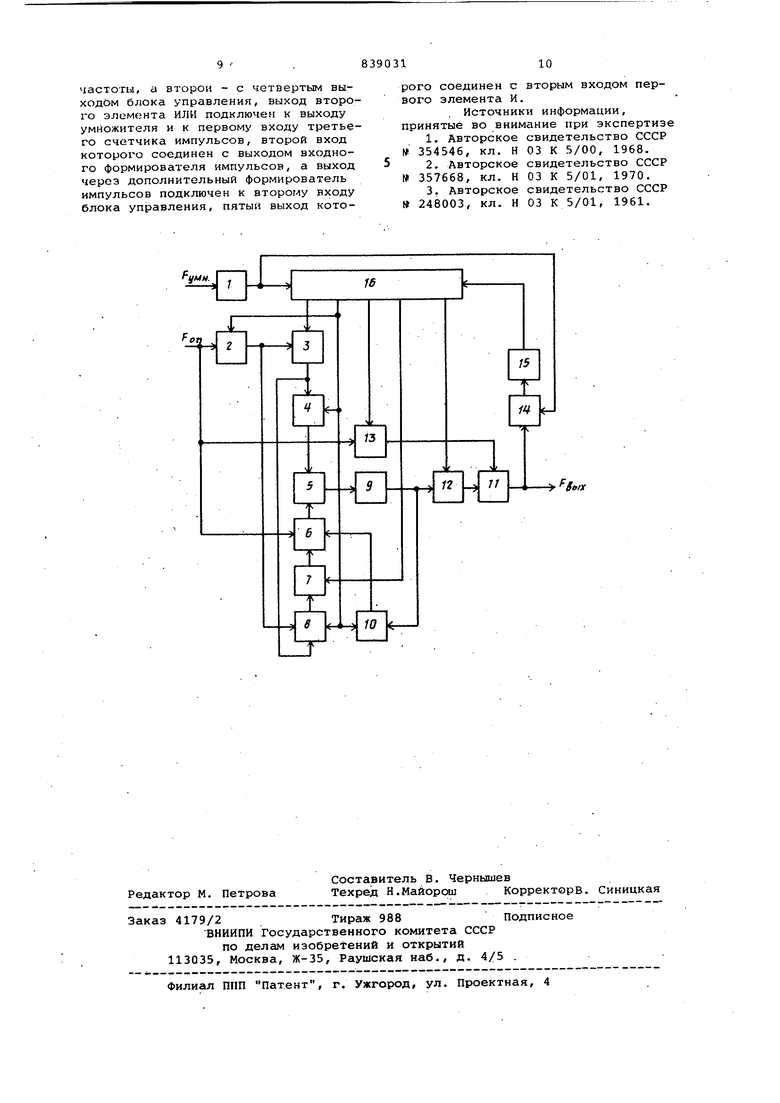

На чертеже представлена структурная электрическая схема предлагаеого умножителя частоты следования импульсов.

Умножитель частоты содержит входной формирователь 1 импульсов, делитель. 2 опорной частоты, первый счётчик 3 импульсов (поделенной опорной частоты), запоминающий регистр 4, блок 5 сравнения, второй счетчик 6 импульсов (опорной частоты), регистр 7, вычитающий счетчик 8 импульсов, выходной формирователь 9 ИМПУЛЬСОВ, первый и второй элементы ИЛИ 10 и 11, первый и второй эле-, енты И 12 и 13, третий счетчик импульсов 14, формирователь 15 импульсов, блок 16 уйравления.

Умножитель ч-астоты работает слеующим образом.

Сигнал умножаемой частоты посту- пает на вход формирователя 1, который преобразует его в прямоугольные импульсы той же частоты. Импульсы выхода формирователя 1 поступают на первый вход блока 16 управления, который по переднему фронту каждого . ходного импульса формирует на сво- . х третьем, втором и первом выхоах последовательно три коротких мпульса управления. Сначала импульGOM С Третьего BLixojia блока 16 управления пронуиодится запись кода ia выходе вычитаьхиего счетчика 8 вpeincTp 7. Затем импульсом со второ го выхода блока 16 производится установка и состояние О делителя 2 опорной часготы н запись кода на выходе первого счетчика 3 в запоминающий реглстр 4 и вычитающий счет4S iv 8 по его установочному входу. После этого импульсом с первого вых .да баока 16 производится установка в состояние О первого счетчика 3. На первый вход счетчика 3 в тече ние периода умножаемой частоту поступают импульсы с выхода делителя 2 опорнои частоты. Коэффициент деления делителя 2 выбирается равным коэффициенту умножения умножителя частоты . По окончании пер ода умножаемой частоты число накопленных в счетчике 3 импульсов переписывается в регистр 4, а счетчик 3 вновь заполняется импульсами с выхода делителя 2. В течение следующего периода умножаемой частоты блок 5 производит непрерывное сравнение числа импульсов опорной частоты, записываемых в счетчик б, и числа, записанного в регистре 4. При равенстве этих чисел блок 5 выдает сигнал, поступающий на вход выходного формирователя 9 . Формирование импульсов на выходе устройства осуществляется с учетом, флуктуации умножаемой частоты, кото рая в данном случае, например на отдельных участках цикла работы дви гатели, характеризуется определенны ми знаком и величиной разности между предьщущим и последующим периодами следования импульсов умножаемо частоты. Для компенсации влияния флуктуации частоты на коэффициент умножения умножителя необходимо определять знак и величину разности между предыдущим и последующим периодами следования импульсов на входе и соо ветствующим образом корректировать код длительнасти предьщущего периода. Указанная коррекция осуществляется с помощью вычитающего счетчика 8, на выходе которого формируется код разности между предыдущим и последующим периодами умножаемой ча тоты. По окончании очередного периода код длительности последнего переписывается в счетчик В по его установочному входу с выхода счетчика 3, а затем в течение последующего периода на его счетный вход поступают импульсы с выхода делителя 2 частоты. В результате, в момент окончания очередного периода умножаемой частоты в счетчике 8 фиксируется код разности между предыдущим и оче редным периодами. При этом, разность со знаком +- представляется прямым, а .со знаком - - дополнительным кодом. Этот код по сигналу с третьего выхода блока 16 управления переписывается с выхода счетчика 8 в регистр 7, а затем в счетчик 8 по сигналу с второго выхода блока 16 управления переписывается с выхода счетчика 3 код длительности очередного периода. Кроме того, по сигналу с второго выхода блока 16 управления код длительности очередного периода с выхода счетчика 3 переписывается в .регистр 4. Этим же сигналом, проходящим на выход элемента ИЛИ 10, код с выхода регистра 7 переписывается в счетчик 6 по его установочному входу. В результате предварительной установки счетчика б при заполнении его импульсами опорной частоты происходит соответствующее смещение момента появления сигнала на выходе блока 5 относительно момента его появления при отсутствии флуктуации умножаемой частоты. Так, при 7 Т -величина дТ (где Т. , .- предыдущее и текущее значение периода следования импульсов на входе умножителя, а CkT . - Т -разность между предыдущим и текущим значениями периода следования импульсов на входе умножителя) представляется прямым кодом и сигнал на выходе блока 5 сравнения появляется: раньше, а при . величина л.1 представляется дополнительным кодом и сигнал на выходе сравнив.ающего устройства появляется позже, чем при Т Т - . Сигнал с выхода блока 5 поступает на вход формирователя, который формирует на своём выходе коррткий импульс. Этот импульс, проходя на выход элемента ИЛИ 10, осуществляет перепись кода с выхода регистра 7 в счетчик б, осуществляя тем Сс1мым установку последнего перед последующей подачей на его счетный вход импульсов опорной частоты. Кроме того, импульс с выхода Формирователя 9 проходит через разблокированный в данном случае элемент И 12 и далее через элемент ИЛИ 11 на выход умножителя. При этом частота следования импульсов на выходе умножителя будет строго в К раз выше частоты на его входе только при условии . . . . -- const, т.е. при постоянном значении флуктуации умножаемой частоты. Действительно, при коррекции на периоде Т используется код величины Т, вместо которая может быть опреTv,-.- Т делена только по окончании периода Tj-. . Таким образом, при АТ, л. текущее значение коэффициента умиожения умножителя отклоняется от номинального, однако это отклонение коэффициента умножения является величиной высшего порядка малости по ср нению с отклонением его, вызванным флуктуацией умножаемой частоты (при отсутствии описанной коррекции). Для коррекции коэффициента умножения используется третий счетчик 14, на счетный вход которого поступ ют импульсы выходной частоты. С началом очередного периода умножаемой частоты счетчик 14 по заднему фронту импульса на выходе формирователя 1 устанавливается в исходное состоя ние - в счетчик записывается дополнительный код числа, равного коэффи циенту умножения умножителя. Затем в течение очередного периода умножа мой частоты- в счетчике 14 осуществляется счет импульсов выходной частоты. При этом в момент поступления на его вход (выход умножителя) К импул сов на выходе старшего разряда счет чика 14 появляется сигнал перепол-нения, поступаквдий на вход формирователя 15, который формирует на сво ем выходе короткий импульс. Импульс с выхода формирователя 15 поступает на второй вход блока 16 управления. Если текущее значение коэффициента умножения больше номинального, то импульс с выхода формирователя 15 поступает на второй вхдд блока 16 управления раньше импульса с выхода формирователя 1, который поступает на первый вход блока 16 управления. По переднему фронту импульса на втором .входе блок 16 управления формирует на своем пятом Bbixojoie сигнал, блокирующий элемент И 12, в результате чего импульсы с выхода формирователя 9 не проходят на выход умножителя, а по заднему фронту импульса на первом входе блок 16 управления вновь разблокирует элемент 12 и в течение очередного пери да умножаемой частоты импульсы с выхода формирователя 9 проходят на выход умножителя. Если текущее значение коэффициента умножения меньше номинального, то импульс на первом входе блока 16 управления появляется раньше чем на втором. При этом по переднему фронту импульса на первом входе блок 16 управления формирует на своем четвертом выходе сигнал, разблокирующий элемент И 13 .3 результате чего импульсы опорной частоты проходят через элементы И 1 и ИЛИ 11 на выход умножителя.. В момент поступления на выход умножителя К-го импульса на второй вход блока 16 управления с выхода формир вателя 15 поступает импульс, по переднему фронту которого блок 16 управления сигналом на своем четвертом выходе блокирует элемент И 13. Таким образом, в течение любого периода умножаемой частоты на выходе умножителя Формируется К импульсов выходной частоты, т.е. обеспечивается постоянство коэффициента умножения умножителя при флуктуации умножаемой частоты. Формула изобретения Умножитель частоты следования импульсов, содержащий делитель опорной частоты, два счетчика импульсов, входной и выходной формирователи импульсов, запоминающий регистр, блок сравнения и блок управления, причем вход устройства соединен с входом входного формирователя импульсов, выход которого подключен к входу блока управления, первый выход которого соединен с первым входом первого счетчика импульсов, второй вход которого соединен с выходом делителя опорной частоты, а выход - с входом запоминающего регистра, выход запоминающего регистра подключен к первому входу блока сравнения, второй вход которого соединен с . выходом второго счетчика импульсов, а выход - с входом выходного формирователя импульсов, первый вход второго счетчика импульсов соединен с первым входом делителя опорной частоты, второй выход блока управления соединен с вторыми входами делителя опорной частоты и запоминающего регистра, о.тли чающийся тем, что, с целью обеспечения постоянства значения коэффициента умножения умножителя при Флуктуации умножаемой частоты, в него введены вычитающий счетчик импульсов, регистр, два элемента И, два элемента ИЛИ, третий счетчик, импульсов и дополнительный формирователь импульсов, при этом первый вход вычитающего счетчика импульсов соединен с выходом делителя опорной частоты, второй вход - с выходом первого счетчика импульсов, третий вход - с вторым выходом блока управления и первым входом первого элемента ИЛИ, второй вход которого -подключен к выходу выходного формирователя импульсов и первому входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, а выход первого элемента ИЛИ подключен ко втор-рму входу второго счетчика импульсов, третий вход которого соединен с выходом регистра, первый вход которого подключен к выходу вычитающего счетчика импульсов, а второй - к третьему выходу блока управления, второй вход второго элемента ИЛИ подключен к выходу второго элемента И, первый вход которого соединен с первым входом делителя опорной

частоты, а второй - с четвертым выходом блока управления, выход второго элемента ИЛИ подключен к выходу умножителя и к первому входу третьего счетчика импульсов, второй вход которого соединен с выходом входного формирователя импульсов, а выход через дополнительный формирователь импульсов подключен к второму входу блока управления, пятый выход которого соединен с вторым входом первого элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 354546, кл. Н 03 К 5/00, 1968.

2.Авторское свидетельство СССР № 357668, кл. Н 03 К 5/01, 1970.

3.Авторское свидетельство СССР 248003, кл. Н 03 К 5/01, 1961.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1980 |

|

SU945962A1 |

| Умножитель частоты следования периодических импульсов | 1976 |

|

SU540363A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Умножитель частоты следования импульсов | 1979 |

|

SU809526A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1972 |

|

SU425315A1 |

| Умножитель частоты | 1976 |

|

SU660228A1 |

уми.

ffX

Авторы

Даты

1981-06-15—Публикация

1979-09-18—Подача