1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для умножения частоты следования импульсов периоди ческих сигналов.

Известен дискретный умножитель частоты, содержащий формирователь импульсов, блок управления,делитель частоты, генератор опорной частоты, ключ, блок коррекции, выполненный на счетчике, одновибраторе и элементах И, и блок умножения, выполненный на счетчиках, регистре памяти и элементах И и ИЛИ 1.

Недостаток устройства - понит-. .. женная точность умножения частоты следования импульсов.

Наиболее близким к предлагаемому является дискретный умножитель частоты, содержащий коммутатор, сигнальный вход которого соединен с шиной опорной частоты, первый управляющий вход подключен через первый формирователь импульсо-в к входу умножителей частоты, а первый выход соединен с входом блока управления, подключенного первымвыходом ко входам обнуления двух регистров памяти, вторым выходом - к первым входам элементов i- первой и второй группы.

а третьим выходом - к установочным входам первого счетчика и делителя частоты и второму/ управляющему входу коммутатора, соединенного вторым 5 выходом со счетным входом делителя частоты, кодовый выход которого подключен ко BTopoNfi входу элементов И первой группы, соединенных выходом с информационным входом первого регистра памяти, подключенного выходами разрядов к соответствующим управляющим входам цифроуправляемой линии задерлски, а кодовый выход первого счетчика, соединенного счетным

15 входом с выходом переполнения делителя частоты, подключен ко второму входу элементов И второй группы, соединенной выходом с инд)Ормационным входом второго регистра памяти, выход

20 которого подключен к первому входу элементов И третьей группы, соединенных вторым входом через второй формирователь импульсов с выходом второго счетчика, подключенного кодовым

25 входом к выходу элементов М третьей группы, причем сигнальный вход цифроуправляемой линии задержки,соединенной выходом с выходом устройства, подключен к выходу второго формиро30 вателя импульсов, а счетный вхоД

второго счетчика соединен с шиной опорной частоты. Цифроуправляемая линия задержки в прототипе выполнена на п (где п - число разрядов управляющего кода) параллельно соединенных цепях, каждая из которых«содержит элемент И и элемент задержки„ Выходы цепей соединены с входами выходного элемента ИЛИ, а управляюшл входы элементов И подключены к выходам дешифратора. Коммутатор выполнен на триггере и двух элементах И 2 .

Недостаток устройства - пониженная точност.ь умножения частоты следования Импульсов периодических сигналов на постоянный коэффициент.

Цель изобретения - повышение точности умножения. ..

С этой целью в дискретный умножитель частоты, содержащий коммутатор, сигнальный вход которого соединен с шиной опорной частоты,первый управляющий -вход подключен через первый формирователь импульсов ко входу умножаемой частоты, а первый выход соединен с входом блокс управления,.подключенного первым выходом ко входам обнуления двух регистров памяти, вторым выходом - к первым входам элементов И, первой и второй групп, а третьим выходом - :;к установочным входам первого счетчика и делителя частоты и второму управляющему входу коммутатора, соединенного вторым выходом со счетным . входом делителя частоты, кодовый выход которого подключен ко второму входу элементов И первой группы, соединенных выходом с информационным входом первого регистра памяти,подключенного выходами разрядов к соответствующим управляющим входам цифроуправляемой линии задержки, а кодовый выход первого счетчика, соединенного счетным входом с выходом переполнения делителя частоты,подключен ко второму входу элементов И второй группы, соединенной выходом с ин(1юрмационным входом второго регастра памяти, выход которого подключен к первому входу элементов И третьей группы, соединенных вторым входом через второй формирователь импульсов с выходом второго счетчика,подключенного кодовым входом к выходу элементов И третьей группы, дополнительно введены коммутатор, элемен задержки, элемент ИЛИ и выходной формирователь, подключенный входом к первому входу элемента ИЛИ,пер)зому управляющему входу дополнительного коммутатора и выходу цифроуправляемой линии задержки, соединенной сигнальным входом с первым выходом дополнительного коммутатора, второй выход которого подключен к c4eTHOtiy входу второго счетчика и второму входу элемента ИЛИ, соединенного

третьим входом с шиной запуска и подключенного выходом через элемент задержки к сигнальному входу дополнительного коммутатора,второй управляющий вход которого соединен с выходом второго фopг шpoвaтeля импульсов.

Кроме того, Цифроуправляемая линия задержки содержит п элементов задержки, п элементов ИЛИ и две группы по п элементов И (где п - число разрядов управляющего кода), причем выход каждого i-ro элемента ИЛИ (l$i:Sn), соединенного первым входом с вы-ходом i-ro элемента И первой группы и подключенного вторым входом через элемент задержки к выходу i-ro элемента И второй группы, соединен с первыми входами (i+l)-x элементов И первой и второй группы, подключенных вторыми входами к управляюии м входам цифроуправляемой линии задержки, причем первые входы первого и второго элементов И обеих групп соединены с сигнальным входом цифроуправляемой линии задержки, а выход п-го элемента ИЛИ подключен к выходу цифроуправляемой линии задержки.

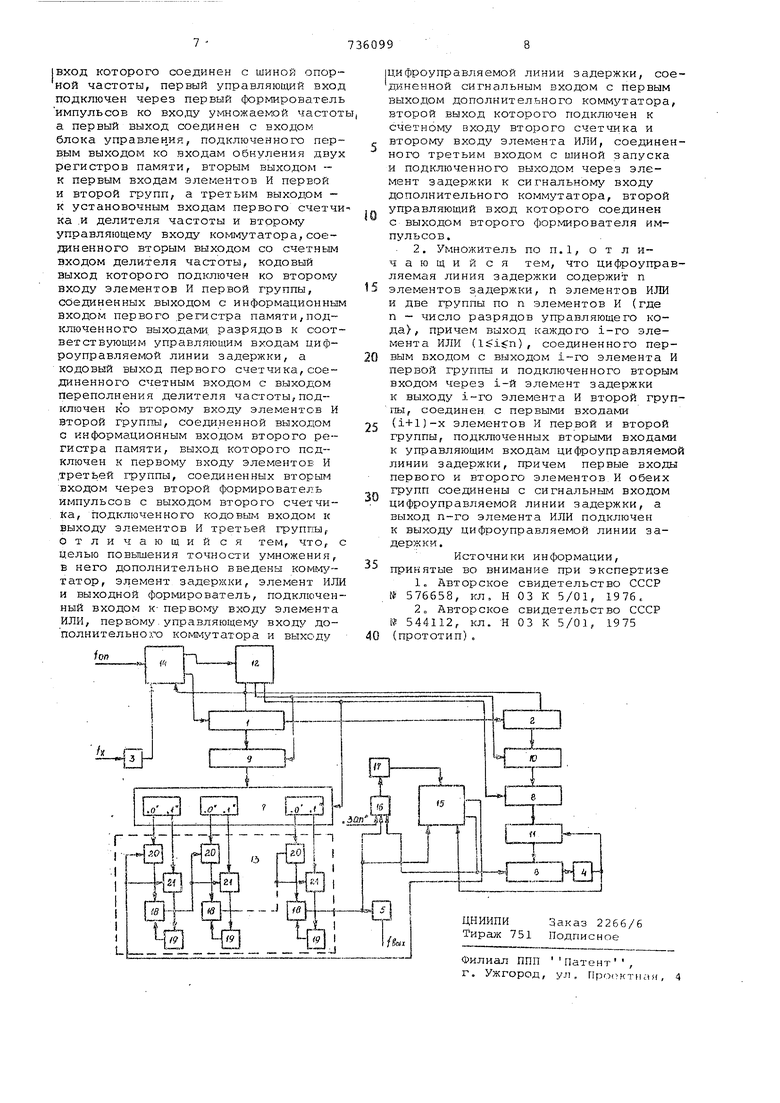

На чертеже изображена блок-схема дискретного умножителя частоты.

Устройство содержит делитель 1 частоты, коэффициент деления которого равен коэффициенту умножения К устройства, первый счетчик 2, первый 3 и второй 4 формирователи импульсов, выходной формирователь 5, второй счетчик 6, первый 7 и второй 8 регистры памяти, первую 9, вторую 10 и третью 11 группы элементов И, блок 12 управления, цифроуправляеглую линию 13 задержки, основной 14 и дополнительный 15 рсоммутатор, элемент 16 ИЛИ, элемент 17 задержки,

Цифроуправляемая линия 13 задержки содержит элементы 18 ИЛИ,элементы 19 задержки, элементы 20 И первой группы и элементы 21 И второй группы

Устройство работает следующим образом.

Каждый входной импульс умножаемо частоты f. через первый формирователь 3 поступает на первый управляюи№1й вход коммутатора 14 и переключает его в такое состояние, при котором импульсы опорной частоты СП) поступающие на сигнальный вход коммутатора, проходят только через его Первый выход на вход блока 12 управления. За время поступления в блок 12 импульсов fon в этом блоке вырабатываются последовательно три сигнёша, первый из которых обнуляет регистры 7 и 8, второй сигнал, снимаемый со второго выхода блока 12, поступает на первые входы групп элементов И 9 и 10, осуществляя пернос прямого кода из делителя 1 частоты в регистр 7 памяти и перенос

обратного кода из счетчика 2 в регистр 8 памяти. Третий .сигнал, снимаемый с третьего выхода блока 12 устанавливает в счетчике 2 все разряды (кроме младшего) в единичное состояние и записывает в делитель 1 частоты число, равное количеству импульсов частоты ,-прошедших на вход блока 12. Одновременно третьим сигналом коммутатор 14 по второму управляющему входу устанавливается в такое состояние, при котором импульсы частоты проходят только через его второй выход на вход делителя 1 частоты.

Импульсы с выхода делителя 1, частота следования которых равна fpp /К, поступают на счетный вход счетчика 2. За один период Tj следования умножаемой частоты на вход счетчика 2 поступает число импульсов, равное

N - ,

где m - число импульсов частоты

fon)оставшихся в делителе 1 к концу периода Т() Тдг, - период следования импульсов частоты.

Однако из-за установки в счетчике 2 предварительного кода в нем фиксируется число, равное NX 2. Это число после поступления очередного импульса частоты f% сигналом со второго выхода блока 12 переносится в обратном коде в регистр 8 (т.е. в регистре памяти 8 устанавливается дополнительный код числа ). Одновременно этим же сигнало с блока 12 из делителя 1 частоты остаток от делителя m переносится в регистр 7 памяти.

Процесс умножения начинается с момента подачи импульса пуск по шине запуска устройства. Этот импульс (соответствующие связи на блосхеме не. показаны) отпирает группу элементов 11 И, в результате чего дополнительный код числа считывается из регистра 8 в счетчик 6. Этот же импульс пуск через элемент 16 ИЛИ поступает на вход элемента 17 задержки, имеющег-о время задержки, равное Тдр. На выходе ЭЛемента 17 возникает последовательнос импульсов с частотой следования (эти импульсы поступают со второго выхода дополнительного коммутатора 15 на счетный вход счетчика 6 и второй вход элемента 16 ИЛИ), При поступленйГи импульсов на выход счетчика 6 появится сигнал переполнения, который через формирователь 4 поступает на второй вход группы элементов 11 И, осуществляя повторную перепись дополнительного кода из регистра 8 в счетчик 6. Этот же сигнал с выхода фop o poвaтeля 4 поступает на второй управляющий вход

коммутатора 15, переключая его в такое положение, при котором импульсы, поступающие с выхода элемента 17 задержки на сигнальный вход этого коммутатора, проходят только на его первый выход, т.е. появившийся ,на выходе элемента задержки импульс пройдет с первого выхода коммутатора 15 на сигнальный вход цифроуправляемой лини№- 13 задержки.

В зависимости от состояния разря0дов регистра 7 памяти (прямые и инверсные выходы которых соединены с управляющим входами линии 13 задержки) импульс будет поступать последовательно на входы эле5ментов 16 ИЛИ либочерез 1соответсавующие элементы 20 через соответствующие элементы 21 И и элементы 19 задержки.

Время задержки t в линии 13 опре0деляется соотношением

-|рл,

где р - разрядная цифра управляющего кода, принимающая знаО

чение

или

5

t - - время задержки, соответствующее весу разряда.

Минимальная величина задержки элементов 19 выбирается равной и соответствует единичному состоя0нию младшего разряда регистра 7

(далее -Ьй.

и т.д).

Таким образом, если остаточное число в делителе 1 равно т, то импульс на выходе линии 13 относительно ее сигнального входа появится

С задержкой -- Этот импульс переключает по первому управляющему, входу коммутатор 15 в исходное состояние (при котором импульсы проходят только на второй выход этого коммутатора) и проходит через элемент 16 ИЛИ на вход элемента 17 задержки,дальнейшая работа устройства происходит аналогично описанному выше.

Период повторения.импульсов на выходе выходного формирователя 5 равен

Т н Т -- To tv Iaa-Ik

выУ. %оп к КТ„„ К. к

on

или

ъь.- Предлагаемое устройство позволяет повысить точность умножения за счет

5 уменьшения погрешности от неравномерности следования импульсов выходной последовательности до возможного для дискретных умножителей предела. Эта погрешность рэвна 1 - при ус0ловии, что погрешность заполнения делителя 1 составляет ± один импульс опорной частоты.

Формула изобретения

1. Дискретный умножитель частоты , содержащий коммутатор, сигнальньлй

(вход которого соединен с шиной опорной частоты, первый управляющий вход подключен через первый формирователь импульсов ко входу уг иожаемой частот а первый выход соединен с входом блока управлен ия, подключенного первым выходом ко входам обнуления двух регистров памяти, вторым выходом - к первым входам элементов И первой и второй групп, а третьим выходом - к установочным входам первого счетчика .и делителя частоты и второму управляющему входу коммутатора,соединенного вторым выходом со счетным входом делителя частоты, кодовый выход которого подключен ко второму входу элементов И первой группы, соединенных выходом с информационным входом первого регистра памяти,подключенного выходами разрядов к соответствующим управляющим входам цифроуправляемой линии задержки, а кодовый выход первого счетчика,соединенного счетным входом с выходом переполнения делителя частоты,подключен ко второму входу элементов И второй группы, соединенной выходом с информационным входом второго регистра памяти, выход которого подключен к первому входу элементов И третьей группы, соединенных вторым входом через второй формирователь импульсов с выходом второго счетчика, подключенного ко ДОВЕЕМ входом к выходу элементов И третьей группы,, отличающий ся тем, что, с целью повышения точности умножения, В него дополнительно введены комм5 татор, элемент задержки, элемент ИЛИ и выходной формирователь, подключенный входом к- первому входу элемента ИЛИ, первому - управляющему входу дополнительного коммутатора и выходу

ion

г

цифроуправляемой линии задержки, соед лнeннoй сигнальным входом с первым выходом дополнительного коммутатора, второй выход которого подключен к счетному входу второго счетчика и второму входу элемента ИЛИ, соединенного третьим входом с шиной запуска и подключенного выходом через элемент задержки к сигнальному входу дополнительного коммутатора, второй управляющий вход которого соединен с выходом второго формирователя импульсов.

2. Умножитель по п.1, о т л ичающийся тем, что цифроуправляемая линия задержки содержит п элементов задержки, п элементов ИЛИ и две группы по п элементов И (где п - число разрядов управляющего кода), причем выход каждого 1-го элемента ИЛИ (), соединенного первым входом с выходом i-ro элемента И первой группы и подключенного вторым входом через i-й элемент задержки к выходу элемента И второй группы, соединен, с первыми входами (i+l)-x элементов И первой и второй группы, подключенных вторыми входами к управляющим входам цифроуправляемо линии задержки, причем первые входы первого и второго элементов И обеих групп соединены с сигнальным входом цифроуправляемой линии задержки, а выход элемента ИЛИ подключен к выходу цифроуправляемой линии задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 576658, кл. Н 03 К 5/01, 1976.

2„ Авторское свидетельство СССР № 544112, кл. Н 03 К 5/01, 1975 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Следящий умножитель частоты | 1979 |

|

SU840892A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2025895C1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Умножитель частоты | 1980 |

|

SU945948A1 |

Авторы

Даты

1980-05-25—Публикация

1977-12-08—Подача