(54) .иИФРСеОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

1

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам кусочно-линейной аппроксимации, и может быть использовано в гибридных вычислительных системах.

Известно устройство для функционального преобразования цифровых сигналов, содержащее реверсивный счетчик, регистр, дешифратор, блок памяти, генератор, элемент И, управляемый делитель частоты и блок вычитания LlJ

Недостатками устройства являются пониженные точность и надежность работы,

Наиболее близким к предлагаемому является устройство для функционального преобразования цифровых сигналов, содер жащее реверсивный счетчик, выходы которого являются выходами устройства, и регистр, соединенный информационными входами с шиной ввода аргумента, а выходами - с входами дешифратора, подключенного выходами через блок памяти к первой группе входов блока вычитания кодов, выход обнуления которого соединен

с первым входом элемента И, подключенного вторым входом к выходу генератора импульсов, а выходом - к сигнальному входу управляемого делителя частоты, блок вьиитания кодов соединен второй группой входов с выходами реверсивного счетчика, выходами кода разности - с управляющими входами управляемого делителя частоты, выходом знака разности - с выходом управления реверсом реверсив10ного счетчика, а выходом обнуления - с управляющим входом регистра и с входом стробирования управляемого делителя частоты, подключенного выходом к счетному входу реверсивного счетчика 2 ..

ts

Недостатком известного устройства 5шляется необходимость ограничения крутизны входного сигнала, обусловленная тем, что при превьпиении определенной крутизны входного сигнала происходит не линейная интерполяция, соответствующая выбранному i -му интервалу аппроксимации, а линейная, соответствующая разности между значениями кодов, соответствую-

. ших -i-и по состоянию реверсивного счетчика и ( 1 + К.)-н по значению из блокапамяти точек (причем К 71).

Целью изобретения является расшире низ класса решаемых задач за счет воз- $ можности воспроизведения функциональных зависимостей с произвольной крутизной.

Поставленная цель достигается тем, что в цифровой функциональный преобразователь, содержащий генератор импульсов,/о элемент И, управляемый делитель частоты, реверсивный счетчик, блок вычитания, блок памяти, входной регистр и дешифратор, вход которого соединен с выходом вход- ного регистра, информационный вход кото- (5

рого соединен с входом аргумента преобразователя, управляющий вход входного регистра соединен с выходом обнуления блока вычитания, первым входом элемента И и входом стробирования управляемог делителя частоты, управляющий вход которого соединен с кодовым выходом блока вычитания, информацио11ный вход и выход которого соединены соответственно с выходом элемента И и счетным входом ре- версивного счетчика, выход которого соединен с выходом преобразователя и первы входом блока вычитания, выход генератора импульсовСоединен с вторым .входом элемента И, выход знака блока вычитания соединен с входом управления реверсом реверсивного счетчика, дополнительно введены три промежуточных регистра, группа элементов И, группа элементов ИЛИ, груп па формирователей импульсов, элемент ИЛИ, элемент задержки, элемент НЕ и сумматор, первый вход которого соединен с выходом дешифратора и первыми входами элементов И группы, вторые входы которых подключены к выходу элементаНЕ и управляющему входу первого промежуточного регистра, информагшонный вход которого соединен с выходом блока памяти и информационным входом второго промежуточного регистра, выход и управляющий, вход которого соединены соответственно с установочным входом реверсивного счетчика к выходом элемента задержки, вход которого соединен с выходом элемента ИЛИ и вторым входом сумматора, входы элемента ИЛИ соединены с выхо- дами формирователей группы, входы которых соединены с выходом разрядов, начиная со второго, входного регистра, выход элемента задержки соединен с входом элемента НЕ и управляющим входом третьего 5памяти и счетчика 1. Передний фронт сигпромежуточного регистра, информационныйнала сравнения с выхода 1О обнуления вход и выход которого соединены соот-блока 8 поступает на управляющий вход ветственно с выходом сумматора и пер-регистра 2, разрешая передачу кода елевыми входами элементов ИЛИ группы, вторые входы и выходы которых соединены соответственно с выходами элементов И группы и входом блока памяти, выход первого промежуточного регистра соединен с вторым бходом блока вычитания.

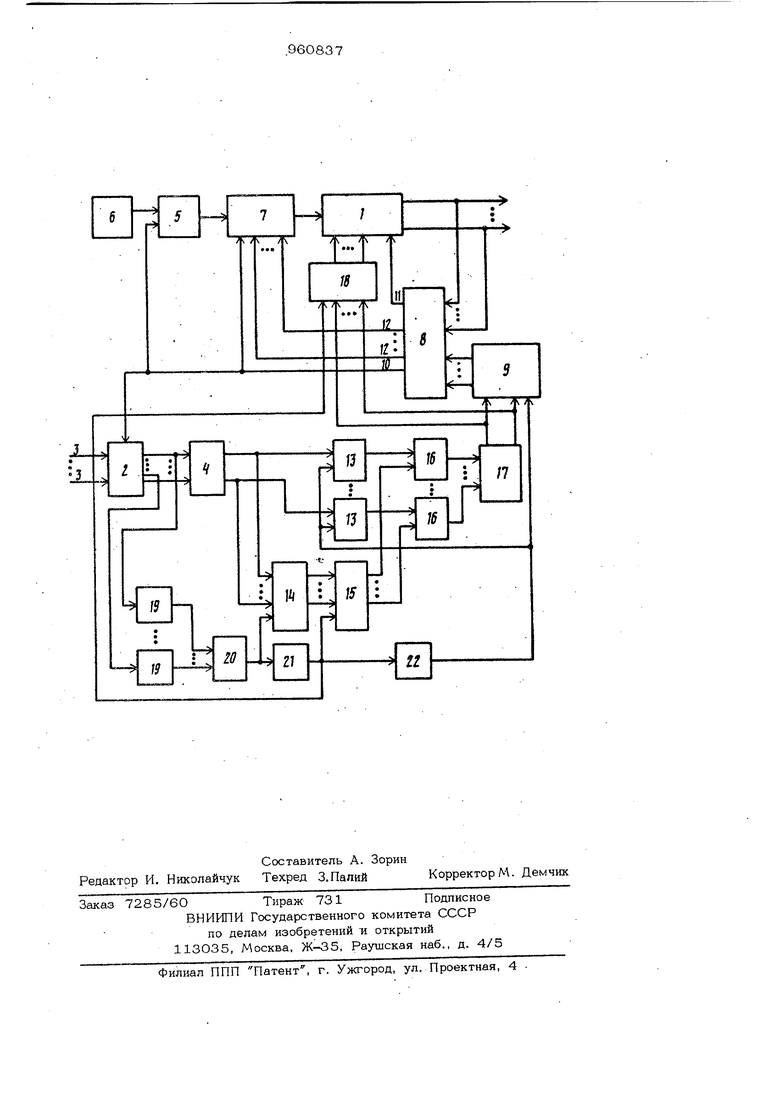

На чертеже представлена блок-схема цифрового функционального преобразователя.

Устройство содержит реверсивный счетчик 1, входной регистр 2, информационный вход 3 входного регистра 2, дешифратор 4, элемент И 5, генератор 6 импульсоц, управляемый делитель 7 часрегистр 9, выход 10 обнуления блока 8 вычитания, выход 11 знака разноста блока 8 вычитания, кодовый выход 12 блока 8 вычитания, группу элементов И 13, тоты, блок 8 вычитания, промежуточный сумматор 14, промежуточный регистр 15, Группу элементов ИЛИ 16, блок 17 памяти, промежуточный регистр 18, группу формирователей 19 импульсов, элемент ИЛИ 2О, элемент 21 задеряжи и элемент НЕ 22. Устройство работает следующим образом. В блок 17 памяти заносятся ординаты узловых точек функции преобразования f(Xi), причем в первую ячейку заносится нулевой код f (УО) ° вторую (Х-|)и т.д. Значения .кодов аргумента, поступающие на входной регистр 2, преобразуются дешифратором 4 в код адреса, по которому в блоке 17 памяти находится код соответствующего значения функции преобразования. С помощью блока 8 вычитания и де;штеля 7 частоты автоматически устанавливается коэффициент наклона аппроксимирующих отрезков. Группа формирователей 19 соединена с ( N - 1) выходами старших разрядов входного регистра 2 и предназначена для образования одиночных импульсов положительной полярности при изменении кода в любом разряде. В исходном состоянии реверсивный счетчик i и регистры 2, 9, 15 и 18 установлены в ноль, и нулевой код с выхода регистра 2 поступает на входы дешифратора 4. Таким образом, нулевой код из первой ячейки блока 17 памяти поступает через регистр 9 на вход блока 8 вычитания, который вырабатывает разность кодов поступающих с выхода блока 17 дующего значения аргумента из регистра на дешифратор 4, на первый вход элемента И 5, закрывая его на время установки коэффициента деления, на вход стробирования делителя. 7 частоты, разрешая уста- новку коэффициента. При малой крутизне входного сигнала на первом участке на выходах регистра 2 изменится только код младшего разряда, и формирователи 19 не выработают импульса положительной полярности. В результате регистры 15 и 18 заблокированы сигналом низкого уровня, а на управляющий вход регистра 9 и входы группы элементов И 13 с выхода элемента НЕ 22 поступает разрешающий сигнал высокого уровня. Дешифратор 4 осуществляет вЬтборку адреса соответствующего значения функции f(У), которое поступает из блока 17 памяти через регистр 9 на вхо- ды блока 8, формирующего разность кодой (Х-) и f (Хо). поступающую на управляющие входы делителя 7 частоты, в котором устанавливается соответствующий коэффициент деления. После поступления на вход блока 8 кода.значения функции f (Xi на выходе 10 блока 8 вырабатывается задний фронт сигнала сравнения, задержан ный на время, необходимое для установ ки коэффициента деления делителя 7 час- тоты. По заднему фронту сигнала сравнения открывается элемент И 5, и импульсы с выхода генератора 6 поступают на счетный вход реверсивного счетчика 1. Таким образом, происходит линейная интерполяция функции на выбранном интервале аппр ксим.ации, причем частота импульсов с вы хода генератора 6, поступающая на счетчик 1, определяется коэффициентом деления делителя 7. Выходной код счетчика 1 при необходимости может быть преобразован в аналоговый сигнал соответствую щим цифро-аналоговым преобразователем. При совпадении кода счетчика 1 и ко- да (Х-1)на выходе 10 обнуления блока 8 фор 5ируется очередной импульсный сигнал по .которому элемент И 5 закрывается, и Бьщается разрешение на передачу из регистра 2 в дешифратор 4 кода следующег значения аргумента. При больщой крутизне входного сигнала, т. е. при переходе с 1 -го участка аппроксимации к (i + К)-му (причем поступившее на входы регистра 2 nepBOie значение аргумента через дешифратор 4по разрешающему высокому уровню на вторых входах группы элементов И 13 осуществляет выборку адреса, соответствующего значению функции {(.Л которое поступает из блока 17 памяти через регистр 9 на вход блока 8. Кроме .того, на К выходах регистра 2 прбисходит изменение кода, что приводит к появлению одиночных импульсов на выходах группы формирователей 19, и на выходе первого элемента ИЛИ 20 появляется импупьс положительной полярности. По данному импульсу в сумматоре 14 из кода адреса, поступающего с выхода дешифратора 4, вычитается единица младшего разряда и, таким образом, формируется адрес, соот ветствующий значению функции )По задержанному на время, необходимое для передачи кода()из блока Д7 памяти в блок 8, линией 21 задержки положительному импульсу разрешается передача адреса, соответствующего значению функции с сумматора 14, через регистр 15 в блок 17 памяти и запись кода {Х-.,. JH3 блока 17 через регистр 18 в счетчик 1. Таким образом, в блоке 8 формируется разность КОДОВ (.) и ..), поступающая на управляющие входы делителя 7 и устанавливающая коэффициент деления на данном участке аппроксимации. По заднему фронту сигнала сравнения с выхода 10 блока 8 элемент И 5 открывается, и начинается линейная интерполяция данного участка функции. На последующих участках аппроксимации устройство работает аналогично. При изменении знака крутизны функции в узловых точках разность кодов {( ( изменяет знак, и признак знака крутизны с выхода 11 блока 8 управляет рёверюом счетчика 1. Таким образом, предложенное устройство по сравнению с известным позволяет расширить класс решаемых задач за счет преобразования функций, начинающихся не с нуля, и функций с произвольной крутизной. Формула изобретения Цифровой функциональный преобразователь, содержащий генератор импульов, элемент И, управляемый делитель частоты, реверсивный счетчик, блок вычитания, .блок памяти, входной регистр и дешифратор, вход которого соединен с выходом входного регистра, информационный вход которого соединен с входом аргумента преобразователя управляющий вход входного регистра соединен с выходом обнуления блока вычитания, первым входом элемента И и входом стробирования управляемого делителя частоты, управляющий вход которого соединен с кодовым выходом блока вычитания, информационный вход и выход которого соединены соответственно с выходом элемента И и счетным входом реверсивного счетчика, выход которого соединен с выходом преобразователя и первым входом блока вы-- 10 с

читания, выход генератора импульсов соединен с вторым входом элемента И, выход знака блока вычитания соединен с входом управления реверсом реверсивного счетчика, отличающийся тем, is что, с целью расширения класса решаемых задач за счет возможности воспроизведения фушсциональных зависимостей с произвольной крутизной, в него введены три проме куточных регистра, группа элемен- JQ

тов И, группа элементов ИЛИ, группа формирователей импульсов, элемент ИЛИ, элемент задержки, элемент НЕ и сумматор, первый вход которого соединен с выходом дешифратора и первыми входами элементов 15 И группы, вторые входы которых .подключены к выходу элемента НЕ и управляющему входу первого промежуточного регистра, информахшонный вход которого соединен с выходом блока памяти и информационным входом второго промежуточного регистра, выход и управляющий вход которого соединены соответственно с установочным входом реверсивного счетчика и выходом элемента задержки, вход которого соединен с выходом элемента ИЛИ и вторым входом сумматора, входы элемента ИЛИ соединены с выходами формирователей группы, входы которых соединены

входного регистра, выход элемента задержки соединен с входом элемента НЕ и управляющим входом третьего промежуточного регистра, информационный вход и выход которого соединены соответственно с выходомсумматора и первыми входами элементов ИЛИ группы, вторые входы и выходы которых соединены соответственно с выходами элементов И группы и входом

ного регистра соединен

с вторым входом блока вычитания.

Источники информа1ши, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №684552, кл. G06 F 15/31, 1977.

2.Авторское свидетельство СССР по заявке № 2855014/18-24,

кл. Q06 F 15/31, 18.12.79 (прототип). выходом разрядов, начиная со второго. блока памяти, выход первого промежуточ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Устройство для функционального преобразования цифровых сигналов | 1979 |

|

SU864293A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Устройство для аппроксимации функций | 1980 |

|

SU934481A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

Авторы

Даты

1982-09-23—Публикация

1981-02-18—Подача